YD/T 821-1996

基本信息

标准号: YD/T 821-1996

中文名称:数字传输性能测量的数字图形

标准类别:通信行业标准(YD)

标准状态:现行

出版语种:简体中文

下载格式:.zip .pdf

下载大小:454608

标准分类号

关联标准

出版信息

相关单位信息

标准简介

YD/T 821-1996.

1范围

YD/T 821规定了标准的和成帧的测试序列,以及在PDH和SDH系统上,差错性能测量的块长。

YD/T 821是工作在各类比特率的数字传输系统,及其复用/分用器以及开业务监测的差锖性能测量及测量设备的技术设计和制造的依据。

2标准的测试序列

标准测试序列是在某-规定的数字速率上,对数字传输设备或点对点的数字通道进行差错性能评价时,必需采用的测试序列。

比特差错测量,对评价数字传输设备的性能是一种重要的手段。只有测量序列的比特序列是完全已知时,才能进行所谓的“真”比特差错的测量,这时应能检出每个比特差错。而实际的业务申于其随机性质,通常不能满足上述条件。

所以,有必要规定可再现的,尽可能接近模拟实际业务的测试序列。可再现的测试序列也是完成点到点测量的先决条件。

具有2n-1长度的伪随机序列是此向题最普通的解答。除了n个连续0(所谓的反转信号)和n-1个连续1的字符串以外,在取决于n的字符串长度内,该序列包含任意可能0和1的组合。

(有关n的值,见第3章)

本标准规定了不同长度的伪随机序列。

3伪随机测试序列的应用

测试序列的特性应符合所测试系统的要求。通常,伪随机序列的长度应随被测量的比特率增加而增加。这样可以避免序列的重复频率太高,而与实践中遇到的状态不一致。

伪随机序列的产生,可借助于具有适当反馈的移位寄存器。如果该移位寄存器有n级,则最大的序列长度将是2n-1比特。

如果数字信号直接地从移位寄存器的输出(非反转信号)取出,则最长的连0字符个数将等于n- 1。如果该信号被反转,将产生n个连0字符。

1范围

YD/T 821规定了标准的和成帧的测试序列,以及在PDH和SDH系统上,差错性能测量的块长。

YD/T 821是工作在各类比特率的数字传输系统,及其复用/分用器以及开业务监测的差锖性能测量及测量设备的技术设计和制造的依据。

2标准的测试序列

标准测试序列是在某-规定的数字速率上,对数字传输设备或点对点的数字通道进行差错性能评价时,必需采用的测试序列。

比特差错测量,对评价数字传输设备的性能是一种重要的手段。只有测量序列的比特序列是完全已知时,才能进行所谓的“真”比特差错的测量,这时应能检出每个比特差错。而实际的业务申于其随机性质,通常不能满足上述条件。

所以,有必要规定可再现的,尽可能接近模拟实际业务的测试序列。可再现的测试序列也是完成点到点测量的先决条件。

具有2n-1长度的伪随机序列是此向题最普通的解答。除了n个连续0(所谓的反转信号)和n-1个连续1的字符串以外,在取决于n的字符串长度内,该序列包含任意可能0和1的组合。

(有关n的值,见第3章)

本标准规定了不同长度的伪随机序列。

3伪随机测试序列的应用

测试序列的特性应符合所测试系统的要求。通常,伪随机序列的长度应随被测量的比特率增加而增加。这样可以避免序列的重复频率太高,而与实践中遇到的状态不一致。

伪随机序列的产生,可借助于具有适当反馈的移位寄存器。如果该移位寄存器有n级,则最大的序列长度将是2n-1比特。

如果数字信号直接地从移位寄存器的输出(非反转信号)取出,则最长的连0字符个数将等于n- 1。如果该信号被反转,将产生n个连0字符。

标准图片预览

标准内容

YD/T821—--1996

本标准是根据ITU-TO.150(1995年修改草案)《数字传输设备性能测量仪表的通用要求》的内容而规定。在技术内容上与该国际建议等效。本标准包括可适用于数字传输设备性能测量仪表的通用信息。结合我国数字通信的PDH和 SDH传输体制,制定工作在14.4kbit/s以下、64kbit/s、N×64kbit/s.2048kbit/s、8448kbit/s34368kbit/s、139264kbit/s和155520kbit/s等比特率上的标准测试序列及其成恢测试序列的要求。本标准还规定了,在PDH和 SDH系统上差错性能测量的块长,作为面向块的差错性能测量,本标推由邮电部电信科学研究规划院提出并归口。本标准由邮电部电信传输研究所起草。本标准主要起草人:翁元举、罗建国。216

1范围

中华人民共和国通信行业标准

数字传输性能测量的数字图形

YD/T 821-1996

本标准规定了标准的和成帧的测试序列,以及在 PDH 和 SDH 系统上,差错性能测量的块长。本标准是工作在各类比特率的数字传输系统,及其复用/分用器以及开业务监测的差错性能测量及测量设备的技术设计和制造的依据。2标准的测试序列

标准测试序列是在某一规定的数字速率上,对数字传输设备或点对点的数字通道进行差错性能评价时,必需采用的测试序列。

比特差错测量,对评价数字传输设备的性能是一种重要的手段。只有测量序列的比特序列是完全已知时,才能进行所谓的“真”比特差错的测量,这时应能检出每个比特差错。而实际的业务曲于其随机性质,通常不能满足上述条件。

所以,有必要规定可再现的,尽可能接近模拟实际业务的测试序列。可再现的测试序列也是完成点到点测量的先决条件。

具有2\一1长度的伪随机序列是此问题最普通的解答。除了n个连续0(所谓的反转信号)和n一1个连续1的字符串以外,在取决于n的字符串长度内,该序列包含任意可能0和1的组合。(有关n的值,见第3章)

本标准规定了不同长度的伪随机序列。3伪随机测试序列的应用“

测试序列的特性应符合所测试系统的要求。通常,伪随机序列的长度应随被测量的比特率增加而增加。这样可以避免序列的重复频率太高,而与实践中遇到的状态不一致。伪随机序列的产生,可借助于具有适当反馈的移位寄存器。如果该移位寄存器有n级,则最大的序列长度将是2\—1比特。

如果数字信号直接地从移位寄存器的输出(非反转信号)取出,则最长的连0字符个数将等于n一1。如果该信号被反转,将产生n个连0字符。除采用移位寄存器以外,还可能有其它的方法产生具有这些特性的伪随机序列3.1·通过扰码器的差错测量

在测试过程中,可能含有扰码器。若第3章所述的n值与扰码器的级数共有整数倍,则可能得出不期望的测量结果。为了减少将产生此问题的可能性,规定了测试序列的n值为一个质数。3.2序列同步的丢失

只有在测试建立的接收侧,其参考序列正确地同步于来自被测对象的序列时,才能完成采用伪随机序列的比特差错的测量。为了获得一致的测量结果,必须规定序列同步的特性。下列要求可适用于,采用伪随机序列处理差错性能测量的全部ITU-TO系列建议。若有下列情况,则应认为序列同步丢失并应启动再同步:中华人民共和国邮电部1996-03-12批准HiiKAoNiKAca

1996-08-01实施

YD/T 821-1996

a)在某一秒的累计时间间隔内,比特差错率≥0.20,或b)能够明确地证实测试序列和参考序列不同相。3.3“成”的测量

成顿测试序列是在不相等的输入和输出的数字速率上,进行差错性能评价时,必需采用的测试序列,例如复用/分用器的差错性能评价。并且该成结构也用于不中断通信业务的开业务(In-Service)监测。面向块的差错性能测量的块长,适用于PDH和SDH系统的测量。某些测量要求测试序列在有效的帧内按净荷传送测试序列。在这种情况下,当传送顿定位信号时,将停止测试序列的传送。

详细内容在本标准的第5章中给出。3.4抖动测试

数字测试序列不仅用于差错的测量,而且也可用于测量抖动转移函数、可容许的输入抖动及输出抖动。数字线路系统和数字线路段的抖动测量应使用较长的伪随机测试序列。这种情况,对用于测量抖动的测试序列的长度应给以特别的注意,如果该序列太短(高的序列重复颊率),则测试信号的频谱分布可能实质上与实际业务性能不同。在此情况下,该测量结果将不反映实际状态。根据实贱经验,通常可用一个适当的修正系数(1.5或1.3),以修正具有随机性的实际业务和伪随机测试序列进行测量的差别。见G.823建议讨论此问题的附录A1。对于复用设备的抖动转移函数的测试,应使用本标准4.7中给出的测试序列。4数字测试序列

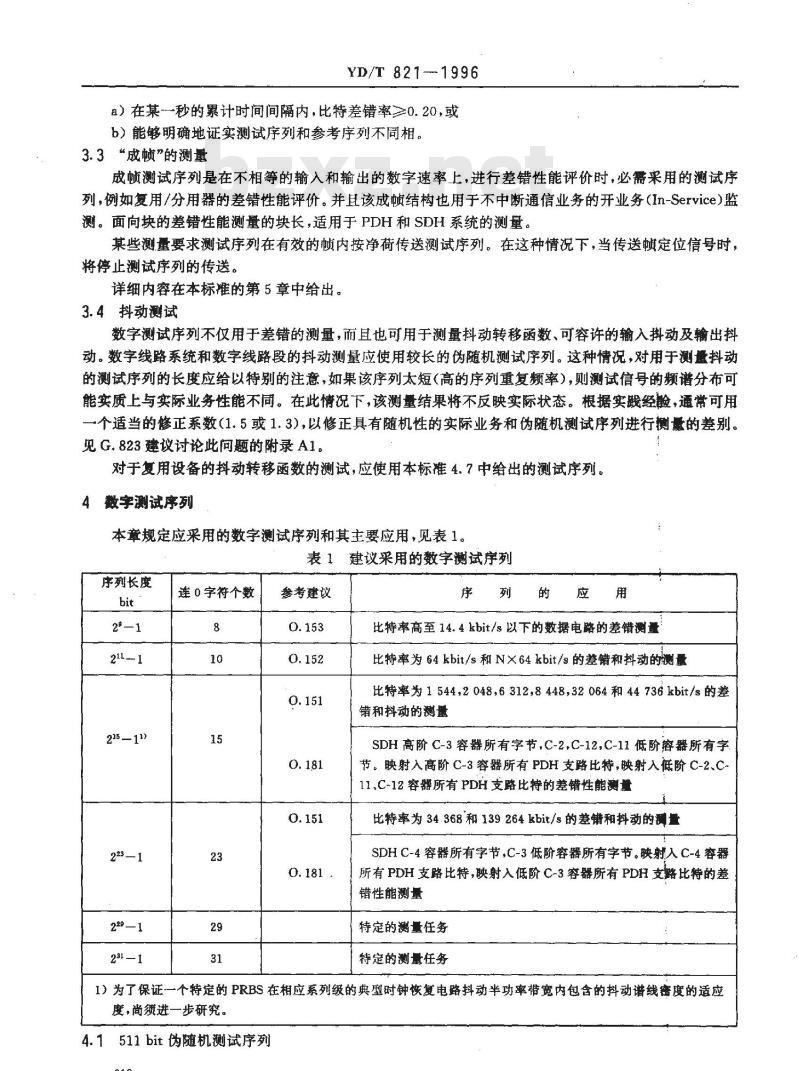

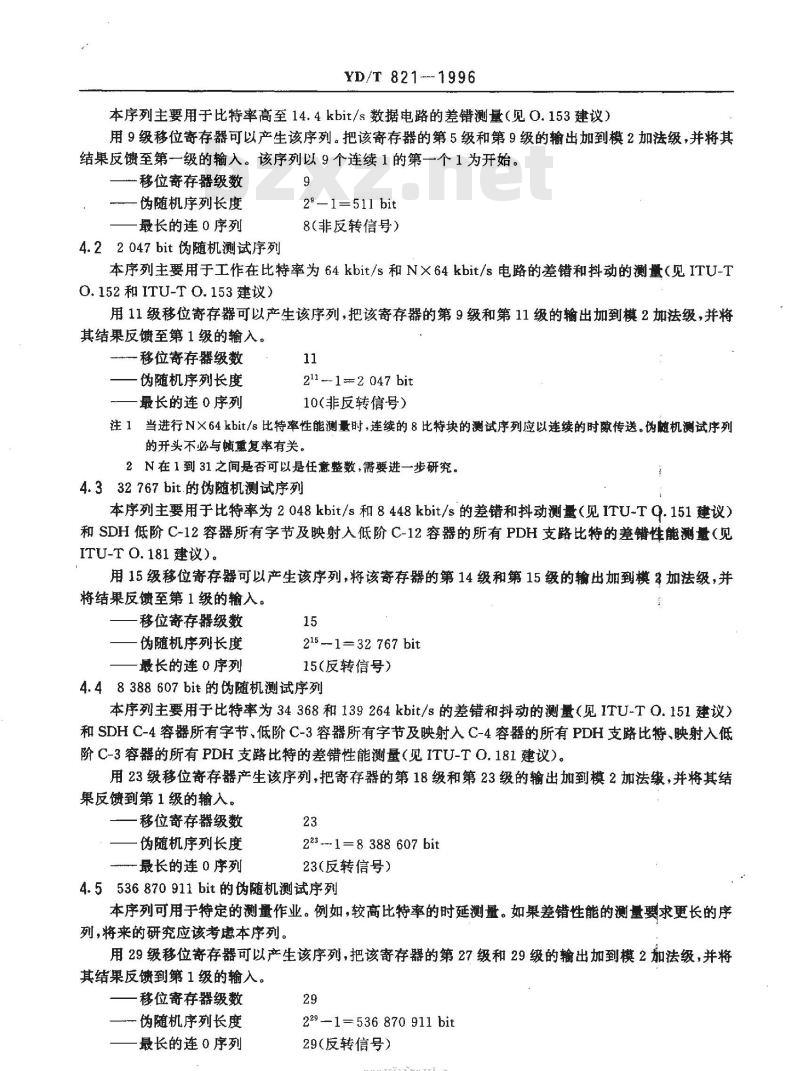

本章规定应采用的数字测试序列和其主要应用,见表1。表1建议采用的数字测试序列

序列长度

2°—1

213—11)

223—1

231—1

连0字符个数

参考建议

序列的应用

比特率高至14.4kbit /s以下的数据电路的差错测量比特率为 64 kbit/s 和 N X 64 kbit /s 的差错和抖动的测量比特率为1544,2048,6312,8448,32064和44736kbit/的差错和抖动的测量

SDH高阶C-3容器所有字节,C-2,C-12,C-11低阶溶器所有字节。映射入高阶C-3容器所有PDH支路比特,映射入低阶C-2、C-11,C-12 容器所有 PDH 支路比特的差错性能测量比特率为34.368和139264kbit/s的差错和抖动的测量SDHC-4容器所有字节,C-3低阶容器所有字节。映射入C-4容器所有PDH支路比特,映射入低阶C-3容器所有PDH支璐比特的差错性能测量

特定的测量任务

特定的测量任务

1)为了保证一个特定的PRBS在相应系列级的典型时钟恢复电路抖动半功率带宽内包含的抖动谱线密度的适应度,尚须进一步研究。

4.1511bit伪随机测试序列

YD/T 821---1996

本序列主要用于比特率高至14.4kbit/s数据电路的差错测量(见0.153建议)用9级移位寄存器可以产生该序列。把该寄存器的第5级和第9级的输出加到模2加法级,并将其结果反馈至第一级的输入。该序列以9个连续1的第一个1为开始。移位寄存器级数

伪随机序列长度

最长的连0序列

4.22047bit伪随机测试序列

29—1=511 bit

8(非反转信号)

本序列主要用于工作在比特率为64kbit/s和N×64kbit/s电路的差错和抖动的测量(见ITU-TO.152和ITU-TO.153建议)

用11级移位寄存器可以产生该序列,把该寄存器的第9级和第11级的输出加到棋2加法级,并将其结果反馈至第1级的输入。

移位寄存器级数

一伪随机序列长度

最长的连0序列

211 - 1 2 047 bit

10(非反转信号)

注 1当进行 N X 64 kbit /s 比特率性能测量时,连续的 8 比特块的测试序列应以连续的时隙传送。伪雌机测试序列的开头不必与恢重复率有关。

2 N在 1 到 31 之间是否可以是任意整数,需要进一步研究。4.332767bit的伪随机测试序列

本序列主要用于比特率为2048kbit/s和8448kbit/s的差错和抖动测量(见ITU-TQ.151建议)和SDH低阶C-12容器所有字节及映射入低阶C-12容器的所有PDH支路比特的差错性能测量(见ITU-T O. 181 建议)。

用15级移位寄存器可以产生该序列,将该寄存器的第14级和第15级的输出加到模3加法级,并将结果反馈至第1级的输入。

移位寄存器级数

伪随机序列长度

最长的连0序列

215 --1=32 767 bit

15(反转信号)

4.48388607bit的伪随机测试序列本序列主要用于比特率为34368和139264kbit/s的差错和抖动的测量(见ITU-TO.151建议)和SDHC-4容器所有字节、低阶C-3容器所有字节及映射入C-4容器的所有PDH支路比特、映射入低阶C-3容器的所有PDH支路比特的差错性能测量(见ITU-TO.181建议)。用23级移位寄存器产生该序列,把寄存器的第18级和第23级的输出加到模2加法级,并将其结果反馈到第1级的输入。

移位寄存器级数

伪随机序列长度

最长的连 0 序列

223 -- 1=8 388 607 bit

23(反转信号)

4.5536870911bit的伪随机测试序列本序列可用于特定的测量作业。例如,较高比特率的时延测量。如果差错性能的测量要求更长的序列,将来的研究应该考虑本序列。用29级移位寄存器可以产生该序列,把该寄存器的第27级和29级的输出加到模2加法级,并将其结果反馈到第1级的输入。

移位寄存器级数

伪随机序列长度

最长的连0序列

229 -1= 536 870 911 bit

29(反转信号)

HiKAoNi KAca-

YD/T 821--1996

4.62147483647bit的伪随机测试序列本序列可用于特定的测量作业,例如,较高比特率的时延测量。如果差错性能的测量要求更长的序列,将来的研究应该考虑本序列。用31级移位寄存器可以产生该序列,把寄存器的第28级和第31级的输出加到模2加法级,并且将其结果反馈至第1级的输入。

移位寄存器级数

—伪随机序列长度

—最长的连0序列

231 --1=2 147 483 647 bit

31(反转信号)

4.7用于PDH所有比特率的重复测试序列4.7.1用于所有比特率的10001000测试序列4.7.2作为一种任选的和用于PDH所有比特率方案的测试序列a)能够以低速率(例如10至100Hz)交替改变的两种任意可编程序的8比特测试序列。b)任意可编程序的16比特测试序列。5在不同的比特率上的成顿测试序列5.1概述

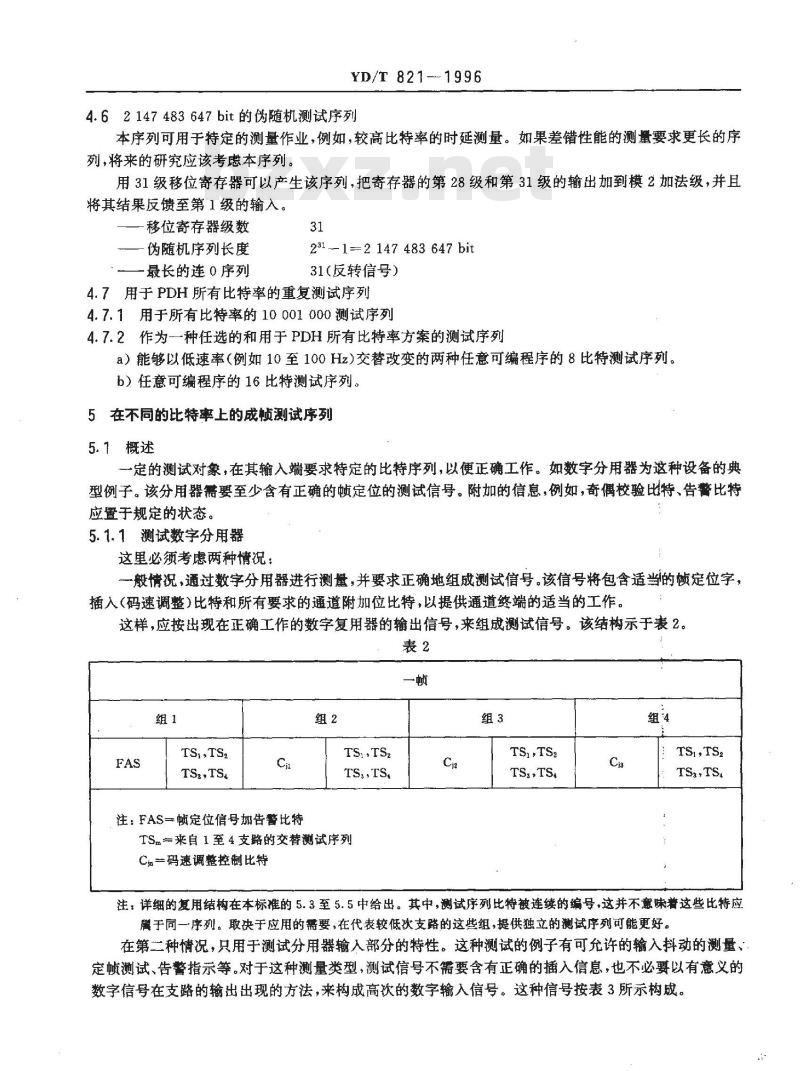

一定的测试对象,在其输入端要求特定的比特序列,以便正确工作。如数字分用器为这种设备的典型例子。该分用器需要至少含有正确的顿定位的测试信号。附加的信息,例如,奇偶校验比特、告警比特应置于规定的状态。

5.1.1测试数字分用器

这里必须考虑两种情况:

一般情况,通过数字分用器进行测量,并要求正确地组成测试信号。该信号将包含适当的恢定位字,插入(码速调整)比特和所有要求的通道附加位比特,以提供通道终端的适当的工作。这样,应按出现在正确工作的数字复用器的输出信号,来组成测试信号。该结构示于表2。表2

TS,TS2

TSs,TS

注:FAS一定位信号加告警比特

TSm一来自 1至 4支路的交替测试序列C一码速调整控制比特

TS,TS4

注,详细的复用结构在本标推的5.3至5.5中给出。其中,测试序列比特被连续的编号,这并不意味着这些比特应篇于同一序列。取决于应用的需要,在代表较低次支路的这些组,提供独立的测试序列可能更好。在第二种情况,只用于测试分用器输入部分的特性。这种测试的例子有可允许的输入抖动的测量、定顿测试、告警指示等。对于这种测量类型,测试信号不需要含有正确的插入信息,也不必要以有意义的数字信号在支路的输出出现的方法,来构成高次的数字输入信号。这种信号按表3所示构成。220

第1帧

TS,到 TSu

第2顿

YD/T 821—1996

第3顿

TSu+到S

注:FAS=顿定位信号加告警比特:TS,到TS,=可能属于一个序列的测试序列比特5.2工作在2048kbit/s比特率的数字顺5.2.1无CRC-4程序并提供公共信道信令的帧在此情况下,该顿结构如表4。

时隙0

1001 1011

11AS SSSS

注:A=远端告警指示

S=备用比特

时隙1~15

测试序列

5.2.2无CRC-4程序并提供随路信令的帧在此情况下,该顿结构如表5。

时隙0

10011011

11AS SSSS

注:A=远端告警指示

S=备用比特

日,b,c,d信令比特

时1~15

测试序列

5.2.3具有CRC-4程序和提供随路信令的恢在此情况下,该顿结构如表 6。

时题0

Co01 1011

C1AS SSSS

时隙1~15

测试序列

注:C循环允余校验比特(CRC-4)A一远端告警指示

S=备用比特

a,b,c.d=信令比特

HiiKAoNiKAca

TS+i到 TS

时隙16

测试序列

时隙16bZxz.net

abed abcd

时隙16

abcd abcd

第n顿

TSx+到 TS,

时隙17~31

测试序列

时隙17~31

测试序列

时隙17~~31

测试序列

YD/T 821--1996

5.3工作在8448kbit/s比特率的数字顿在此情况下,该恢结构如表7。

一顿含有每组为212bit的4个组,并具有848bit的长度。表7

200 bit

详细的组1到组4的结构列于表8:208 bit

附加位(O-)比特

赖定位信号(比特1至10)

1111010000

远端告警指示(比特11)

留待国内使用(比特12)

208 bit

码速调整控制比特:C11,C21,C31.C41码速调整控制比特:C12.C22C32,C42码速调整控制比特:C13.C23,C33,C43来自支路的可用于码速调整的比特(比特5~8)

注:有关插入(码速调整)比特的使用见5.1.1。5.4工作在34368kbit/s比特率的数字顿在此情况下,该恢结构如表9。

一愤包含每组为384bit的4个组,具有1536bit长度。表9

372 bit

组1至组4详细结构如表10。

380 bit

380 bit

208 bit

测试序列比特

1~200

201~408

409616

617~84(820)

380 bit

YD/T 821—1996

附加位(O-)比特

赖定位信号(比特1~10)

1111010000

远端告警指示(比特11)

留待国内使用(比特12)

调整控制比特:C11,C21,C31,C41调整控制比特:C12,C22.C32.C42调整控制比特:C13,C23,C33,C43来自支路可用于码速调整的比特(比特5~8)

5.5工作在139264kbit/s比特率上的数字顿5.5.1工作在139264kbit/s并复接34368kbit/s信号的数字懒在此情况下,该顿结构如表11。个懒包含每组为488bit的6.个组,并具有2928bit的长度。表11

472 bit

组1至组6的详细结构示于表12。组1

组2~~5

484 bit

附加位(O-)比特

赖定位信号(比特1~12)

111110100000

远端告警指示(比特13)

留特国内使用(比特14~16)

组2~5

注:有关播入(调整)比特见5.1.1。调整控制比特:Cln,C2,C3n,C4n调整控制比特:C15,C25,C35,C45来自支路的可用于调整的比特

(比特 5~8)

HiKAoNiKAca

测试序列比特

373~752

753~1 132

1 133~1 512(1 508)

484 bit

测试序列比特

473~2408

2 409~2 892(2 888)

YD/T 821-1996

5.6工作在155520kbit/s比特率上的数字顿5.6.1 SDH 基本复用结构

我国SDH基本复用结构如下:

指针处理

定位校准

图1基本复用映射结构

5.6.2SDH测试信号结构

按G.70X建议,应有正确的开销字节和有效指针的设置。5.6.2.1适用于C-4高阶容器的所有字节的测试信号结构TSS1TU-3

139264kbit/s

34368kbitls

2048kbit/s

为了测试高阶通道连接功能(HPC)和采用AU-4结构的网络单元(NE),测试信号结构TSS1是-~种适用于C-4容器所有字节,其长度按本标准4.4为223-1比特的PRBS(伪随机二进制序列)测试序列。见图2。

图2TSS1测试信号结构

5.6.2.2适用于C-3低阶容器的所有字节的测试信号结构TSS3为了测试提供高阶通道连接功能(HPC)和低阶通道连接功能(LPC)的网络单元(NE),测试信号结构TSS3是一种适用于C-3低阶容器所有字节,其长度按本标准4.4为223一1比特的PRBS(伪随机二进制序列)测试序列。见图3。

YD/T 821-1996

图3TSS3测试信号结构

5.6.2.3适用于C-12低阶容器的所有字节的测试信号结构TSS4为了测试提供高阶通道连接功能(HPC)和低阶通道连接功能(LPC)的网络单元(NE),测试信号结构TSS4是种适用于C-12低阶容器所有字节,其长度按本标准4.3为215一1比特的PRBS(伪随机二进制序列)测试序列。见图4。

图4TSS4测试信号结构

(7 × TUG-2)

5.6.2.4适用于映射入C-4容器的所有PDH支路比特的测试信号结构TSS5为了测试仅提供低阶通道适配功能(LPA-4)和采用AU-4结构的网络单元(NE),测试信号结构TSS5是一种适用于映射入C-4容器所有PDH支路比特,其长度按本标准4.4为223一1比特的PRBS(伪随机二进制序列)测试序列。见图5。HiikAoNikAca

YD/T8211996

图5TSS5测试信号结构

5.6.2.5适用于映射入低阶C-3容器的所有PDH支路比特的测试信号结构TSS7为了测试仅提供低阶通道适配功能(LPA-3)和采用AU-4结构的网络单元(NE),测试信号结构TSS5是种适用于映射入低阶C-3容器所有PDH支路比特,其长度按本标准4.4为231比特的PRBS(伪随机二进制序列)测试序列。见图6。RSOH

图6TSS7测试信号结构

5.6.2.6适用于映射入低阶C-12容器的所有PDH支路比特的测试信号结构TSS8为了测试仅提供低阶通道适配功能(LPA-12)和采用AU-4结构的网络单元(NE),测试信号结构TSS8是一种适用于映射入低阶C-12容器所有PDH支路比特,其长度按本标准4.3为25一1比特的PRBS(伪随机二进制序列)测试序列。见图7。226

6面向块的差错性能测量

6.1块差错量

YD/T 821—1996

(7 × TUG-2)

图 7TSS8测试信号结构

G.826建议规定了工作在一次群速率或一次群速率以上的数字通道的差错性能的参数和指标。该建议要求差错性能的测量,建立在块的评价基础上。完成G.826建议的差错测量的测量仪器,也应坚持以块为基础的概念。在这种情况下,测量结果将得到以块差错或块差错比的形式表示的差错性能。然而,本标准并不排除,由于若干单个比特差错产生的比特差错或比特差错比的可选的测量和评价。

6.2块长

为了得到一致的测量结果,面向块的差错性能测量,需要建立在同一块长的基础上。6.2.1在 PDH系统上用于性能测量的块长G.826建议,以比特率规定开业务测量的块长,在该比特率上使用固有的差错检测码。这些块长也适用于停业务的测量。

按G.826建议要求,块长如表13。表13PDH差错性能监测的块长

比特率

(kbit/s)

139264

PDH块

(pμs)

块/秒

1)以检错码(EDC)作为基准,按EDC的工作原理提出块长。疫有规定EDC处,块长是建立在125s有关长的整数倍的基础。实际的块长可为表中给出的标称值士5%的偏差。6.2.2在 SDH系统上用于性能测量的块长表14给出SDH不同通道的差错性能测量的块长和检错码(EDC),这些块长是G.826建议为开业HiiKAoNiKAca

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。

本标准是根据ITU-TO.150(1995年修改草案)《数字传输设备性能测量仪表的通用要求》的内容而规定。在技术内容上与该国际建议等效。本标准包括可适用于数字传输设备性能测量仪表的通用信息。结合我国数字通信的PDH和 SDH传输体制,制定工作在14.4kbit/s以下、64kbit/s、N×64kbit/s.2048kbit/s、8448kbit/s34368kbit/s、139264kbit/s和155520kbit/s等比特率上的标准测试序列及其成恢测试序列的要求。本标准还规定了,在PDH和 SDH系统上差错性能测量的块长,作为面向块的差错性能测量,本标推由邮电部电信科学研究规划院提出并归口。本标准由邮电部电信传输研究所起草。本标准主要起草人:翁元举、罗建国。216

1范围

中华人民共和国通信行业标准

数字传输性能测量的数字图形

YD/T 821-1996

本标准规定了标准的和成帧的测试序列,以及在 PDH 和 SDH 系统上,差错性能测量的块长。本标准是工作在各类比特率的数字传输系统,及其复用/分用器以及开业务监测的差错性能测量及测量设备的技术设计和制造的依据。2标准的测试序列

标准测试序列是在某一规定的数字速率上,对数字传输设备或点对点的数字通道进行差错性能评价时,必需采用的测试序列。

比特差错测量,对评价数字传输设备的性能是一种重要的手段。只有测量序列的比特序列是完全已知时,才能进行所谓的“真”比特差错的测量,这时应能检出每个比特差错。而实际的业务曲于其随机性质,通常不能满足上述条件。

所以,有必要规定可再现的,尽可能接近模拟实际业务的测试序列。可再现的测试序列也是完成点到点测量的先决条件。

具有2\一1长度的伪随机序列是此问题最普通的解答。除了n个连续0(所谓的反转信号)和n一1个连续1的字符串以外,在取决于n的字符串长度内,该序列包含任意可能0和1的组合。(有关n的值,见第3章)

本标准规定了不同长度的伪随机序列。3伪随机测试序列的应用“

测试序列的特性应符合所测试系统的要求。通常,伪随机序列的长度应随被测量的比特率增加而增加。这样可以避免序列的重复频率太高,而与实践中遇到的状态不一致。伪随机序列的产生,可借助于具有适当反馈的移位寄存器。如果该移位寄存器有n级,则最大的序列长度将是2\—1比特。

如果数字信号直接地从移位寄存器的输出(非反转信号)取出,则最长的连0字符个数将等于n一1。如果该信号被反转,将产生n个连0字符。除采用移位寄存器以外,还可能有其它的方法产生具有这些特性的伪随机序列3.1·通过扰码器的差错测量

在测试过程中,可能含有扰码器。若第3章所述的n值与扰码器的级数共有整数倍,则可能得出不期望的测量结果。为了减少将产生此问题的可能性,规定了测试序列的n值为一个质数。3.2序列同步的丢失

只有在测试建立的接收侧,其参考序列正确地同步于来自被测对象的序列时,才能完成采用伪随机序列的比特差错的测量。为了获得一致的测量结果,必须规定序列同步的特性。下列要求可适用于,采用伪随机序列处理差错性能测量的全部ITU-TO系列建议。若有下列情况,则应认为序列同步丢失并应启动再同步:中华人民共和国邮电部1996-03-12批准HiiKAoNiKAca

1996-08-01实施

YD/T 821-1996

a)在某一秒的累计时间间隔内,比特差错率≥0.20,或b)能够明确地证实测试序列和参考序列不同相。3.3“成”的测量

成顿测试序列是在不相等的输入和输出的数字速率上,进行差错性能评价时,必需采用的测试序列,例如复用/分用器的差错性能评价。并且该成结构也用于不中断通信业务的开业务(In-Service)监测。面向块的差错性能测量的块长,适用于PDH和SDH系统的测量。某些测量要求测试序列在有效的帧内按净荷传送测试序列。在这种情况下,当传送顿定位信号时,将停止测试序列的传送。

详细内容在本标准的第5章中给出。3.4抖动测试

数字测试序列不仅用于差错的测量,而且也可用于测量抖动转移函数、可容许的输入抖动及输出抖动。数字线路系统和数字线路段的抖动测量应使用较长的伪随机测试序列。这种情况,对用于测量抖动的测试序列的长度应给以特别的注意,如果该序列太短(高的序列重复颊率),则测试信号的频谱分布可能实质上与实际业务性能不同。在此情况下,该测量结果将不反映实际状态。根据实贱经验,通常可用一个适当的修正系数(1.5或1.3),以修正具有随机性的实际业务和伪随机测试序列进行测量的差别。见G.823建议讨论此问题的附录A1。对于复用设备的抖动转移函数的测试,应使用本标准4.7中给出的测试序列。4数字测试序列

本章规定应采用的数字测试序列和其主要应用,见表1。表1建议采用的数字测试序列

序列长度

2°—1

213—11)

223—1

231—1

连0字符个数

参考建议

序列的应用

比特率高至14.4kbit /s以下的数据电路的差错测量比特率为 64 kbit/s 和 N X 64 kbit /s 的差错和抖动的测量比特率为1544,2048,6312,8448,32064和44736kbit/的差错和抖动的测量

SDH高阶C-3容器所有字节,C-2,C-12,C-11低阶溶器所有字节。映射入高阶C-3容器所有PDH支路比特,映射入低阶C-2、C-11,C-12 容器所有 PDH 支路比特的差错性能测量比特率为34.368和139264kbit/s的差错和抖动的测量SDHC-4容器所有字节,C-3低阶容器所有字节。映射入C-4容器所有PDH支路比特,映射入低阶C-3容器所有PDH支璐比特的差错性能测量

特定的测量任务

特定的测量任务

1)为了保证一个特定的PRBS在相应系列级的典型时钟恢复电路抖动半功率带宽内包含的抖动谱线密度的适应度,尚须进一步研究。

4.1511bit伪随机测试序列

YD/T 821---1996

本序列主要用于比特率高至14.4kbit/s数据电路的差错测量(见0.153建议)用9级移位寄存器可以产生该序列。把该寄存器的第5级和第9级的输出加到模2加法级,并将其结果反馈至第一级的输入。该序列以9个连续1的第一个1为开始。移位寄存器级数

伪随机序列长度

最长的连0序列

4.22047bit伪随机测试序列

29—1=511 bit

8(非反转信号)

本序列主要用于工作在比特率为64kbit/s和N×64kbit/s电路的差错和抖动的测量(见ITU-TO.152和ITU-TO.153建议)

用11级移位寄存器可以产生该序列,把该寄存器的第9级和第11级的输出加到棋2加法级,并将其结果反馈至第1级的输入。

移位寄存器级数

一伪随机序列长度

最长的连0序列

211 - 1 2 047 bit

10(非反转信号)

注 1当进行 N X 64 kbit /s 比特率性能测量时,连续的 8 比特块的测试序列应以连续的时隙传送。伪雌机测试序列的开头不必与恢重复率有关。

2 N在 1 到 31 之间是否可以是任意整数,需要进一步研究。4.332767bit的伪随机测试序列

本序列主要用于比特率为2048kbit/s和8448kbit/s的差错和抖动测量(见ITU-TQ.151建议)和SDH低阶C-12容器所有字节及映射入低阶C-12容器的所有PDH支路比特的差错性能测量(见ITU-T O. 181 建议)。

用15级移位寄存器可以产生该序列,将该寄存器的第14级和第15级的输出加到模3加法级,并将结果反馈至第1级的输入。

移位寄存器级数

伪随机序列长度

最长的连0序列

215 --1=32 767 bit

15(反转信号)

4.48388607bit的伪随机测试序列本序列主要用于比特率为34368和139264kbit/s的差错和抖动的测量(见ITU-TO.151建议)和SDHC-4容器所有字节、低阶C-3容器所有字节及映射入C-4容器的所有PDH支路比特、映射入低阶C-3容器的所有PDH支路比特的差错性能测量(见ITU-TO.181建议)。用23级移位寄存器产生该序列,把寄存器的第18级和第23级的输出加到模2加法级,并将其结果反馈到第1级的输入。

移位寄存器级数

伪随机序列长度

最长的连 0 序列

223 -- 1=8 388 607 bit

23(反转信号)

4.5536870911bit的伪随机测试序列本序列可用于特定的测量作业。例如,较高比特率的时延测量。如果差错性能的测量要求更长的序列,将来的研究应该考虑本序列。用29级移位寄存器可以产生该序列,把该寄存器的第27级和29级的输出加到模2加法级,并将其结果反馈到第1级的输入。

移位寄存器级数

伪随机序列长度

最长的连0序列

229 -1= 536 870 911 bit

29(反转信号)

HiKAoNi KAca-

YD/T 821--1996

4.62147483647bit的伪随机测试序列本序列可用于特定的测量作业,例如,较高比特率的时延测量。如果差错性能的测量要求更长的序列,将来的研究应该考虑本序列。用31级移位寄存器可以产生该序列,把寄存器的第28级和第31级的输出加到模2加法级,并且将其结果反馈至第1级的输入。

移位寄存器级数

—伪随机序列长度

—最长的连0序列

231 --1=2 147 483 647 bit

31(反转信号)

4.7用于PDH所有比特率的重复测试序列4.7.1用于所有比特率的10001000测试序列4.7.2作为一种任选的和用于PDH所有比特率方案的测试序列a)能够以低速率(例如10至100Hz)交替改变的两种任意可编程序的8比特测试序列。b)任意可编程序的16比特测试序列。5在不同的比特率上的成顿测试序列5.1概述

一定的测试对象,在其输入端要求特定的比特序列,以便正确工作。如数字分用器为这种设备的典型例子。该分用器需要至少含有正确的顿定位的测试信号。附加的信息,例如,奇偶校验比特、告警比特应置于规定的状态。

5.1.1测试数字分用器

这里必须考虑两种情况:

一般情况,通过数字分用器进行测量,并要求正确地组成测试信号。该信号将包含适当的恢定位字,插入(码速调整)比特和所有要求的通道附加位比特,以提供通道终端的适当的工作。这样,应按出现在正确工作的数字复用器的输出信号,来组成测试信号。该结构示于表2。表2

TS,TS2

TSs,TS

注:FAS一定位信号加告警比特

TSm一来自 1至 4支路的交替测试序列C一码速调整控制比特

TS,TS4

注,详细的复用结构在本标推的5.3至5.5中给出。其中,测试序列比特被连续的编号,这并不意味着这些比特应篇于同一序列。取决于应用的需要,在代表较低次支路的这些组,提供独立的测试序列可能更好。在第二种情况,只用于测试分用器输入部分的特性。这种测试的例子有可允许的输入抖动的测量、定顿测试、告警指示等。对于这种测量类型,测试信号不需要含有正确的插入信息,也不必要以有意义的数字信号在支路的输出出现的方法,来构成高次的数字输入信号。这种信号按表3所示构成。220

第1帧

TS,到 TSu

第2顿

YD/T 821—1996

第3顿

TSu+到S

注:FAS=顿定位信号加告警比特:TS,到TS,=可能属于一个序列的测试序列比特5.2工作在2048kbit/s比特率的数字顺5.2.1无CRC-4程序并提供公共信道信令的帧在此情况下,该顿结构如表4。

时隙0

1001 1011

11AS SSSS

注:A=远端告警指示

S=备用比特

时隙1~15

测试序列

5.2.2无CRC-4程序并提供随路信令的帧在此情况下,该顿结构如表5。

时隙0

10011011

11AS SSSS

注:A=远端告警指示

S=备用比特

日,b,c,d信令比特

时1~15

测试序列

5.2.3具有CRC-4程序和提供随路信令的恢在此情况下,该顿结构如表 6。

时题0

Co01 1011

C1AS SSSS

时隙1~15

测试序列

注:C循环允余校验比特(CRC-4)A一远端告警指示

S=备用比特

a,b,c.d=信令比特

HiiKAoNiKAca

TS+i到 TS

时隙16

测试序列

时隙16bZxz.net

abed abcd

时隙16

abcd abcd

第n顿

TSx+到 TS,

时隙17~31

测试序列

时隙17~31

测试序列

时隙17~~31

测试序列

YD/T 821--1996

5.3工作在8448kbit/s比特率的数字顿在此情况下,该恢结构如表7。

一顿含有每组为212bit的4个组,并具有848bit的长度。表7

200 bit

详细的组1到组4的结构列于表8:208 bit

附加位(O-)比特

赖定位信号(比特1至10)

1111010000

远端告警指示(比特11)

留待国内使用(比特12)

208 bit

码速调整控制比特:C11,C21,C31.C41码速调整控制比特:C12.C22C32,C42码速调整控制比特:C13.C23,C33,C43来自支路的可用于码速调整的比特(比特5~8)

注:有关插入(码速调整)比特的使用见5.1.1。5.4工作在34368kbit/s比特率的数字顿在此情况下,该恢结构如表9。

一愤包含每组为384bit的4个组,具有1536bit长度。表9

372 bit

组1至组4详细结构如表10。

380 bit

380 bit

208 bit

测试序列比特

1~200

201~408

409616

617~84(820)

380 bit

YD/T 821—1996

附加位(O-)比特

赖定位信号(比特1~10)

1111010000

远端告警指示(比特11)

留待国内使用(比特12)

调整控制比特:C11,C21,C31,C41调整控制比特:C12,C22.C32.C42调整控制比特:C13,C23,C33,C43来自支路可用于码速调整的比特(比特5~8)

5.5工作在139264kbit/s比特率上的数字顿5.5.1工作在139264kbit/s并复接34368kbit/s信号的数字懒在此情况下,该顿结构如表11。个懒包含每组为488bit的6.个组,并具有2928bit的长度。表11

472 bit

组1至组6的详细结构示于表12。组1

组2~~5

484 bit

附加位(O-)比特

赖定位信号(比特1~12)

111110100000

远端告警指示(比特13)

留特国内使用(比特14~16)

组2~5

注:有关播入(调整)比特见5.1.1。调整控制比特:Cln,C2,C3n,C4n调整控制比特:C15,C25,C35,C45来自支路的可用于调整的比特

(比特 5~8)

HiKAoNiKAca

测试序列比特

373~752

753~1 132

1 133~1 512(1 508)

484 bit

测试序列比特

473~2408

2 409~2 892(2 888)

YD/T 821-1996

5.6工作在155520kbit/s比特率上的数字顿5.6.1 SDH 基本复用结构

我国SDH基本复用结构如下:

指针处理

定位校准

图1基本复用映射结构

5.6.2SDH测试信号结构

按G.70X建议,应有正确的开销字节和有效指针的设置。5.6.2.1适用于C-4高阶容器的所有字节的测试信号结构TSS1TU-3

139264kbit/s

34368kbitls

2048kbit/s

为了测试高阶通道连接功能(HPC)和采用AU-4结构的网络单元(NE),测试信号结构TSS1是-~种适用于C-4容器所有字节,其长度按本标准4.4为223-1比特的PRBS(伪随机二进制序列)测试序列。见图2。

图2TSS1测试信号结构

5.6.2.2适用于C-3低阶容器的所有字节的测试信号结构TSS3为了测试提供高阶通道连接功能(HPC)和低阶通道连接功能(LPC)的网络单元(NE),测试信号结构TSS3是一种适用于C-3低阶容器所有字节,其长度按本标准4.4为223一1比特的PRBS(伪随机二进制序列)测试序列。见图3。

YD/T 821-1996

图3TSS3测试信号结构

5.6.2.3适用于C-12低阶容器的所有字节的测试信号结构TSS4为了测试提供高阶通道连接功能(HPC)和低阶通道连接功能(LPC)的网络单元(NE),测试信号结构TSS4是种适用于C-12低阶容器所有字节,其长度按本标准4.3为215一1比特的PRBS(伪随机二进制序列)测试序列。见图4。

图4TSS4测试信号结构

(7 × TUG-2)

5.6.2.4适用于映射入C-4容器的所有PDH支路比特的测试信号结构TSS5为了测试仅提供低阶通道适配功能(LPA-4)和采用AU-4结构的网络单元(NE),测试信号结构TSS5是一种适用于映射入C-4容器所有PDH支路比特,其长度按本标准4.4为223一1比特的PRBS(伪随机二进制序列)测试序列。见图5。HiikAoNikAca

YD/T8211996

图5TSS5测试信号结构

5.6.2.5适用于映射入低阶C-3容器的所有PDH支路比特的测试信号结构TSS7为了测试仅提供低阶通道适配功能(LPA-3)和采用AU-4结构的网络单元(NE),测试信号结构TSS5是种适用于映射入低阶C-3容器所有PDH支路比特,其长度按本标准4.4为231比特的PRBS(伪随机二进制序列)测试序列。见图6。RSOH

图6TSS7测试信号结构

5.6.2.6适用于映射入低阶C-12容器的所有PDH支路比特的测试信号结构TSS8为了测试仅提供低阶通道适配功能(LPA-12)和采用AU-4结构的网络单元(NE),测试信号结构TSS8是一种适用于映射入低阶C-12容器所有PDH支路比特,其长度按本标准4.3为25一1比特的PRBS(伪随机二进制序列)测试序列。见图7。226

6面向块的差错性能测量

6.1块差错量

YD/T 821—1996

(7 × TUG-2)

图 7TSS8测试信号结构

G.826建议规定了工作在一次群速率或一次群速率以上的数字通道的差错性能的参数和指标。该建议要求差错性能的测量,建立在块的评价基础上。完成G.826建议的差错测量的测量仪器,也应坚持以块为基础的概念。在这种情况下,测量结果将得到以块差错或块差错比的形式表示的差错性能。然而,本标准并不排除,由于若干单个比特差错产生的比特差错或比特差错比的可选的测量和评价。

6.2块长

为了得到一致的测量结果,面向块的差错性能测量,需要建立在同一块长的基础上。6.2.1在 PDH系统上用于性能测量的块长G.826建议,以比特率规定开业务测量的块长,在该比特率上使用固有的差错检测码。这些块长也适用于停业务的测量。

按G.826建议要求,块长如表13。表13PDH差错性能监测的块长

比特率

(kbit/s)

139264

PDH块

(pμs)

块/秒

1)以检错码(EDC)作为基准,按EDC的工作原理提出块长。疫有规定EDC处,块长是建立在125s有关长的整数倍的基础。实际的块长可为表中给出的标称值士5%的偏差。6.2.2在 SDH系统上用于性能测量的块长表14给出SDH不同通道的差错性能测量的块长和检错码(EDC),这些块长是G.826建议为开业HiiKAoNiKAca

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。