YD/T 627-1993

基本信息

标准号: YD/T 627-1993

中文名称:数字交换机数字中继接口(2048 kbit/s)参数及数字中继接口间传输特性和测试方法

标准类别:通信行业标准(YD)

标准状态:现行

出版语种:简体中文

下载格式:.zip .pdf

下载大小:462047

相关标签: 数字 交换机 中继 接口 参数 传输 特性 测试方法

标准分类号

关联标准

出版信息

相关单位信息

标准简介

YD/T 627-1993.

1主题内容 与适用范围

YD/T 627规定了数字交换机进入电信网时,必须满足的2048 kbit/s数字中继接口的参数和在一个交换机内必须达到的数字中继接口间的传输特性指标,以及相应的测试方法。

YD/T 627适用于各种A律PCM数字交换机。

2引用标准

GB 6879 2048 kbit/s30路脉码调制复用设备技术要求

GB 6880 2048 kbit/s30路脉码调制复用设备测试方法

GB 7611脉冲编码调制通信系统网路数字接口参数

3一般测试条件

3.1测试应在数字中继口处进行。

3.2交换机应处于正常的通话工作状态。

3.3当被测通路内侧接有数字衰减器、编码转换器、数字回声抑制器、数字话音插空装置或全零抑制器时,应使之失效。

3.4测试仪表应检测合 格,其主要指标应满足附录B(参考件)要求。

4 2048kbit/s中继接口参数及测试方法

4.1 输出口输出波形及输出特性

4.1.1指标

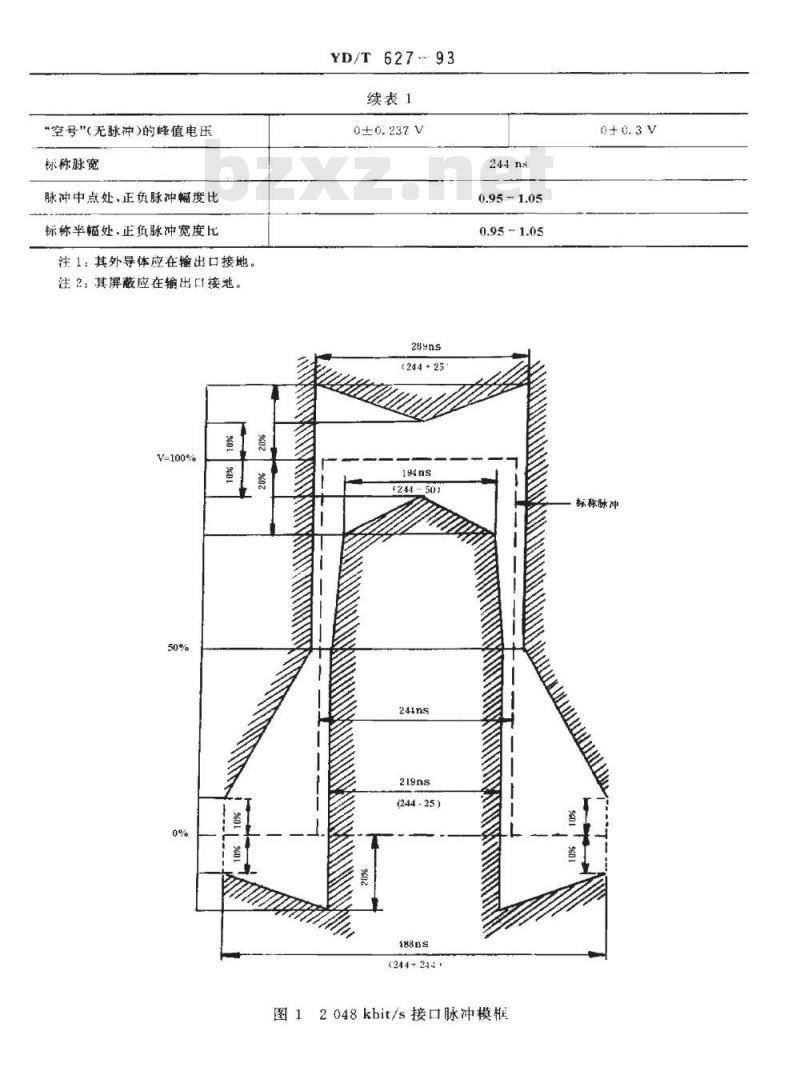

输出接口终接测试负载阻抗时,输出脉冲波形应符合图1要求,输出特性满足表1要求。

4.1.2测试连接

测试连接见图2。

4.1.3操作步骤

将交换机的数字中继的输出口、终接电阻75Ω(或12Ω),用示波器跨接在终端电阻两端进行观察测试,输出脉冲波形应符合指标规定。

4.2 输入口输入特性

4.2.1 输入口允许衰臧

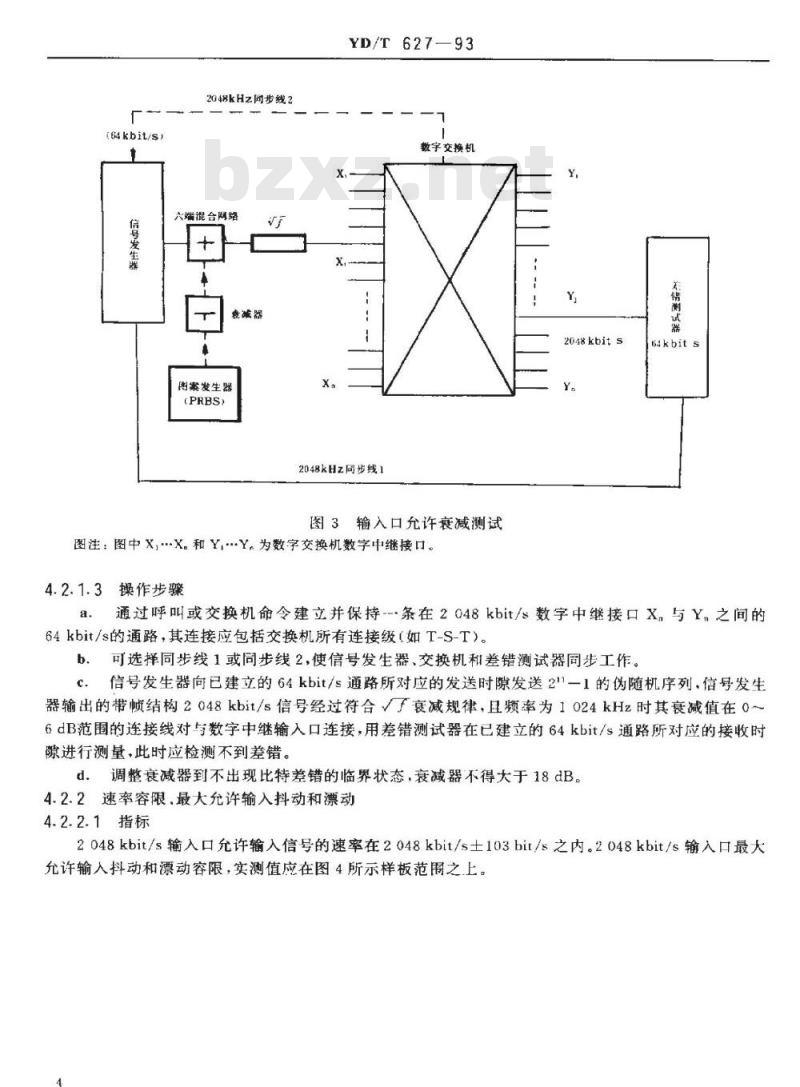

4.2.1.2测试连接

测试连接见图3。六端混合网络参见附录B。

1主题内容 与适用范围

YD/T 627规定了数字交换机进入电信网时,必须满足的2048 kbit/s数字中继接口的参数和在一个交换机内必须达到的数字中继接口间的传输特性指标,以及相应的测试方法。

YD/T 627适用于各种A律PCM数字交换机。

2引用标准

GB 6879 2048 kbit/s30路脉码调制复用设备技术要求

GB 6880 2048 kbit/s30路脉码调制复用设备测试方法

GB 7611脉冲编码调制通信系统网路数字接口参数

3一般测试条件

3.1测试应在数字中继口处进行。

3.2交换机应处于正常的通话工作状态。

3.3当被测通路内侧接有数字衰减器、编码转换器、数字回声抑制器、数字话音插空装置或全零抑制器时,应使之失效。

3.4测试仪表应检测合 格,其主要指标应满足附录B(参考件)要求。

4 2048kbit/s中继接口参数及测试方法

4.1 输出口输出波形及输出特性

4.1.1指标

输出接口终接测试负载阻抗时,输出脉冲波形应符合图1要求,输出特性满足表1要求。

4.1.2测试连接

测试连接见图2。

4.1.3操作步骤

将交换机的数字中继的输出口、终接电阻75Ω(或12Ω),用示波器跨接在终端电阻两端进行观察测试,输出脉冲波形应符合指标规定。

4.2 输入口输入特性

4.2.1 输入口允许衰臧

4.2.1.2测试连接

测试连接见图3。六端混合网络参见附录B。

标准图片预览

标准内容

中华人民共和国通信行业标准

YD/T 627--93

数字交换机数字中继接口(2048kbit/s)参数及数字中继接口间传输

特性和测试方法

1993-04-27发布

中华人民共和国邮电部

1993-11-01实施

中华人民共和国通信行业标准

数字交换机数字中继接口(2048kbit/s)参数及数字中继接口间传输

特性和测试方法

主题内容与适用范围

iiKAoNiKAca-

YD/T627—93

本标准规定了数字交换机进入电信网时,必须满足的2048kbit/s数字中继接口的参数和在一个交换机内必须达到的数字中继接口间的传输特性指标.以及相应的测试方法。本标准适用于各种A律PCM数字交换机。2引用标准

GB68792048kbit/s30路脉码调制复用设备技术要求GB68802048kbit/s30路脉码调制复用设备测试方法GB7611脉冲编码调制通信系统网路数字接口参数3一般测试条件

3.1测试应在数字中继口处进行。3.2交换机应处于正常的通话工作状态。3.3当被测通路内侧接有数字衰减器、编码转换器、数字回声抑制器、数字话音插空装置或全零抑制器时,应使之失效。

3.4测试仪表应检测合格,其主要指标应满足附录B(参考件)要求,42048kbit/s中继接口参数及测试方法4.1输出口输出波形及输出特性

4.1.1指标

输出接口终接测试负载阻抗时,输出脉冲波形应符合图1要求,输出特性满足表1要求。4.1.2测试连接

测试连接见图2。

脉冲形状(标称为矩形)

每个传输方向的线对数

测试负载阻抗

“传号\(有脉冲)的标称峰值电压不管符号如何,有效信号的所有“传号\应符合图1的脉冲模框。图中V对应于标称蜂值

个同轴线对(注1)

750电阻性

中华人民共和国邮电部1993-04-27批准一个对称线对(注2)

1202电阻性

1993-11-01实施

\空号”(无脉冲)的峰值电压标称脉宽

脉冲中点处,正负脉冲幅度比

标称半幅处,正负脉冲宽度比

注1:其外导体应在输出口接地。注2:其屏蔽应在输出口接地。

V=100%

YD/T627·93

续表1

0±0.237V

(244+25

(244-25)

(244+244

0.95-1.05

0.95~1.05

图12048kbit/s接口脉冲模框

标称脉冲

数字交换机

YD/T627-93

图2输出脉冲波形测试

图注X.X。和Y.Y。分别为数字交换机中继接口的输入口和输出口。4.1.3操作步骤

“不波器

iiKAoNiKAca-

将交换机的数字中继的输出口.终接电阻752(或1202),用示波器跨接在终端电阻两端进行观察测试,输出脉冲波形应符合指标规定。4.2输入口输入特性

4.2.1输入日充许衰减

4.2.1.1指标

将满足输出口指标的2048kbit/s数字信号,加上另一个独立的,比它电平低18dB的相同速率的伪随机序列(PRBS)后,经过符合子衰减规律的、其衰减值在0~6dB(f=1024kHz)范围内的连接线对与输入口连接时,在输出口,任一-所对应的时隙上,应检测不到差错。4.2.1.2测试连接

测试连接见图3。六端混合网络参见附录B。3

(64kbit/s)

信号发生群

2048kHz间步线2

六端混合网络

度减器

图案发生器

(PRBS)

YD/T627—93

数字交换机

2048kHz同步线1

图3输入口充许衰减测试

图注:图中X,.X。和Y.Y,为数字交换机数字中继接口。4.2.1.3操作步骤

2048kbits

芜错制试端

64kbits

通过呼叫或交换机命令建立并保持--条在2048kbit/s数字中继接口X,与Y,之间的64kbit/s的通路,其连接应包括交换机所有连接级(如T-S-T)。b、可选择同步线1或同步线2,使信号发生器、交换机和差错测试器同步工作。信号发生器向已建立的64kbit/s通路所对应的发送时隙发送211一1的伪随机序列,信号发生c.

器输出的带懒结构2048kbit/s信号经过符合了衰减规律,且频率为1024kHz时其衰减值在0~6dB范围的连接线对与数字中继输入口连接,用差错测试器在已建立的64kbit/s通路所对应的接收时隙进行测量,此时应检测不到差错。d。调整衰减器到不出现比特差错的临界状态,衰减器不得大于18dB。4.2.2速率容限、最大允许输入抖动和漂动4.2.2.1指标

2048kbit/s输入口允许输入信号的速率在2048kbit/s士103bit/s之内。2048kbit/s输入口最大允许输入抖动和漂动容限,实测值应在图4所示样板范围之上。4

抖动和激动峰-峰值(UI)(对数坐标)36.9UI

YD/T627--93

斜率值20dB10倍频程

图42048kbit/s输入口最大允许输入抖动和漂动容限f。-1.2X10-5Hz

fi=20Hz

4.2.2.2测试连接

测试连接见图5。

(64kbit,s,

信少发生器

外时钟源

fo=4.88X10-Hz

f,=0.01Hz

f,-18kHz

iiKAoNiKAca-

抖动频率(对数坐标)

J.-1.667Hz

f,=100kHz

图42048kbit/s输入口最大允许输入抖动和漂动容限数学交换机

2048kbit.s

发生器

2048kbit.s

图52048kbit/s输入口最大充许抖动容限测试图注,X.X。和YY.为数字交换机数字中继接口。4.2.2.3操作步骤

漂动测试方法待定。

同4.2.1.3(a)。

聚错测成器

b.信号发生器工作在外时钟状态,向已建立的64kbit/s通路所对应的发送时隙发送2\l一1的伪随机序列,外时钟源频率为(2048kHz/s)土103Hz的抖动发生器对2048kbit/s的数字流加不同抖动YD/T627-93

频率的抖动,用差错测试器在已建立的64kbit/s通路所对应的接收时隙进行测量,在无比待差错产生的条件下(此时应排除由滑动产生的比特差错),测得的交换机数字中继口最大输入抖动应满足图4所示的要求。

4.2.3输入阻抗及回波损耗(反射衰减)4.2.3.1指标

输入阻抗标称值应为75Q(120Q)。相当于标称比特率频率(2048kHz/s)百分数的回波损耗为:在2.5%~5%(51.2~102.4kHz)时:b12dB;在5%~100%(102.1~2048kHz)时:b,=18dB;100%150%(2048~3072kHz)时:6≥14dB。4.2.3.2测试连接

测试连接见图6。

外接或内接bzxz.net

标称值标准电网

避机反射轿

Z被测

接数字交换机

数宝中举口输入!

图6输入回波损耗的测试

图注:阻抗反射桥在测标称值为1202时,应具备测平衡阻抗的功能。4.2.3.3操作步骤

阻抗反射桥调整自身平衡:

将反射桥N端内接或外接标准电阻:先将Z、端断开,选频表量得电平为P1:c.

送频表

d.再将Z接上,此时选频表读数为P2,则回波损耗(反射衰减)为:b,=P一Pz(dB)测试信号频率为51.2~3072kHz。4.3过压保护

见附录A(补充件)关于过压保护要求的规定。52048kbit/s数字中继接口间传输特性及测试方法5.1比特差错

5.1.1指标

2048kbit/s数字中继接口间比特差错特性,由64kbit/s通路的比特差错特性反映。通过交换机的单向64kbit/s连接,长时间平均比特差错率设计指标为:Px10-

假设误码发生具有泊松分布,相当于无比特差错分百分比为:EFM%99.5%。

或比特差错分百分比为EM%≤0.5%。5.1.2测试连接

测试连接见图7。

(64kbit/s

借专发生

2048kHz同步线2

2048kbit/S

YD/T 627—93

数字交换机

2048kHz同步线1

图7比特差错测试

图注:X,X,和Y.Y,为数字交换机的数字中继接口。5.1.3操作步骤

同4.2.1.3a;

同4.2.1.3b;

2048kbit/s

iiKAoNiKAca-

(64kbit/s)

蒸销测试器

信号发生器向已建立的64kbit/s通路所对应的发送时隙发送21一1的伪随机序列,在对应的接收时隙用差错测试器连续观测24h。5.1.4检验方法

检验时间为一天(24h),测到的比特差错数为nbit按以下计算出比特差错率:P=n/(24×3600×64000)

要求比特差错率的置信区间上限≤(1.0×10\9)得出:n≤2。

如果n2或出现一次突发性差错,应查找原因再测一天,如果出现超过一次以上的突发性差错,应改善性能,再测两天,每天指标为n≤2。鉴定测试时,只能重测一次。

5.2比特完整性及比特序列独立性5.2.1指标

5.2.1.1比特完整性

允许数字信号在数字中继接口间传输,不改变任何信号源的顺序。5.2.1.2比特序列独立性

发送一进制全“1”、全“)”以及任意码,在接收侧均能正确接收。7

5.2.2测试连接

测试连接同图7。

5.2.3操作步骤

同4.2.1.3a;

YD/T627-93

同4.2.1.3b;

c信号发生器向已建立的64 kbit/s通路所对应的时隙发送以字节为单位的数字序列,其内容分别为2111伪随机序列、全\1”、全“0”“10011011”和“00011011”。差错测试器在已建立的64kbit/s通路所对应的时隙进行测量,测量时间不少于1min。所测结果应与发送的码型一致。5.3时延

5.3.1指标

2048kbit/s数字中继接口间时延特性由64kbit/s通路的时延特性反映。通过交换的64kbit/s单向连接平均传输时延小于900us,95%的概率不超过1500us1)。注,1)当负荷影响测试结果时,需在正带负荷下进行。5.3.2测试连接

测试连接见图8。

(64kbits.

信孕发生器

2048kbit,s

数字交换机

2048kbit.s

时延参考线

图8时延测试

图注:X,…X.及Y.….Y,为数字交换机的数字中维接口。5.3.3操作步骤

5.3.3.1方法1

同4.2.1.3a;

测试仪表与交换机处于独立时钟工作方式;b.

(64kbits)

时延接收器

信号发生器向已建立的64kbit/s通路所对应的时隙发送21一1伪随机序列,在对应的接收时隙用时延接收器记下所测得值。在不同时隙间测试多次取平均值,测试不少于20次。5.3.3.2方法2

在仅要求对时延做合格或不合格判断时,可采用方法2。从简测试。8

同4.2.1.3a,

b.同5.3.3.1b

TKAONKAa-

c。信号发生器向已建立的64kbit/s通路所对应的发送时隙发送211—1的伪随机序列,在对应的接收时隙用时延接收器连续观测,记下交换机与测试仪表在失步条件下,出现滑动后最大值,该值小于900 us为合格。

A1对于同轴线对接口

YD/T627—93

附录A

关于过压保护要求的规定

(补充件)

使用图A1所示的最大幅度为U的闪电脉冲发生器,产生1.2us的10个标准的闪电脉冲(5个负脉冲和5个正脉冲),以差模电压方式加到数字中继口的输入和输出门,接山应能承受这一测试而不受损伤”。

U=20V真折

[图Al

用于差模电压测试的1.2/50us脉冲发生器A2对于对称线对接口

A2.1使用图A1所示的最大幅度为U的闪电脉冲发生器,产生1.2us的10个标准的闪电脉冲(5个负脉冲和5个正脉冲),以差模电压方式加到数字中继口的输入和输出口,接口应能承受这~测试而不受损伤!。

A2.2使用图A2所示的最大幅度为U的闪电脉冲发生器,产生1.2us的10个标准的闪电脉冲(5个负脉冲和5个正脉冲),以共模电压方式加到数字中继口的输入和输出口.接口应能承受这一测试而不受损伤”。

U·moV直池

图A2用于共模电压测试的1.2/50us脉冲发生器o

注:1)过压保护测试必须小心进行。首先检查被测接口是否有过压保护设计,保护装置是否正确接人,其次检查测试装置(仪表)是否合乎规定。10

YD/T627-93

附录B

主要仪表基本要求

(参考件)

本方法配置的使用仪表,其基本要求如下:B1数字信号发生器

B1.1标称比持率

2048kbit/s容差±50×10-6

B1.2输出口电气特性

按GB68793.16.1.1条规定。

iKAONKAca-

B1.3应能发送符合GB68792.10条规定的帧结构信息,并能在其中用于通话的30个时隙中,向其中任一被选的时隙发送测试图案。B1.4线路码型

HDB、AMI码。

B1.5测试图案

211-1伪随机序列,其生成规则按GB7611附录E要求。测试图案应兼备8bit任意组合的字节测试。

B1.6时钟工作方式

主控时钟、受控时钟和外接时钟。比特差错测试器

B2.1应能接收数字信号发生器所发出的顿结构信息,并能正确选择和检测其中任一被选时隙的比特差错。

B2.2阻抗

752,1202(平衡)。

B2.3标称比特率、接收线路码型、接收测试图案、时钟工作方式,见A1相应条款。B3时延接收器

B3.1应能接收数字信号发生器所发出的顿结构信息,并能正确选择和测量其中任·一被选时隙的64kbit/s信号转换的延时。

B3.2阻抗

75Q.120Q(平衡)。

B3.3标称比特率、接收线路码型、接收测试图案、时钟工作方式,见A1相应条款。B4相位抖动测试器(含抖动调制器)B4.1调制频率在20~2400Hz之间时,输出峰到峰的抖动幅度不小于10UI;调制频率在45~100kHz之间时,输出峰到峰抖动幅度不小于0.5UI。B4.2阻抗

752,120Q(平衡)。

B4.3标称比特率,输出口电气特性,见A1相应条款。

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。

YD/T 627--93

数字交换机数字中继接口(2048kbit/s)参数及数字中继接口间传输

特性和测试方法

1993-04-27发布

中华人民共和国邮电部

1993-11-01实施

中华人民共和国通信行业标准

数字交换机数字中继接口(2048kbit/s)参数及数字中继接口间传输

特性和测试方法

主题内容与适用范围

iiKAoNiKAca-

YD/T627—93

本标准规定了数字交换机进入电信网时,必须满足的2048kbit/s数字中继接口的参数和在一个交换机内必须达到的数字中继接口间的传输特性指标.以及相应的测试方法。本标准适用于各种A律PCM数字交换机。2引用标准

GB68792048kbit/s30路脉码调制复用设备技术要求GB68802048kbit/s30路脉码调制复用设备测试方法GB7611脉冲编码调制通信系统网路数字接口参数3一般测试条件

3.1测试应在数字中继口处进行。3.2交换机应处于正常的通话工作状态。3.3当被测通路内侧接有数字衰减器、编码转换器、数字回声抑制器、数字话音插空装置或全零抑制器时,应使之失效。

3.4测试仪表应检测合格,其主要指标应满足附录B(参考件)要求,42048kbit/s中继接口参数及测试方法4.1输出口输出波形及输出特性

4.1.1指标

输出接口终接测试负载阻抗时,输出脉冲波形应符合图1要求,输出特性满足表1要求。4.1.2测试连接

测试连接见图2。

脉冲形状(标称为矩形)

每个传输方向的线对数

测试负载阻抗

“传号\(有脉冲)的标称峰值电压不管符号如何,有效信号的所有“传号\应符合图1的脉冲模框。图中V对应于标称蜂值

个同轴线对(注1)

750电阻性

中华人民共和国邮电部1993-04-27批准一个对称线对(注2)

1202电阻性

1993-11-01实施

\空号”(无脉冲)的峰值电压标称脉宽

脉冲中点处,正负脉冲幅度比

标称半幅处,正负脉冲宽度比

注1:其外导体应在输出口接地。注2:其屏蔽应在输出口接地。

V=100%

YD/T627·93

续表1

0±0.237V

(244+25

(244-25)

(244+244

0.95-1.05

0.95~1.05

图12048kbit/s接口脉冲模框

标称脉冲

数字交换机

YD/T627-93

图2输出脉冲波形测试

图注X.X。和Y.Y。分别为数字交换机中继接口的输入口和输出口。4.1.3操作步骤

“不波器

iiKAoNiKAca-

将交换机的数字中继的输出口.终接电阻752(或1202),用示波器跨接在终端电阻两端进行观察测试,输出脉冲波形应符合指标规定。4.2输入口输入特性

4.2.1输入日充许衰减

4.2.1.1指标

将满足输出口指标的2048kbit/s数字信号,加上另一个独立的,比它电平低18dB的相同速率的伪随机序列(PRBS)后,经过符合子衰减规律的、其衰减值在0~6dB(f=1024kHz)范围内的连接线对与输入口连接时,在输出口,任一-所对应的时隙上,应检测不到差错。4.2.1.2测试连接

测试连接见图3。六端混合网络参见附录B。3

(64kbit/s)

信号发生群

2048kHz间步线2

六端混合网络

度减器

图案发生器

(PRBS)

YD/T627—93

数字交换机

2048kHz同步线1

图3输入口充许衰减测试

图注:图中X,.X。和Y.Y,为数字交换机数字中继接口。4.2.1.3操作步骤

2048kbits

芜错制试端

64kbits

通过呼叫或交换机命令建立并保持--条在2048kbit/s数字中继接口X,与Y,之间的64kbit/s的通路,其连接应包括交换机所有连接级(如T-S-T)。b、可选择同步线1或同步线2,使信号发生器、交换机和差错测试器同步工作。信号发生器向已建立的64kbit/s通路所对应的发送时隙发送211一1的伪随机序列,信号发生c.

器输出的带懒结构2048kbit/s信号经过符合了衰减规律,且频率为1024kHz时其衰减值在0~6dB范围的连接线对与数字中继输入口连接,用差错测试器在已建立的64kbit/s通路所对应的接收时隙进行测量,此时应检测不到差错。d。调整衰减器到不出现比特差错的临界状态,衰减器不得大于18dB。4.2.2速率容限、最大允许输入抖动和漂动4.2.2.1指标

2048kbit/s输入口允许输入信号的速率在2048kbit/s士103bit/s之内。2048kbit/s输入口最大允许输入抖动和漂动容限,实测值应在图4所示样板范围之上。4

抖动和激动峰-峰值(UI)(对数坐标)36.9UI

YD/T627--93

斜率值20dB10倍频程

图42048kbit/s输入口最大允许输入抖动和漂动容限f。-1.2X10-5Hz

fi=20Hz

4.2.2.2测试连接

测试连接见图5。

(64kbit,s,

信少发生器

外时钟源

fo=4.88X10-Hz

f,=0.01Hz

f,-18kHz

iiKAoNiKAca-

抖动频率(对数坐标)

J.-1.667Hz

f,=100kHz

图42048kbit/s输入口最大允许输入抖动和漂动容限数学交换机

2048kbit.s

发生器

2048kbit.s

图52048kbit/s输入口最大充许抖动容限测试图注,X.X。和YY.为数字交换机数字中继接口。4.2.2.3操作步骤

漂动测试方法待定。

同4.2.1.3(a)。

聚错测成器

b.信号发生器工作在外时钟状态,向已建立的64kbit/s通路所对应的发送时隙发送2\l一1的伪随机序列,外时钟源频率为(2048kHz/s)土103Hz的抖动发生器对2048kbit/s的数字流加不同抖动YD/T627-93

频率的抖动,用差错测试器在已建立的64kbit/s通路所对应的接收时隙进行测量,在无比待差错产生的条件下(此时应排除由滑动产生的比特差错),测得的交换机数字中继口最大输入抖动应满足图4所示的要求。

4.2.3输入阻抗及回波损耗(反射衰减)4.2.3.1指标

输入阻抗标称值应为75Q(120Q)。相当于标称比特率频率(2048kHz/s)百分数的回波损耗为:在2.5%~5%(51.2~102.4kHz)时:b12dB;在5%~100%(102.1~2048kHz)时:b,=18dB;100%150%(2048~3072kHz)时:6≥14dB。4.2.3.2测试连接

测试连接见图6。

外接或内接bzxz.net

标称值标准电网

避机反射轿

Z被测

接数字交换机

数宝中举口输入!

图6输入回波损耗的测试

图注:阻抗反射桥在测标称值为1202时,应具备测平衡阻抗的功能。4.2.3.3操作步骤

阻抗反射桥调整自身平衡:

将反射桥N端内接或外接标准电阻:先将Z、端断开,选频表量得电平为P1:c.

送频表

d.再将Z接上,此时选频表读数为P2,则回波损耗(反射衰减)为:b,=P一Pz(dB)测试信号频率为51.2~3072kHz。4.3过压保护

见附录A(补充件)关于过压保护要求的规定。52048kbit/s数字中继接口间传输特性及测试方法5.1比特差错

5.1.1指标

2048kbit/s数字中继接口间比特差错特性,由64kbit/s通路的比特差错特性反映。通过交换机的单向64kbit/s连接,长时间平均比特差错率设计指标为:Px10-

假设误码发生具有泊松分布,相当于无比特差错分百分比为:EFM%99.5%。

或比特差错分百分比为EM%≤0.5%。5.1.2测试连接

测试连接见图7。

(64kbit/s

借专发生

2048kHz同步线2

2048kbit/S

YD/T 627—93

数字交换机

2048kHz同步线1

图7比特差错测试

图注:X,X,和Y.Y,为数字交换机的数字中继接口。5.1.3操作步骤

同4.2.1.3a;

同4.2.1.3b;

2048kbit/s

iiKAoNiKAca-

(64kbit/s)

蒸销测试器

信号发生器向已建立的64kbit/s通路所对应的发送时隙发送21一1的伪随机序列,在对应的接收时隙用差错测试器连续观测24h。5.1.4检验方法

检验时间为一天(24h),测到的比特差错数为nbit按以下计算出比特差错率:P=n/(24×3600×64000)

要求比特差错率的置信区间上限≤(1.0×10\9)得出:n≤2。

如果n2或出现一次突发性差错,应查找原因再测一天,如果出现超过一次以上的突发性差错,应改善性能,再测两天,每天指标为n≤2。鉴定测试时,只能重测一次。

5.2比特完整性及比特序列独立性5.2.1指标

5.2.1.1比特完整性

允许数字信号在数字中继接口间传输,不改变任何信号源的顺序。5.2.1.2比特序列独立性

发送一进制全“1”、全“)”以及任意码,在接收侧均能正确接收。7

5.2.2测试连接

测试连接同图7。

5.2.3操作步骤

同4.2.1.3a;

YD/T627-93

同4.2.1.3b;

c信号发生器向已建立的64 kbit/s通路所对应的时隙发送以字节为单位的数字序列,其内容分别为2111伪随机序列、全\1”、全“0”“10011011”和“00011011”。差错测试器在已建立的64kbit/s通路所对应的时隙进行测量,测量时间不少于1min。所测结果应与发送的码型一致。5.3时延

5.3.1指标

2048kbit/s数字中继接口间时延特性由64kbit/s通路的时延特性反映。通过交换的64kbit/s单向连接平均传输时延小于900us,95%的概率不超过1500us1)。注,1)当负荷影响测试结果时,需在正带负荷下进行。5.3.2测试连接

测试连接见图8。

(64kbits.

信孕发生器

2048kbit,s

数字交换机

2048kbit.s

时延参考线

图8时延测试

图注:X,…X.及Y.….Y,为数字交换机的数字中维接口。5.3.3操作步骤

5.3.3.1方法1

同4.2.1.3a;

测试仪表与交换机处于独立时钟工作方式;b.

(64kbits)

时延接收器

信号发生器向已建立的64kbit/s通路所对应的时隙发送21一1伪随机序列,在对应的接收时隙用时延接收器记下所测得值。在不同时隙间测试多次取平均值,测试不少于20次。5.3.3.2方法2

在仅要求对时延做合格或不合格判断时,可采用方法2。从简测试。8

同4.2.1.3a,

b.同5.3.3.1b

TKAONKAa-

c。信号发生器向已建立的64kbit/s通路所对应的发送时隙发送211—1的伪随机序列,在对应的接收时隙用时延接收器连续观测,记下交换机与测试仪表在失步条件下,出现滑动后最大值,该值小于900 us为合格。

A1对于同轴线对接口

YD/T627—93

附录A

关于过压保护要求的规定

(补充件)

使用图A1所示的最大幅度为U的闪电脉冲发生器,产生1.2us的10个标准的闪电脉冲(5个负脉冲和5个正脉冲),以差模电压方式加到数字中继口的输入和输出门,接山应能承受这一测试而不受损伤”。

U=20V真折

[图Al

用于差模电压测试的1.2/50us脉冲发生器A2对于对称线对接口

A2.1使用图A1所示的最大幅度为U的闪电脉冲发生器,产生1.2us的10个标准的闪电脉冲(5个负脉冲和5个正脉冲),以差模电压方式加到数字中继口的输入和输出口,接口应能承受这~测试而不受损伤!。

A2.2使用图A2所示的最大幅度为U的闪电脉冲发生器,产生1.2us的10个标准的闪电脉冲(5个负脉冲和5个正脉冲),以共模电压方式加到数字中继口的输入和输出口.接口应能承受这一测试而不受损伤”。

U·moV直池

图A2用于共模电压测试的1.2/50us脉冲发生器o

注:1)过压保护测试必须小心进行。首先检查被测接口是否有过压保护设计,保护装置是否正确接人,其次检查测试装置(仪表)是否合乎规定。10

YD/T627-93

附录B

主要仪表基本要求

(参考件)

本方法配置的使用仪表,其基本要求如下:B1数字信号发生器

B1.1标称比持率

2048kbit/s容差±50×10-6

B1.2输出口电气特性

按GB68793.16.1.1条规定。

iKAONKAca-

B1.3应能发送符合GB68792.10条规定的帧结构信息,并能在其中用于通话的30个时隙中,向其中任一被选的时隙发送测试图案。B1.4线路码型

HDB、AMI码。

B1.5测试图案

211-1伪随机序列,其生成规则按GB7611附录E要求。测试图案应兼备8bit任意组合的字节测试。

B1.6时钟工作方式

主控时钟、受控时钟和外接时钟。比特差错测试器

B2.1应能接收数字信号发生器所发出的顿结构信息,并能正确选择和检测其中任一被选时隙的比特差错。

B2.2阻抗

752,1202(平衡)。

B2.3标称比特率、接收线路码型、接收测试图案、时钟工作方式,见A1相应条款。B3时延接收器

B3.1应能接收数字信号发生器所发出的顿结构信息,并能正确选择和测量其中任·一被选时隙的64kbit/s信号转换的延时。

B3.2阻抗

75Q.120Q(平衡)。

B3.3标称比特率、接收线路码型、接收测试图案、时钟工作方式,见A1相应条款。B4相位抖动测试器(含抖动调制器)B4.1调制频率在20~2400Hz之间时,输出峰到峰的抖动幅度不小于10UI;调制频率在45~100kHz之间时,输出峰到峰抖动幅度不小于0.5UI。B4.2阻抗

752,120Q(平衡)。

B4.3标称比特率,输出口电气特性,见A1相应条款。

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。