SJ 50597.39-1996

基本信息

标准号: SJ 50597.39-1996

中文名称:半导体集成电路 JC54HC221型HCMOS双单稳态触发器(斯密特触发输入)详细规范

标准类别:电子行业标准(SJ)

标准状态:现行

出版语种:简体中文

下载格式:.rar .pdf

下载大小:753829

标准分类号

关联标准

出版信息

相关单位信息

标准简介

SJ 50597.39-1996 半导体集成电路 JC54HC221型HCMOS双单稳态触发器(斯密特触发输入)详细规范

SJ50597.39-1996

标准下载解压密码:www.bzxz.net

标准图片预览

标准内容

中华人民共和国电子行业军用标准FL5962

SJ 50597/39-96

半导体集成电路

JC54HC221型HCMOS双单稳态

触发器(斯密特触发输人)

详细规范

Semiconductor integrated circuitsDetaiL specification for type JC54HC221 HCMOS dualmonostable multivibrators with schmitt triggers inputs1996-08-30发布

1997-01-01实施

中华人民共和国电子工业部批准1范圈

1.1主题内容

1.2适用范围

1.3分类

1.4绝对最大额定值

1.5推荐工作条件

2引用文件

3要求

3.1详细要求

3.2设计、结构和外形尺寸

3.3引线材料和涂覆

3.4电特性

电试验要求

3.6标志·

3.7微电路组的划分

4质量保证规定

4.1抽样和检验

4.2筛选

4.3鉴定检验

4.4质量一致性检验·

4..5检验方法

4.6数据报告

5交货准备

包装要求·

6 说明事项…

6.1订货资料

6.2缩写词、符号和定义

替代性

(3)

TYKAONKACa-

中华人民共和国电子行业军用标准半导体集成电路

JC54HC221型HCMOS双单稳态触发器(斯密特触发输人)详细规范

Semiconduotor integrated circuitsDetall speeification for type JC54HC221 HCMOS dualmonostable multivtbrator's with schmitt triggers inputs范围

1.1 主题内容

SJ 50597/3996

本规范规定了半导体集成电路JC54HC221型HCMOS双单稳态触发器(斯密特触发输入)(以下简称器件)的详细要求。1.2适用范围

本规范适用于器件的研制、生产和采购。1.3分类

本规范给出的器件按器件型号器件等级和封装形式分类。1.3.1器件缩号

器件编号应按GJB597《微电路总规范)第3.6.2条的规定。1.3.1.1器件型号

器件型号如下:

器件型号

JC54HC221

1.3.1.2器件等级

器件名称

双单稳态触发器(斯密特触发辅人)器件等级应为GJB597第3.4条规定的B级和本规范规定的B,级。1.3.1.3封装形式

封装形式按GB/T7092《半导体集成电路外形尺寸>的规定。封装形式如下:

中华人民共和国电子工业部1996-08-30发布1997-01-01实施

1.4绝对最大额定值

绝对最大额定值如下:

电源电压

辙入电压

输出电压

输出电流(每端)

销位二极管电流

电源电流

贮存温度

引线耐焊接温度(10s)

1.5推荐工作条件

推荐工作条件如下:

SJ50597/39-96

外形代号

若无其他规定,-55℃≤T≤125

电源电压

输人高电半电压

输人低电平电压

V. = 2.0V

Ve = 4.sV

Ve = 6.0V

TTKAONKAa

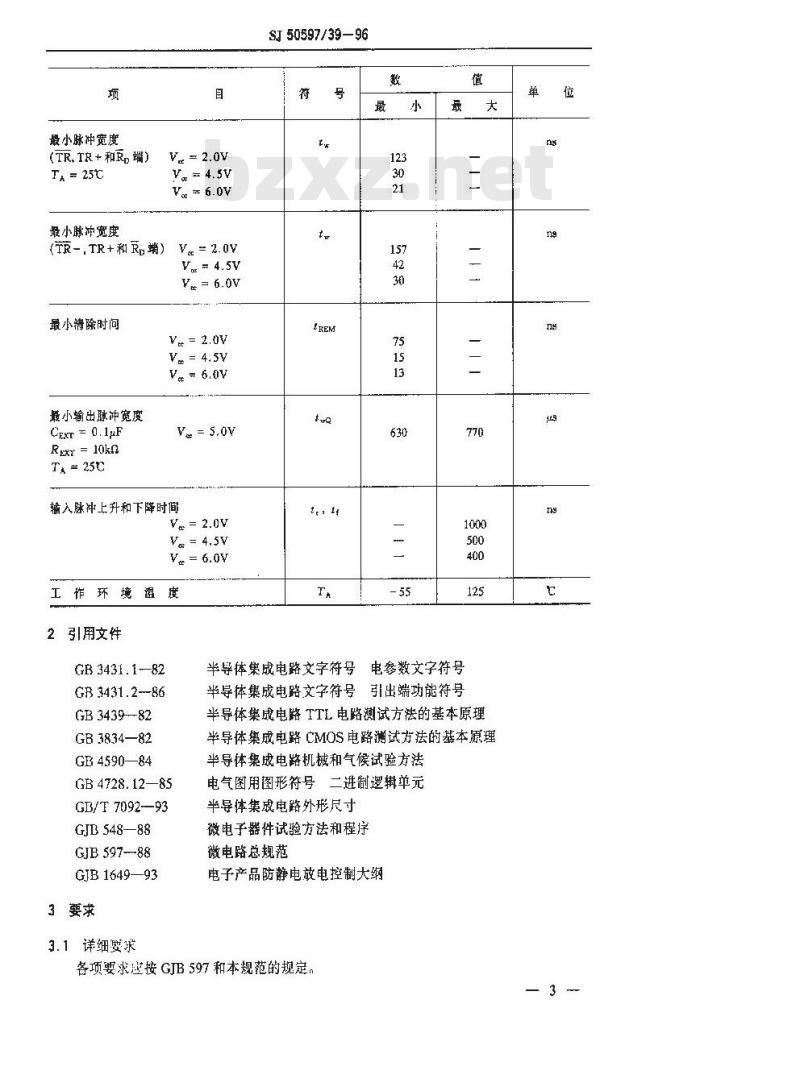

最小脉冲宽度

(TR,TR+和R。端)

TA=25t

最小脉冲宽度

V. = 2.0V

Y. = 4. sv

V. = 6.0V

(TR-,TR+和 R,端) V。 = 2.0V

Va = 6.0V

最小清除时问

小输出脉冲宽度

CexT - 0.1μF

Rex=10kn

V. = 2.0V

V. = 4.5V

Vee = 5.0V

輪入脉冲上升和下降时间

V. = 2.0V

工作环境温度

引用文件

GB 3431. 1-82

GB 3431.2--86

GB 3439--82

GB 3834—82

GB 4590—84

GB 4728. 12—85

GB/T 7092-93

GJB 548—88

GJB 597-88

GIB 1649-93

3要求

3.1详细要求

SJ 50597/3996

半导体集成电路文字符号电参数文字符号半导体集成电路文字符号引出端功能符号半导体集成电路TTL电路测试方法的基本原理半导体集成电路CMOS电路测试方法的基本原理半导体集成电路机械和气候试验方法电气图用图形符号二进制逻辑单元半导体集成电路外形尺寸

微电子器件试验方法和程序

微电路总规范

电子产品防静电放电控制大纲

各项要求虚按GJB597和本规范的规定,单

SJ 50597/39-96

本规范规定的B级器件仅在产品保证规定的筛选、鉴定和质量一致性检验的某些项目和要求上不同于 B 级。

3.2设计、结构和外形尽寸

设计,结构和外形尺寸应符合 GJB 597和本规范的规定。3.2.1逻辑符号、引出排列和逻辑图逻辑符号、逻辑图和引出端排列应符合图1的规定。引出端排列为俯视图。遇辑符号应符合GB4728.12的规定。

逻辑符号

1Ror/CexT

2RExT/CyxT

引出端排列

2CExp8

F 2n 19

184iCexT

D型,F型,H型、型

2Rexr/

14biCexy

102TR+

TKAOIKAca-

逻辑图(1/2)

SJ 50597/39 -- 96

图1逻辑符号、引出端排列和逻辑图3.2.2功能表

功能表如下:

往:H一高电平;L一低电平:X一任意:一从低电平到高电平的转换;+一从高电平到低电平的转换;『—一个高电平脉冲F—个低电平魅冲3.2.3电路图

制造厂在鉴定前应将电路图提交给认证机构存档备查。3.2.4封装形式

封装形式应符合本规范1.3.1.3条的规定。3.3引线材料和涂覆

引线材料和涂覆应按GJB597第3.5.6条的规定。3.4电特

电特性应符合表 1 的规定。

输入正轿位电压

输入负摘位电压

电源电流

输入高电平电流

输入低电平电流

輪出高电平电压

拖出低电平电压

输出短路电流

输入电容

传输延迟时间

(数据到输出夏)免费标准下载网bzxz

传输延迟时间

(数据到输出Q)

SJ50597/39-96

表1电特性

条件1

(若无其他规定,

- 550≤ TA≤1250)

V接地,lik=mA,TA=25℃

V.开路,Ix=-1imA,T,=25℃

VI= V.GND

Vi = Vo

V - GND

Vom*Vm - 1.5V, Vil = 0.3V

for = - 20μA

ViH=3.15V

IoHr =~ 20uA

Icr元-4.0mA

fo--20μA

Io---5.2mA

Vit = 0.3V, Veh = 1.5V

IoL=20μA

ViL= 0.9V

ToH = 20μA

Io. = 4.UmA

Iot=20μA

V, = oV或 V, V= 0V

TA = 25C

Vr = oV

7,15端3

其他端

Ct=50pF±10%

TA = 25r

Cl.=50pF ± 10%

CL=50pF±10%

TA=25t

Ct = 50pF = 10%

规范值

小最大

TTKAONKAa-

传崧延返时间

(滞除到输出 豆)

传输延迟时间

(清除到输出Q)

输出脉冲宽度

输出转换时间

注.1)完整的测试条件列于表 3。SI 50597739 -- 96

续表1

条件1)

(若无其他规定,

55C≤T≤125℃)

CL = 50pF ± 10%

TA = 25t

Cr = S0pF ± 10%

Cr = 50pF ± 10 %

TA = 25t

Ci, = 50pF ± 10 %

Ci=50pF ±10%

TA= 25℃

Cexr = 0.1μF ± 10%

Rexr = 10kn ± 5%

Ct = 50pF ± 10%

CExT = 0. 1μF ± 10%

Rext = 10ko 5%

CL=50pF±10%

TA= 25C

CL=50pF±10%

规范值

0.5950.805

2)表中 Vg -2.0V和 4.5V条件下的 Vom、Yo. 值只作为保证参数,可不测试。3)C型封装为 9,19端。

3.5电试验要求

器件的电试验要求,应为本规范表2所规定的有关分组,各分组的电測试按本规范表3的规定。

中间(老炼前)电测试

中间(老炼后)电测试

最终电测试

A组检验电测试

B组终点电测试

C 组终点电测试

C组检验增加的电测试

D组资点电测试

SJ 50597/39 -- 96

表 2 电试验要求

B级器件

(见本规范表3)

A2,A3, A9

A1,A2, A3, A4, AT

A8, A9.A10,AII

A1,A2,A3

A1,A2,A3

注:1)该分组要求 PDA计算(见本规范4,2条)。变化量梭限

B皱器件

(见本规范表3)

A2, A3, A9

A1, A2, A3, A4

A7. A8, A9

A1,A2,A3

A10,A11

Al, A2, A3

2)老炼和命试验要求变化量(4)测试,变化量板限按本规范4.5.2条的规定。表3电测试

引用标准

GB3834

GB3439

GB3439

GB3439

(若无其他规定,GND=OV,

TA = 25℃ )

V.接地,GND 开路,输出端开路,披测:输人端[ik=1mA。

V~开路,GN 接地,输出端开路,被测i输入端 Irk = - 1mA。

iV, = 6.0v

V=6.0V,GND接地

输出端开路

V..=h.ov.

测Q瓣时,V, 4.2V :

测总端时,V, = 1.2V

V.= 6.0V,

測 Q端时, V,= 1.2V :

谢克端时,V,=4.2V

Vi = ov

Fon= -20μuA

[oH= -5.2mA

LoH=20μA

JoH=5.2mA

V.=6.0V,被测辅入端 Vh = 6.0V,非被测输入端 Vit. = {V,输出端开路,分别测试每个输人端

V.=6.0V,被测输人端VL=0V,非被润输入端Vm=6.0V、输出端开路,分别测试每个输人端。

V.= 4. 0V,被测摘出端接地;测 Q端时V, = 4.0V :测 Q端时, V-0V

规范值

变化量极限

TTKAONKAa-

分组符

引用标准

GB 3B34

SJ 50597/39—96

续表3

(若无其他规定,GND=0V,

TA = 25℃)

规范值

Ta=125℃,除Vm+、Vz-不测外,所有参数,条件同A1分组,规范值按本规范表1T,=55,只测YoH、VoL、as,参数、条件同Al分组,规范值按本规范表1。C

V。= 0V,f = 1MHz分别7,15端

测每个摘人端对 GND芝

简电容

V。-4.5V.按功能表(见本规范3.2.2条)。其他端

V。=4.5V,T。=125C和-55C,按功能表(见本规范3.2.2条)。v.=2.0y

夜姗Va=4.5V

逐一测对应的数据端

到出端

C. = 50pF ± 10%

见本规范图2

Q端Va=4.5V

网端V=4.5V

逐测对应清除端到

输出端

C. = 50pF ± 10%

见本规范图2

测每一Q端和Q端

CL = 50pF ± 10%

见本规范图2

CexT = 0. 1μF ± 10%

Rex=10k5%

见本规范图2。

Q端V=4.5V

TA=125C,参数、条件同A9分组,规范值按本规范表1。TA=-55C,数、条件同A9分组,规范值按本规范表1。0.63

注:1)表中列出的输人端和输出嘴条件,均指被测端,未标明的输入端可为低电平、高电平或开路,未标明的输出端可接负载或开路。

2)C型封装为 9,19 。

测试电路

b.波形图

交输入电平

TR+输人

亍很-输入

TR_输人

TR+输入

3.6标志

SJ50597/39-96

图2开关测试电路和波形图

标志应按GJB597第3.6条的规定。3.6.1总剂量辐射强度标志

总剂量辐射强度标志应按GJB597第3.6.2.6条的规定。3.6.2标志的正确性

所有器件在标上器件编号后,应经受本规范表2规定的最终电测试,以验证器件编号标志的正确性。

3.7微电路组的划分

本规范所涉及的器件为第38微电路组(见GJB597附录E)。4质量保证规定

1 10 -

TYKAOIKAca-

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。

SJ 50597/39-96

半导体集成电路

JC54HC221型HCMOS双单稳态

触发器(斯密特触发输人)

详细规范

Semiconductor integrated circuitsDetaiL specification for type JC54HC221 HCMOS dualmonostable multivibrators with schmitt triggers inputs1996-08-30发布

1997-01-01实施

中华人民共和国电子工业部批准1范圈

1.1主题内容

1.2适用范围

1.3分类

1.4绝对最大额定值

1.5推荐工作条件

2引用文件

3要求

3.1详细要求

3.2设计、结构和外形尺寸

3.3引线材料和涂覆

3.4电特性

电试验要求

3.6标志·

3.7微电路组的划分

4质量保证规定

4.1抽样和检验

4.2筛选

4.3鉴定检验

4.4质量一致性检验·

4..5检验方法

4.6数据报告

5交货准备

包装要求·

6 说明事项…

6.1订货资料

6.2缩写词、符号和定义

替代性

(3)

TYKAONKACa-

中华人民共和国电子行业军用标准半导体集成电路

JC54HC221型HCMOS双单稳态触发器(斯密特触发输人)详细规范

Semiconduotor integrated circuitsDetall speeification for type JC54HC221 HCMOS dualmonostable multivtbrator's with schmitt triggers inputs范围

1.1 主题内容

SJ 50597/3996

本规范规定了半导体集成电路JC54HC221型HCMOS双单稳态触发器(斯密特触发输入)(以下简称器件)的详细要求。1.2适用范围

本规范适用于器件的研制、生产和采购。1.3分类

本规范给出的器件按器件型号器件等级和封装形式分类。1.3.1器件缩号

器件编号应按GJB597《微电路总规范)第3.6.2条的规定。1.3.1.1器件型号

器件型号如下:

器件型号

JC54HC221

1.3.1.2器件等级

器件名称

双单稳态触发器(斯密特触发辅人)器件等级应为GJB597第3.4条规定的B级和本规范规定的B,级。1.3.1.3封装形式

封装形式按GB/T7092《半导体集成电路外形尺寸>的规定。封装形式如下:

中华人民共和国电子工业部1996-08-30发布1997-01-01实施

1.4绝对最大额定值

绝对最大额定值如下:

电源电压

辙入电压

输出电压

输出电流(每端)

销位二极管电流

电源电流

贮存温度

引线耐焊接温度(10s)

1.5推荐工作条件

推荐工作条件如下:

SJ50597/39-96

外形代号

若无其他规定,-55℃≤T≤125

电源电压

输人高电半电压

输人低电平电压

V. = 2.0V

Ve = 4.sV

Ve = 6.0V

TTKAONKAa

最小脉冲宽度

(TR,TR+和R。端)

TA=25t

最小脉冲宽度

V. = 2.0V

Y. = 4. sv

V. = 6.0V

(TR-,TR+和 R,端) V。 = 2.0V

Va = 6.0V

最小清除时问

小输出脉冲宽度

CexT - 0.1μF

Rex=10kn

V. = 2.0V

V. = 4.5V

Vee = 5.0V

輪入脉冲上升和下降时间

V. = 2.0V

工作环境温度

引用文件

GB 3431. 1-82

GB 3431.2--86

GB 3439--82

GB 3834—82

GB 4590—84

GB 4728. 12—85

GB/T 7092-93

GJB 548—88

GJB 597-88

GIB 1649-93

3要求

3.1详细要求

SJ 50597/3996

半导体集成电路文字符号电参数文字符号半导体集成电路文字符号引出端功能符号半导体集成电路TTL电路测试方法的基本原理半导体集成电路CMOS电路测试方法的基本原理半导体集成电路机械和气候试验方法电气图用图形符号二进制逻辑单元半导体集成电路外形尺寸

微电子器件试验方法和程序

微电路总规范

电子产品防静电放电控制大纲

各项要求虚按GJB597和本规范的规定,单

SJ 50597/39-96

本规范规定的B级器件仅在产品保证规定的筛选、鉴定和质量一致性检验的某些项目和要求上不同于 B 级。

3.2设计、结构和外形尽寸

设计,结构和外形尺寸应符合 GJB 597和本规范的规定。3.2.1逻辑符号、引出排列和逻辑图逻辑符号、逻辑图和引出端排列应符合图1的规定。引出端排列为俯视图。遇辑符号应符合GB4728.12的规定。

逻辑符号

1Ror/CexT

2RExT/CyxT

引出端排列

2CExp8

F 2n 19

184iCexT

D型,F型,H型、型

2Rexr/

14biCexy

102TR+

TKAOIKAca-

逻辑图(1/2)

SJ 50597/39 -- 96

图1逻辑符号、引出端排列和逻辑图3.2.2功能表

功能表如下:

往:H一高电平;L一低电平:X一任意:一从低电平到高电平的转换;+一从高电平到低电平的转换;『—一个高电平脉冲F—个低电平魅冲3.2.3电路图

制造厂在鉴定前应将电路图提交给认证机构存档备查。3.2.4封装形式

封装形式应符合本规范1.3.1.3条的规定。3.3引线材料和涂覆

引线材料和涂覆应按GJB597第3.5.6条的规定。3.4电特

电特性应符合表 1 的规定。

输入正轿位电压

输入负摘位电压

电源电流

输入高电平电流

输入低电平电流

輪出高电平电压

拖出低电平电压

输出短路电流

输入电容

传输延迟时间

(数据到输出夏)免费标准下载网bzxz

传输延迟时间

(数据到输出Q)

SJ50597/39-96

表1电特性

条件1

(若无其他规定,

- 550≤ TA≤1250)

V接地,lik=mA,TA=25℃

V.开路,Ix=-1imA,T,=25℃

VI= V.GND

Vi = Vo

V - GND

Vom*Vm - 1.5V, Vil = 0.3V

for = - 20μA

ViH=3.15V

IoHr =~ 20uA

Icr元-4.0mA

fo--20μA

Io---5.2mA

Vit = 0.3V, Veh = 1.5V

IoL=20μA

ViL= 0.9V

ToH = 20μA

Io. = 4.UmA

Iot=20μA

V, = oV或 V, V= 0V

TA = 25C

Vr = oV

7,15端3

其他端

Ct=50pF±10%

TA = 25r

Cl.=50pF ± 10%

CL=50pF±10%

TA=25t

Ct = 50pF = 10%

规范值

小最大

TTKAONKAa-

传崧延返时间

(滞除到输出 豆)

传输延迟时间

(清除到输出Q)

输出脉冲宽度

输出转换时间

注.1)完整的测试条件列于表 3。SI 50597739 -- 96

续表1

条件1)

(若无其他规定,

55C≤T≤125℃)

CL = 50pF ± 10%

TA = 25t

Cr = S0pF ± 10%

Cr = 50pF ± 10 %

TA = 25t

Ci, = 50pF ± 10 %

Ci=50pF ±10%

TA= 25℃

Cexr = 0.1μF ± 10%

Rexr = 10kn ± 5%

Ct = 50pF ± 10%

CExT = 0. 1μF ± 10%

Rext = 10ko 5%

CL=50pF±10%

TA= 25C

CL=50pF±10%

规范值

0.5950.805

2)表中 Vg -2.0V和 4.5V条件下的 Vom、Yo. 值只作为保证参数,可不测试。3)C型封装为 9,19端。

3.5电试验要求

器件的电试验要求,应为本规范表2所规定的有关分组,各分组的电測试按本规范表3的规定。

中间(老炼前)电测试

中间(老炼后)电测试

最终电测试

A组检验电测试

B组终点电测试

C 组终点电测试

C组检验增加的电测试

D组资点电测试

SJ 50597/39 -- 96

表 2 电试验要求

B级器件

(见本规范表3)

A2,A3, A9

A1,A2, A3, A4, AT

A8, A9.A10,AII

A1,A2,A3

A1,A2,A3

注:1)该分组要求 PDA计算(见本规范4,2条)。变化量梭限

B皱器件

(见本规范表3)

A2, A3, A9

A1, A2, A3, A4

A7. A8, A9

A1,A2,A3

A10,A11

Al, A2, A3

2)老炼和命试验要求变化量(4)测试,变化量板限按本规范4.5.2条的规定。表3电测试

引用标准

GB3834

GB3439

GB3439

GB3439

(若无其他规定,GND=OV,

TA = 25℃ )

V.接地,GND 开路,输出端开路,披测:输人端[ik=1mA。

V~开路,GN 接地,输出端开路,被测i输入端 Irk = - 1mA。

iV, = 6.0v

V=6.0V,GND接地

输出端开路

V..=h.ov.

测Q瓣时,V, 4.2V :

测总端时,V, = 1.2V

V.= 6.0V,

測 Q端时, V,= 1.2V :

谢克端时,V,=4.2V

Vi = ov

Fon= -20μuA

[oH= -5.2mA

LoH=20μA

JoH=5.2mA

V.=6.0V,被测辅入端 Vh = 6.0V,非被测输入端 Vit. = {V,输出端开路,分别测试每个输人端

V.=6.0V,被测输人端VL=0V,非被润输入端Vm=6.0V、输出端开路,分别测试每个输人端。

V.= 4. 0V,被测摘出端接地;测 Q端时V, = 4.0V :测 Q端时, V-0V

规范值

变化量极限

TTKAONKAa-

分组符

引用标准

GB 3B34

SJ 50597/39—96

续表3

(若无其他规定,GND=0V,

TA = 25℃)

规范值

Ta=125℃,除Vm+、Vz-不测外,所有参数,条件同A1分组,规范值按本规范表1T,=55,只测YoH、VoL、as,参数、条件同Al分组,规范值按本规范表1。C

V。= 0V,f = 1MHz分别7,15端

测每个摘人端对 GND芝

简电容

V。-4.5V.按功能表(见本规范3.2.2条)。其他端

V。=4.5V,T。=125C和-55C,按功能表(见本规范3.2.2条)。v.=2.0y

夜姗Va=4.5V

逐一测对应的数据端

到出端

C. = 50pF ± 10%

见本规范图2

Q端Va=4.5V

网端V=4.5V

逐测对应清除端到

输出端

C. = 50pF ± 10%

见本规范图2

测每一Q端和Q端

CL = 50pF ± 10%

见本规范图2

CexT = 0. 1μF ± 10%

Rex=10k5%

见本规范图2。

Q端V=4.5V

TA=125C,参数、条件同A9分组,规范值按本规范表1。TA=-55C,数、条件同A9分组,规范值按本规范表1。0.63

注:1)表中列出的输人端和输出嘴条件,均指被测端,未标明的输入端可为低电平、高电平或开路,未标明的输出端可接负载或开路。

2)C型封装为 9,19 。

测试电路

b.波形图

交输入电平

TR+输人

亍很-输入

TR_输人

TR+输入

3.6标志

SJ50597/39-96

图2开关测试电路和波形图

标志应按GJB597第3.6条的规定。3.6.1总剂量辐射强度标志

总剂量辐射强度标志应按GJB597第3.6.2.6条的规定。3.6.2标志的正确性

所有器件在标上器件编号后,应经受本规范表2规定的最终电测试,以验证器件编号标志的正确性。

3.7微电路组的划分

本规范所涉及的器件为第38微电路组(见GJB597附录E)。4质量保证规定

1 10 -

TYKAOIKAca-

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。