SJ 50597.55-2002

基本信息

标准号: SJ 50597.55-2002

中文名称:半导体集成电路 JSC320C25型数字信号处理器详细规范

标准类别:电子行业标准(SJ)

标准状态:现行

出版语种:简体中文

下载格式:.rar .pdf

下载大小:377515

标准分类号

关联标准

出版信息

相关单位信息

标准简介

SJ 50597.55-2002 半导体集成电路 JSC320C25型数字信号处理器详细规范

SJ50597.55-2002

标准下载解压密码:www.bzxz.net

标准图片预览

标准内容

中华人民共和国电子行业军用标准FL5962

半导体集成电路

SJ50597/55—-2002

JSC320C25型数字信号处理器

详细规范

Semiconductor integrated circuitsDetail specificationforJSC320C25digital signalprocessor

2002-01-31发布

2002-05-01实施

中华人民共和国信息产业部批准1范围

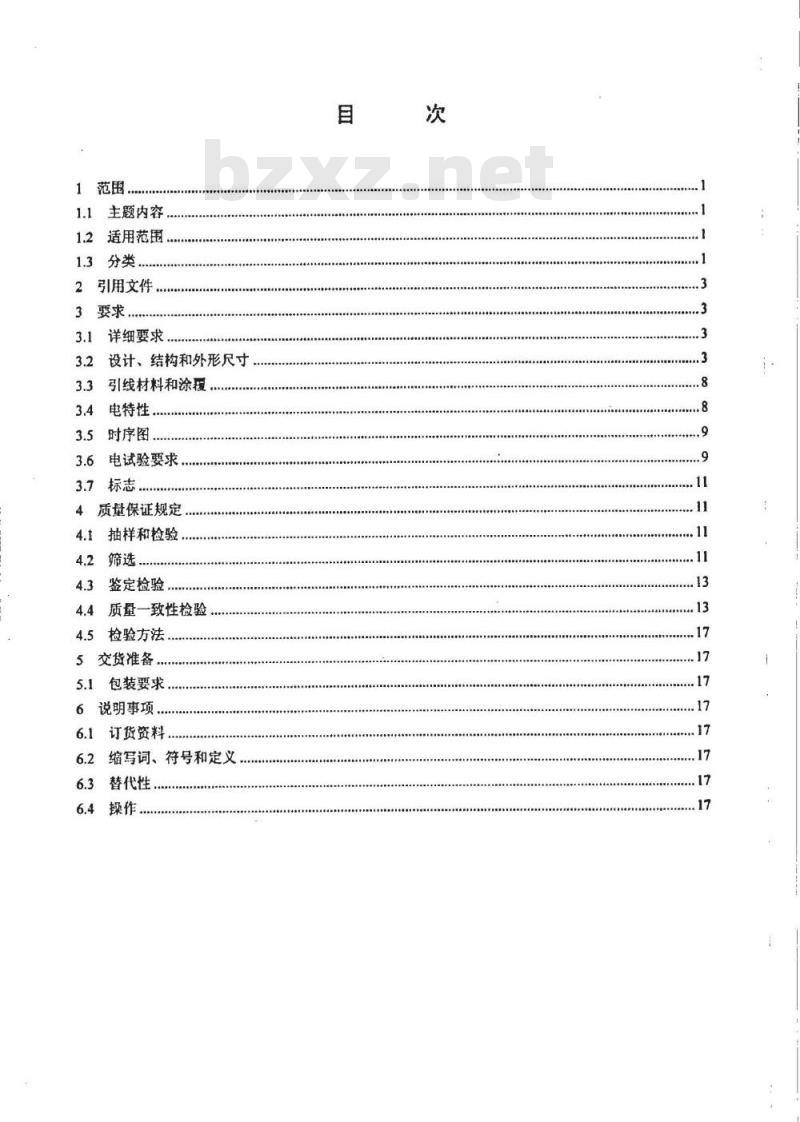

1.1主题内容

1.2适用范围。

1.3分类

引用文件。

详细要求

设计、结构和外形尺寸

引线材料和涂援

电特性

时序图

电试验要求

质量保证规定

抽样和检验,

筛选,

鉴定检验

4.4质量一致性检验

4.5检验方法

5交货准备..

5.1包装要求..

6说明事项.

6.1订货资料,

缩写词、符号和定义

替代性

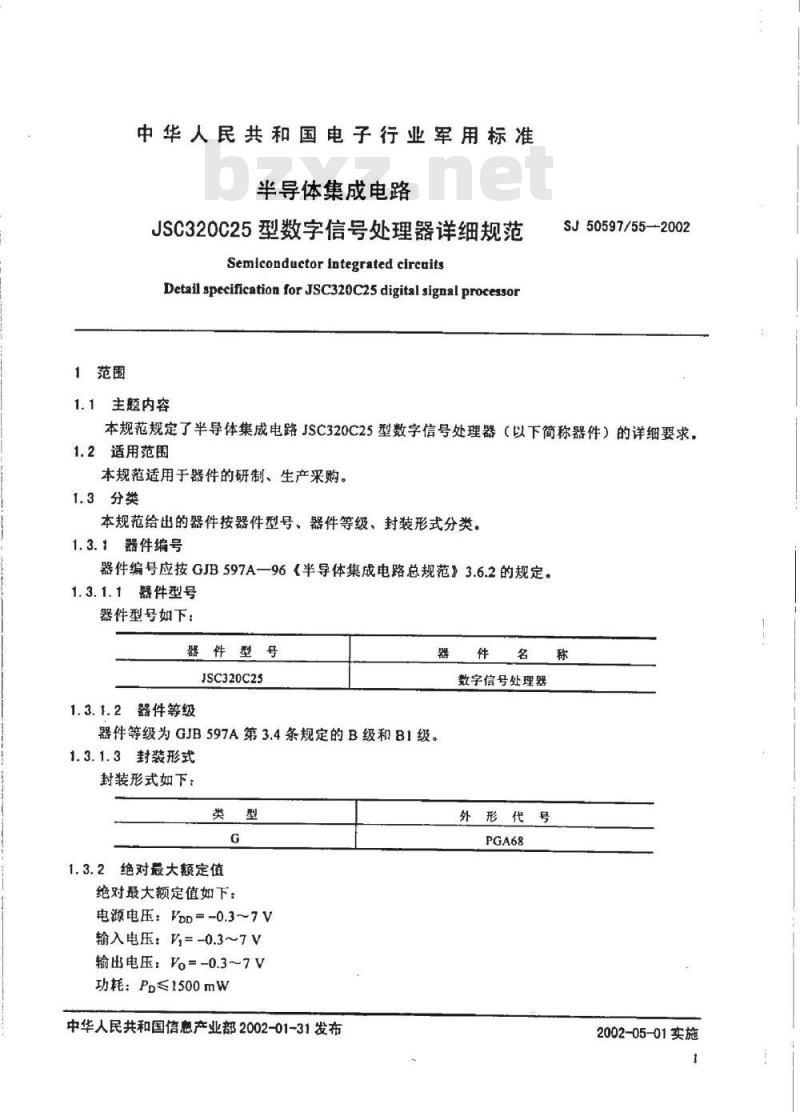

1范围

中华人民共和国电子行业军用标准半导体集成电路

JSC320C25型数字信号处理器详细规范Semiconductor integrated circnitsDetail specificationforJSC320C25digital signal processor1.1主题内容

SJ50597/55--2002

本规范规定了半导体集成电路JSC320C25型数字信号处理器(以下简称器件)的详细要求。1.2适用范围

本规范适用于器件的研制、生产采购。1.3分类

本规范给出的器件按器件型号、器件等级、封装形式分类。1.3.1器件编号

器件编号应按GJB597A—96《半导体集成电路总规范》3.6.2的规定。1.3.1.1器件型号

器件型号如下:

器件型号

JSC320C25

1.3.t.2器件等级

器件等级为GJB597A第3.4条规定的B级和B1级。1.3.1.3封装形式

封装形式如下:

1.3.2绝对最大额定值

绝对最大额定值如下:

电源电压:VDD=-0.3~7V

输入电压:V=-0.3~7V

输出电压:Vo=-0.3~7V

功耗:Pp≤1500mW

中华人民共和国信想产业部2002-01-31发布器

数字信号处理器

外形代号

2002-05-01实施

存温度:T=-65150°℃

SJ50597/55—2002

引线耐焊接温度(10s):T≤300℃热阻(结一外壳)Rth(l-C)=6°C/W结温:T≤150°℃

1.3.3推荐工作条件

推荐工作条件如下:

电源电压:Vpp=4.5V5.5V,Vss=0V工作环境温度:T=-55C~125℃

输入电容:C≤15pF

输出电容:C。≤15pF

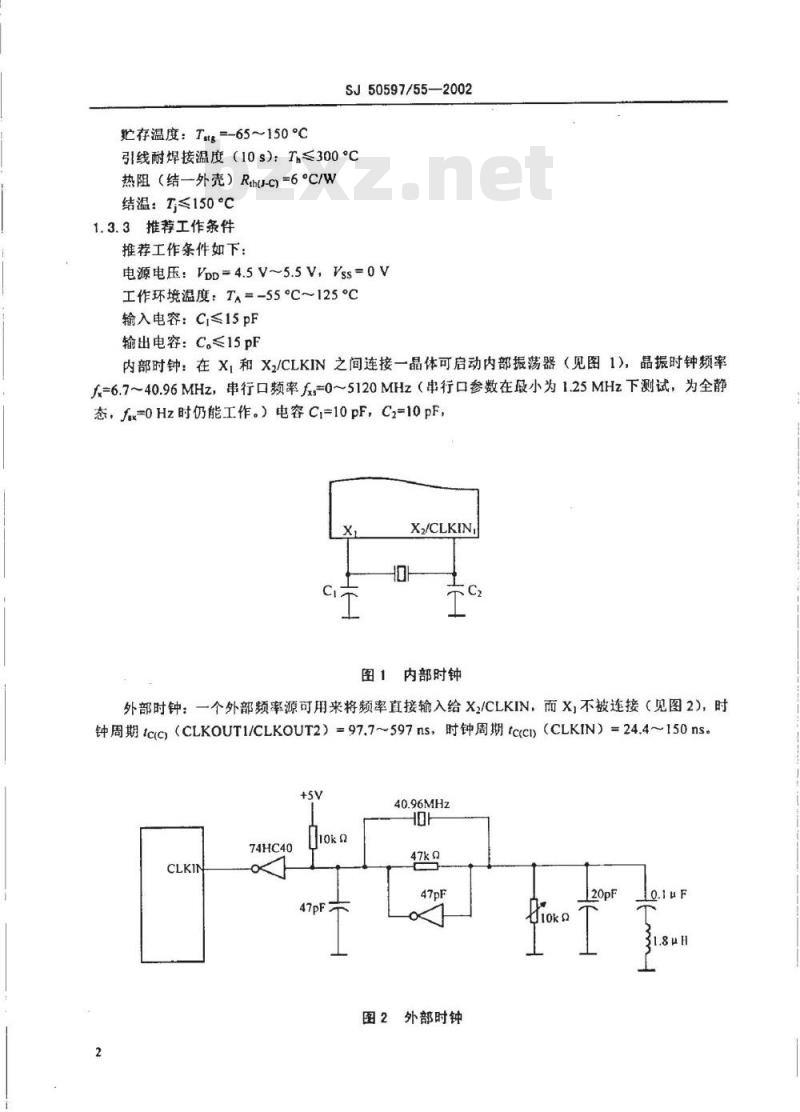

内部时钟:在X,和Xz/CLKIN之间连接一晶体可启动内部振荡器(见图1),晶振时钟频率=6.7~40.96MHz,串行口频率fx=0~5120MHz(申行口参数在最小为1.25MHz下测试,为全静态,=0Hz时仍能工作。)电容C,=10pF,Cz=10pF,X

X2/CLKIN,

图1内部时钟

外部时钟:一个外部频率源可用来将频率直接输入给X,ICLKIN,而X,不被连接(见图2),时钟周期1c(C)(CLKOUT1/CLKOUT2)=97.7~597ns,时钟周期tc(CI)(CLKIN)=24.4~150ns。+5V

74HC40

图2外部时钟

引用文件

SJ50597/55-2002

GB3431.2—86半导体集成电路文字符号引出端功能符号GB3834一82半导体集成电路CMOS电路测试方法的基本原理GB/T4728.12—1996电气图用图形符号二进制逻辑单元GJB548A一96微电子器件试验方法和程序GJB597A一96半导体集成电路总规范SJ/T10734—96半导体集成电路文字符号3要求

3.1详细要求

各项要求应按GJB597A和本规范的规定。3.2设计、结构和外形尺寸

电参数文字符号

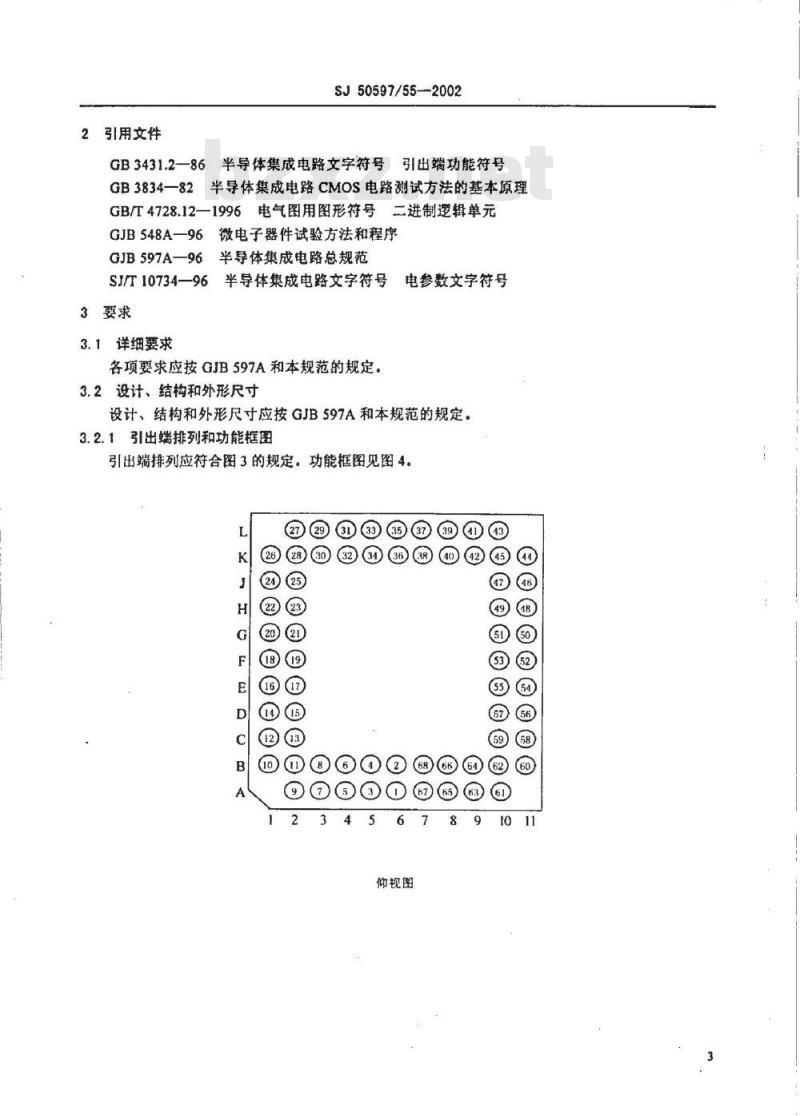

设计、结构和外形尺寸应按GJB597A和本规范的规定。3.2.1引出端排列和功能框图

引出端排列应符合图3的规定。功能框图见图4。L

0035303

00000066666

000000680

仰视图

引出端

序号/座标

微处理器/微机方案

并行数字总线

并行数字总线

SJ50597/55—2002

引出端排列图

引出端功能符号

引出端

序号/座标

并行数字总线

同步输入

外部用户中断输入

串行数据接收输入

接收输入恢同步脉冲

并行地址总线

并行地址总线

引出端

序号/座标

44/K11

45/K10

46//11

47//10

48/H11

49/H10

并行地址总线

并行地址总线

数据选择信号

输入/输出选择信号

程序选择信号bzxz.net

读写信号

选通信号

总线申请信号

外部中断

SJ50597/55—2002

引出端功能符号

数据/程序

引出端

序号/座标

51/G10

52/F11

53/F10

54/E11

55/E10

56/D11

57/D10

58/C11

59/C10

60/B11

61/A10

62/B10

数据RAM

4k字ROM

[6位乘法器

32亿ALU/ACC

指令寄存费

中断寄存器

控制器

定时器

时钟发生器

移位寄存器

图4功能框图

晶摄引脚

晶振或时钟输入

传送输入/输出顿同步脉冲

申行数据传送输出

保持响应信号

外部标志输出

次时钟输出信号

主时钟输出信号

微状态完成信号

中断响应信号

传送时钟输入

接收时钟输入

复位输入

数据准备输入

保持输入

分支控制输入

数据总线(16位)

多处理器挖口

中行接LE

并行地址总线(16位)

X/CLKIN

CLKOUT

CLKOUT

3.2.2外形图

外形图应符合图5的规定。

SJ50597/55--2002

尺寸符号

3.2.3功能测试

SJ50597/55—2002

图5外形图

该电路主频为40MHz、机器周期为25ns,执行大多数指令须4个机器周期,故其指令周期为100在功能测试中,对所有ROM、RAM寄存器、堆栈进行测试,同时在40MHz下执行所有指令。功ns。

能浏试波形图见图6。

Ais-A。

Dis-Do

3.2.4电路图(或芯片图)

图6功能测试波形图

制造厂在鉴定前应将电路图(或芯片图)提交给鉴定机构,并由鉴定鉴定机构存档备查。3.2.5封装形式

SJ50597/55--2002

封装形式应按本规范1.3.1.3条的规定。3.3引线材料和涂覆

引线材料和涂覆应按GJB597A第3.5.6条的规定3.4电特性

3.4.1电特性应符合表1的规定。表1电特性

特性)

输入高电平电压

输入低电平电压

输出高电平电流

输出低电平电流

输出高电平电压

输出低电平电压

三态漏电流

输入高电平电流

输入低电平电流

工作电流

传输延迟

上升时间

下降时间

时钟脉宽(低)2)

时钟脉宽(高)2)

传输延迟2)

间步输入建立时间

同步输入保持时间

td(CIH-C)

td(C1-c2)

fsu(s)

除另有规定外

VDD-5V-55°C≤TA≤125°℃

除CLK的所有输入端

INT(0-2)端

CLKIN CLKX

CLKR端

除CLKIN的所有输入端

CLKIN端·

VFORC =4.6V

VFORC=0.4V

f=20MHz

替通状态

IDLE、HOLD状态

外部时钟开关特性

外部时钟的时序要求3)

注:I)电压均以Vss为基准,Vs-0。电流以流入器件引出端为正。2) Q=1/4t(C)

3)时钟输入占空比[r(ch+Tw(C)Vtc(Cn)必须为40%~60%。9

规范值

3.5时序图

SJ50597/55—2002

时钟特性时序图(见图7)。其中t(cn≤5ns;trcn)≤5ns:twrcu)≥20 ns:fu(CIn≥20ns。DauO

CLKOUTY

CLKOUT

dC1-Ca

d(ci-ca)

电试验要求

terci-can

tca-c)

ta(CH-C)

ta(et-c2)

图7时钟特性时序图

各级器件的电试验要求应为本规范表2所规定的有关分组,各个分组的电测试按本规范表3的规定。表2电试验要求

(GJB548A试验方法)

中间(老化前)电测试

中间(老化后)电测试

载终电测试

A组试验要求

C组终点电测试

D组终点电测试

Al、A7

A、A71

B级器件

A2、A3、A8a、A8b、A9

纽(见表3)

B1级器件

At、A7

Al、A7

A2、A3、A8a、A8b、A9

A1、A2、A3、A4、A5、A6、A7、A8a、A8b、A9、A10、A11

AI、A7

A1、A7

注:1)该分组要求PDA计算(见本规范4.2条)。Al、A2、A3、A4、A5、A6、A7、A8a、A8b、A9、A10、A11

Al、A7

AI、A7

TA=25°C

TA=125C

TA--55°C

TA-25C

TA-125°C

TA--55℃

TA=25℃

TA=125C

TA--55C

引用标准

GB3834

第2.1条

第2.2条

第2.7条

第2.8条

第2.9条

第2.10条

第2.11条

第2.12条

第2.15条

SJ50597/55—2C02

表3A组电测试

(除另有规定外Vpp*5V))

除CLK的所有输入端

INT-2m

CLKINCLKXCLKR端

除CLKIN的所有输入端

CLKIN端

VFORCE=4.6V

VFORCE-0.4V

除外,所有参数条件同AI分组,规范值按表1除外,所有参数条件同AI分组,规范值按表1IA

第3.2条

f20MHz

所有参数条件同A4分组,规范值按表1所有参数条件同A4分组,规范值按表1见3.2.3条

同A7分组

同A7分组

警通状态

IDLE、HOLD状态

极限值

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。

半导体集成电路

SJ50597/55—-2002

JSC320C25型数字信号处理器

详细规范

Semiconductor integrated circuitsDetail specificationforJSC320C25digital signalprocessor

2002-01-31发布

2002-05-01实施

中华人民共和国信息产业部批准1范围

1.1主题内容

1.2适用范围。

1.3分类

引用文件。

详细要求

设计、结构和外形尺寸

引线材料和涂援

电特性

时序图

电试验要求

质量保证规定

抽样和检验,

筛选,

鉴定检验

4.4质量一致性检验

4.5检验方法

5交货准备..

5.1包装要求..

6说明事项.

6.1订货资料,

缩写词、符号和定义

替代性

1范围

中华人民共和国电子行业军用标准半导体集成电路

JSC320C25型数字信号处理器详细规范Semiconductor integrated circnitsDetail specificationforJSC320C25digital signal processor1.1主题内容

SJ50597/55--2002

本规范规定了半导体集成电路JSC320C25型数字信号处理器(以下简称器件)的详细要求。1.2适用范围

本规范适用于器件的研制、生产采购。1.3分类

本规范给出的器件按器件型号、器件等级、封装形式分类。1.3.1器件编号

器件编号应按GJB597A—96《半导体集成电路总规范》3.6.2的规定。1.3.1.1器件型号

器件型号如下:

器件型号

JSC320C25

1.3.t.2器件等级

器件等级为GJB597A第3.4条规定的B级和B1级。1.3.1.3封装形式

封装形式如下:

1.3.2绝对最大额定值

绝对最大额定值如下:

电源电压:VDD=-0.3~7V

输入电压:V=-0.3~7V

输出电压:Vo=-0.3~7V

功耗:Pp≤1500mW

中华人民共和国信想产业部2002-01-31发布器

数字信号处理器

外形代号

2002-05-01实施

存温度:T=-65150°℃

SJ50597/55—2002

引线耐焊接温度(10s):T≤300℃热阻(结一外壳)Rth(l-C)=6°C/W结温:T≤150°℃

1.3.3推荐工作条件

推荐工作条件如下:

电源电压:Vpp=4.5V5.5V,Vss=0V工作环境温度:T=-55C~125℃

输入电容:C≤15pF

输出电容:C。≤15pF

内部时钟:在X,和Xz/CLKIN之间连接一晶体可启动内部振荡器(见图1),晶振时钟频率=6.7~40.96MHz,串行口频率fx=0~5120MHz(申行口参数在最小为1.25MHz下测试,为全静态,=0Hz时仍能工作。)电容C,=10pF,Cz=10pF,X

X2/CLKIN,

图1内部时钟

外部时钟:一个外部频率源可用来将频率直接输入给X,ICLKIN,而X,不被连接(见图2),时钟周期1c(C)(CLKOUT1/CLKOUT2)=97.7~597ns,时钟周期tc(CI)(CLKIN)=24.4~150ns。+5V

74HC40

图2外部时钟

引用文件

SJ50597/55-2002

GB3431.2—86半导体集成电路文字符号引出端功能符号GB3834一82半导体集成电路CMOS电路测试方法的基本原理GB/T4728.12—1996电气图用图形符号二进制逻辑单元GJB548A一96微电子器件试验方法和程序GJB597A一96半导体集成电路总规范SJ/T10734—96半导体集成电路文字符号3要求

3.1详细要求

各项要求应按GJB597A和本规范的规定。3.2设计、结构和外形尺寸

电参数文字符号

设计、结构和外形尺寸应按GJB597A和本规范的规定。3.2.1引出端排列和功能框图

引出端排列应符合图3的规定。功能框图见图4。L

0035303

00000066666

000000680

仰视图

引出端

序号/座标

微处理器/微机方案

并行数字总线

并行数字总线

SJ50597/55—2002

引出端排列图

引出端功能符号

引出端

序号/座标

并行数字总线

同步输入

外部用户中断输入

串行数据接收输入

接收输入恢同步脉冲

并行地址总线

并行地址总线

引出端

序号/座标

44/K11

45/K10

46//11

47//10

48/H11

49/H10

并行地址总线

并行地址总线

数据选择信号

输入/输出选择信号

程序选择信号bzxz.net

读写信号

选通信号

总线申请信号

外部中断

SJ50597/55—2002

引出端功能符号

数据/程序

引出端

序号/座标

51/G10

52/F11

53/F10

54/E11

55/E10

56/D11

57/D10

58/C11

59/C10

60/B11

61/A10

62/B10

数据RAM

4k字ROM

[6位乘法器

32亿ALU/ACC

指令寄存费

中断寄存器

控制器

定时器

时钟发生器

移位寄存器

图4功能框图

晶摄引脚

晶振或时钟输入

传送输入/输出顿同步脉冲

申行数据传送输出

保持响应信号

外部标志输出

次时钟输出信号

主时钟输出信号

微状态完成信号

中断响应信号

传送时钟输入

接收时钟输入

复位输入

数据准备输入

保持输入

分支控制输入

数据总线(16位)

多处理器挖口

中行接LE

并行地址总线(16位)

X/CLKIN

CLKOUT

CLKOUT

3.2.2外形图

外形图应符合图5的规定。

SJ50597/55--2002

尺寸符号

3.2.3功能测试

SJ50597/55—2002

图5外形图

该电路主频为40MHz、机器周期为25ns,执行大多数指令须4个机器周期,故其指令周期为100在功能测试中,对所有ROM、RAM寄存器、堆栈进行测试,同时在40MHz下执行所有指令。功ns。

能浏试波形图见图6。

Ais-A。

Dis-Do

3.2.4电路图(或芯片图)

图6功能测试波形图

制造厂在鉴定前应将电路图(或芯片图)提交给鉴定机构,并由鉴定鉴定机构存档备查。3.2.5封装形式

SJ50597/55--2002

封装形式应按本规范1.3.1.3条的规定。3.3引线材料和涂覆

引线材料和涂覆应按GJB597A第3.5.6条的规定3.4电特性

3.4.1电特性应符合表1的规定。表1电特性

特性)

输入高电平电压

输入低电平电压

输出高电平电流

输出低电平电流

输出高电平电压

输出低电平电压

三态漏电流

输入高电平电流

输入低电平电流

工作电流

传输延迟

上升时间

下降时间

时钟脉宽(低)2)

时钟脉宽(高)2)

传输延迟2)

间步输入建立时间

同步输入保持时间

td(CIH-C)

td(C1-c2)

fsu(s)

除另有规定外

VDD-5V-55°C≤TA≤125°℃

除CLK的所有输入端

INT(0-2)端

CLKIN CLKX

CLKR端

除CLKIN的所有输入端

CLKIN端·

VFORC =4.6V

VFORC=0.4V

f=20MHz

替通状态

IDLE、HOLD状态

外部时钟开关特性

外部时钟的时序要求3)

注:I)电压均以Vss为基准,Vs-0。电流以流入器件引出端为正。2) Q=1/4t(C)

3)时钟输入占空比[r(ch+Tw(C)Vtc(Cn)必须为40%~60%。9

规范值

3.5时序图

SJ50597/55—2002

时钟特性时序图(见图7)。其中t(cn≤5ns;trcn)≤5ns:twrcu)≥20 ns:fu(CIn≥20ns。DauO

CLKOUTY

CLKOUT

dC1-Ca

d(ci-ca)

电试验要求

terci-can

tca-c)

ta(CH-C)

ta(et-c2)

图7时钟特性时序图

各级器件的电试验要求应为本规范表2所规定的有关分组,各个分组的电测试按本规范表3的规定。表2电试验要求

(GJB548A试验方法)

中间(老化前)电测试

中间(老化后)电测试

载终电测试

A组试验要求

C组终点电测试

D组终点电测试

Al、A7

A、A71

B级器件

A2、A3、A8a、A8b、A9

纽(见表3)

B1级器件

At、A7

Al、A7

A2、A3、A8a、A8b、A9

A1、A2、A3、A4、A5、A6、A7、A8a、A8b、A9、A10、A11

AI、A7

A1、A7

注:1)该分组要求PDA计算(见本规范4.2条)。Al、A2、A3、A4、A5、A6、A7、A8a、A8b、A9、A10、A11

Al、A7

AI、A7

TA=25°C

TA=125C

TA--55°C

TA-25C

TA-125°C

TA--55℃

TA=25℃

TA=125C

TA--55C

引用标准

GB3834

第2.1条

第2.2条

第2.7条

第2.8条

第2.9条

第2.10条

第2.11条

第2.12条

第2.15条

SJ50597/55—2C02

表3A组电测试

(除另有规定外Vpp*5V))

除CLK的所有输入端

INT-2m

CLKINCLKXCLKR端

除CLKIN的所有输入端

CLKIN端

VFORCE=4.6V

VFORCE-0.4V

除外,所有参数条件同AI分组,规范值按表1除外,所有参数条件同AI分组,规范值按表1IA

第3.2条

f20MHz

所有参数条件同A4分组,规范值按表1所有参数条件同A4分组,规范值按表1见3.2.3条

同A7分组

同A7分组

警通状态

IDLE、HOLD状态

极限值

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。