SJ/T 10566-1994

基本信息

标准号: SJ/T 10566-1994

中文名称:可测性总线 第一部分:标准测试存取口与边界扫描结构

标准类别:电子行业标准(SJ)

标准状态:现行

发布日期:1994-08-08

实施日期:1994-12-01

出版语种:简体中文

下载格式:.rar.pdf

下载大小:3186169

标准分类号

中标分类号:矿业>>矿业综合>>D01技术管理

关联标准

采标情况:ANSI/IEEE 1149.1-90 NEQ

出版信息

出版社:电子技术标准化研究

页数:89页

标准价格:36.0 元

出版日期:1994-12-01

相关单位信息

起草人:刘家松、邓平

起草单位:天津大学、北京自动测试技术研究所

归口单位:电子工业部标准化研究所

发布部门:中华人民共和国电子工业部

标准简介

本标准规定了数字集成电路和模拟/数字混合集成电路的数字部分用的测试存取口(TAP)与边界扫描结构。本标准规定的测试逻辑可包含在集成电路内,由一个边界扫描寄存器和若干其它块构成,并可通过测试存取口进行存龋本标准适用于在集成电路组装在一块印制电路板或其它基底上后测试集成电路间的互连性、测试集成电路本身和在这个器件正常工作期间观测或修改电路的动作。 SJ/T 10566-1994 可测性总线 第一部分:标准测试存取口与边界扫描结构 SJ/T10566-1994 标准下载解压密码:www.bzxz.net

标准图片预览

标准内容

中华人民共和国电子行业标准

SJ/T 10566—94

可测性总线

第一部分;

标准测试存取口

与边界扫描结构

Testability bus

Part I:Standard test access port andboundary scan architecture

1994-08-08发布

1994-12-01实施

中华人民共和国电子工业部发布1-1

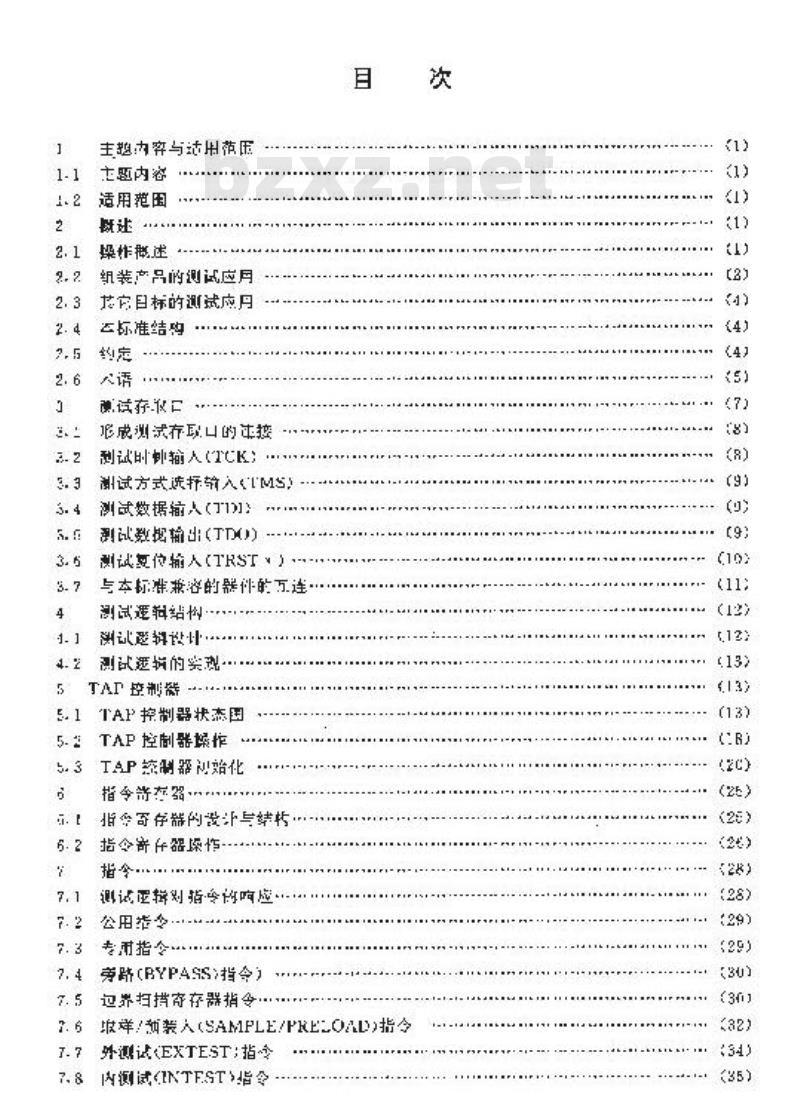

主题内穿与活用范压

主题内容

适用范围

操作费述

组装产品的测试应月

龙它日标的测斌应月

医标准结码

强试存设口

形成测试存取口的接

到试时邮输人TCK

测试方式选托入TMS

测试数据输人()

到试数揭输出)

测试复使输人TRST)

与本标准兼容的器伴的万连

测试避结划

测试避护的尝魂

TAP控制资

TAP控制器状杰国

TAP控器操作

TAP热制器初始化

指今等在器

指今可存器内设许与结构·

指令所器操作

指令…

测试量辑对指令的响应...

公用令

专肃指令

劳路(RYPASS>指令)

迎界扫措寄存器指令.

最烊/预装人(SAMPLE/PKELOAL)指令外训让EXTEST:指全

7.8内试INTEST>指全...

行装广测试(RUNS指令

7.1℃器件识别音据指含

7. 11 标识码(TDCODE)冬

72产SERCOE指会

.......

测试数据存器

测试数烟寄存能的规定

测试数据将弃解的设计与均造…测试数据奇存舒操作

劳路客存器·

学路产存器的设计与操作…

10近界月拖存器

1..边界扫描等弃单元的规定..

上O.2边界扫描寄存器的实现

In,:系续输人引时

1U.头系统时蚀教入:可

10.5二系统编出号年

10.6三系统出毕御

10. Y双向系统引脚.

11器件识别等学器·

儿:器料识别孕器的设计与换作11.2制选老标识路-

11.3部件5激码-.

11-4型式料·--

一能和文件确制受求

12.1请对车标推的·致性……

12.2原龄与三次源的器件

13.实他保要

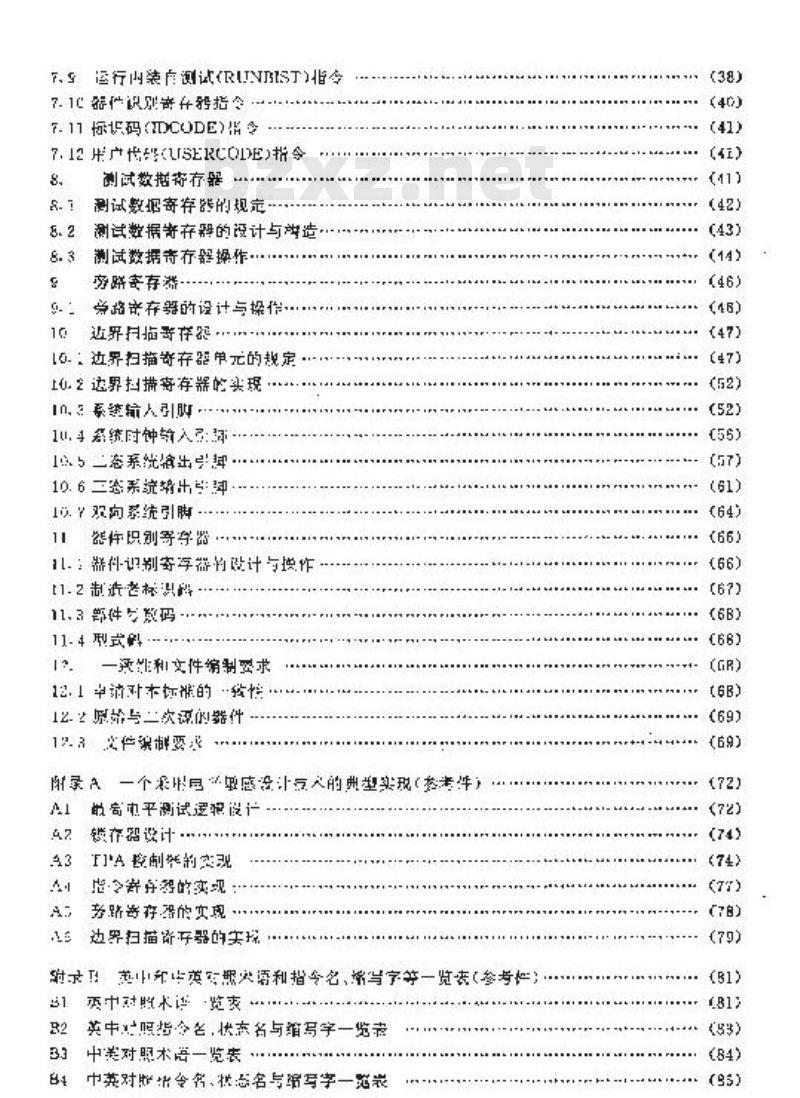

一个性月要度论计汽文的典塑实(套素件)…南录A

的司电平测试逻驱设计

锁存器设计

FIA控制举的实现

指>寄存器的实现:

务路您存登的现…

边界扫捕资存器的实现……

附求!美知中英火语和指令名,端写字等一览表(参考)….31更中对照术证览表.

英中嘎些令名状东名与箱写字一览表B3中美对照术语一览表…

B4中英对期书令名、将总名与第写学一路装2

...(43)

..(46)

(645

(68)

(68)

(72)

...(74)

(7)

..(84)

. (95)bzxz.net

中华人民共和国申学行业标准

可测性总线

第一部分:标准测试存取口

与边界扫描结构

Testablltyhas

Part I:Standard test access port andhounilary scan areliltecture1主跑内容与适用范困

$3/T10566-94

本标准短定了做字集成电略和模拟/数宁泥合莱必电路的致字部分用游谢证导取口(TA卫)与边界扫描构。本标确规定的测试恶擀可但含在策实电路内,由一个达界拓描守存器和若干其它快街或,准可通过测试存取门进行存取。1. 2适用范围

本标准适用于在荣成迅路组装在·块印制电路极或共方底上后测试奥成电路间的互理性,测试染成电路本身和在这个器付止常工作期间规或修改电路的动作。2颠述

2.1提你概送

本条提既了与本际群兼容的器们提作的概据说明。本标准规定的申路系统充许测试指令和有关测试数据债送到一个器件,从而充许读出送些报令的执行果。所有信总(指令、测试数据和测试结果)部以行格点传递。拨作序列应由-.个总线主控器控制,主控器可以是-台自动测试没备(A1E)或者一个与一杀品测试总践接口的器件,作为一个完整案统维护结构的一部分,控制是过对连技别率举线土控器的各种器件的测试方式选拆(TMS:和测试时钟(TCK)拍入施加的信号而获得的。队划始状态前起动,本标准规定的测试电陷紊统在切始状高下是待用的,一种央的操作序列如下.

适常,菜一步是把要完成这种特定操作的指令弱出行地畏人这个器件,本标准规定范避示遇拆是这样计的,指令估忌的串行传遵对些由滋指令制其操作的电踏缺并不即量的,加到这些块的指令以在移他逆(指令装入)案成时改变。一巨指令已经装入:就配些成选定测试电路予以前应,然而,在某些场合,在可以做出一种有享义的在应之前将数摄装人这定的测试电是必翌的,这些数据以和前而装人该指令的过理类假的方式带行地装入这个器,注声测试效批的传送对出我在测试电路系统中扩这条令并无影案、

中华人民共和国电子工业部1924--01994-12-01实施

SJ/T10566—94

台这条指令执行后,在需要的地方整带供给的数期,测试结果可通这将双据移出该器件到或通过总线土控器进行检查。

注意,在一测试操作但以不同的数据重其的圾仑,新测试效据可在测试结果移出时移人该器件,无需量新装入这条指令。圳试电略的操作可表似上述力式通过数入和执行芳千另外的指令维续进行以返函测试电路而结束,而且在需要的地方芯HE案统电露可返回其初始状态,2.2维装产品的测试应用

本条给出在删试个已组装产品(刻划一块印制电路板)的过程中本标规宗的逆界扫挡电路的应用概要。

2.2.1板测试月标

一套器件树成的任何产品的测试何题帮可分船为三个日标:证实每个器件家成共所要求的功能;证变各器件是以正确方式五相连接的;b.

c.证实在产品宁的各器件间正确的相车作用和该产品完成其前定的功能。这种办法是层次式的,它可以用于由崇威电路均成的印制电路板,州于山印制山龄校转成的系统或用由一较单的劝能模块性成的一个复杂奥成电路,为了简化这一计论,以后这种说明将然中到由一查数牢集成电路情成的已组装印制电断振的情视。在印制级,日标:和1通常是采用在线测试装大实现的,血目标则需要到能曾试,然而对于包含表面安教的互连术,在线测试技术就受到很大的收制,例如,使用针床央具和印制电路板上的微小型部件进行前靠接触的困期。测试访间只限于对正常的电略连接,伙有及少量专用划证点时,可接不违三个方法达对上述一个测试日标,对于日标,用干印制版级设计的染成电路的出售者会有这种器件的测试办法,这些器件可以在一台专用自动测试设备系统上测试或用埋藏在设计中的口测试过程进行测试,所采用的测试方法的信息通常器件购买者是得不的。非便有自测试操作方式,用户也会固得不到资料面不能用,印制极测试老的另外测试款据源可能随在规测试系统提供的器独测试数据赋者用户为购买的器件按收检验前开发的测试程,这种件一日组装到印制出路损上,测试间题如只限于该组装电路的止皆连接,这填任务可据较为复杂。如柔用的器件是克杂的,或者如果印制板设计者将馨件的基此连接接到固定电平感者器件引脚保持末连接状变则更加繁势,通常,以该器件在两离情况下进行测试的问样方法来测试它是不可能的,除非能将实现一户在线测试。为了保证能够使用内装测试装无,成者能够范t所先存在的测试码模式(restpattarn)就需要一台主机,它可以用来运教送往或来户各个器件边界的测试数据,固而如果这些器忙是迹立式的就可以测试飞门.这种土机也允许访间和控制器件的内装测试装置,逆界扫括知一系测试边向总线绩合起来就提供总样一种主机。本标准的口的是规定一种边界扫描结均.可采用这种结括作为采放电踏设计的标准功能部件从而能略在已组装印制电路板上或其方产品上建境所的洲试主机,2.2-2什公展边界扫描?

选界扫描技术就是紧验每个薪件引典附加::个修位奇存器级(位含在一个边齐扫描单元中).内而可以旧扫挡测试原理控制和规测器件边异上的信号。图1说明-…个边界扫指单元的典型实现,达种单为可用于境成电路的输入或辆出连接。收2

SJ/T T0586—·94

决于证到多路变换器的控制信号,数据可以由信号输入1(例如摘人引肥)装人扫播穿存器,或者这十寄存群动通过这个单元的伤号输出口(视如进人这个器件设让的核心),在后-…种常况下,提供第二个双稳(由输入时钟B控制),以保证该单元驱动稳出的信号在新数据对辅人时A移位进入该单元时保持起来(见第(率),送种双稳并不是所有场合筛要:但图1包括主以简化这神讨诊,

扫描辅日

信性确人

暂位等人

日期入

时钟A

…种拉界期芦单元

次界扫势单

风互谨

器统五透

图2一种可以边罚划摧的归制电路校设计向号编山

的事入

一个器片的别再用的这当边养扫带追元是百注的,从丽南晓这一计的边界形成一不替位奇存器链:面这条道路装备有占行输入与输山评接印话当的时钟与控制号.在-个点并十禁均业降组装的产品中行个器恒的界扫招惠存器可以出行还控起来联成·条址酒整个设计的单一通路,如图2所示,当外,个位的识计,可以包括若十条额文证界范迪路。如果州关建造个电路的所有件都有边习携守器,部么形成的再穿带个设计的串行通踏可以两种法便用

为了让许冲将件间的互连可以衡试,测试教措可以们进人和件输出引脚有关的SJ/10566—94

所有边界扫描单元和并行通过器件互连数人和输出引脚有关的那些单元,b,为了让这块板上的解件可以测试,当进行内都自测试时,逻界持描存器可用来作为两离芯片上系统超辑和由周围器件接收双的融励的一种手段,另外,如果边界扫摘尚存器尽适当设计的,它可以允许进行芯片上系就辑的一种有限慢递静测试,因为它允许测试数增传逆到该舒件并检克试结果,

这些测试能够通注使用边界扫描毒存器适到的面讨论的前两个目标。实际上,快用这种新存器进行的测试可以检测当前在载测试仪寻找的许多故阐,而无需广泛的针床访间。仍您保留款第三个目标…在功能上测试这神完整产品的操作,它可用一台功能通过可即)自动测试系统或者用一个殊统级自测试来完股。注意通过井行装入一个器件的输入和输出处的这些单元和移出这些结果+边界扫描奇存挚也提供“圾样\流过·器件的数据的手段而且不下扰读签器件或该已组装印制板的行为,这种操作方式对于设计调试和欲障诊断是有价值的,因火它允许控查这种测试系扰不能正带访间的连接:

2.3对其它目标的禅试应用

除了在测试包含多个器件的印制电路组件和其定产品中应用外,本标准规定的谢试逻也可用来提供对建造在舒件本身内的题困广泛的为了测试而设计的功能都件(deaignfar-tcatf比c9)的访问。这样的功能部件可以包括内部打描通路,自副试功能(例如,使用内装逻辑块观酒器,或其它支持坊能。这些为了划试而设计的功能部件可以用本标准规定工AP审行测试数据号引脚间的数据通路进行访问与控制造实该释件的系抛逻举内部量新配置使启动测试操作的指令可以通过该TAP移人该器件。

2.4本标准结构

按本标准规定进行的电路设计,想其技术规范闲有各个部分详图的说明案料并据供实现的实例,就查品理解前面已给出本标准对测试由许多策胶电路渠感的电子产品数字部分的应用撼述。

本标准以后各章包括有关持性和待殊功能部件的说明、其中包括2.4.1和2.4.2两类资料。

2.4.1规范

规范的各细月为靶则、推荐和许可,规则规定本标准的强制性方山,据于现则的录款具有“必须\一词。推再指出对寻求合事标准的设计的优秀实战,属于推养的条款具有“应”或“应该”词许可示出如何随够将选用的功能部件引入寻求将合本标准的设计中。这此功能部件将扩限本际准规定的测试电路系娆的应用,属于许可的条款具有“可以”或“够”一词,2.4.2说明

说明资粮附明要规定的特性或功能部件的必要性或者它们的用遍。这种资料包括说明本标据中这些规积的可能实现的简图。本标准的时录包括另一个可选用的实观例子,这种说明资料也涉及任开发本标准期间数出的设计决策。注:本协准中创括的说明再料只用于说明且的,并不规定一神优选的实测方法。2.5约定

在本标准中使洲下列约定:

S1/T 10566—94

,每十规范细目中的规,推和许可分别以一个母作标识,按字母履序连续排列,对每个规则、推荐或许可可以下列格式用.如:15.1.1C(i).其中,15.1.1为条数号,C为标认,)为选用项:

1,本标准规定的措令和状态名称以累体学表示&,居于本标准规定的测达数携寄存器的态和信号名称包含字符DR,而层于指令寄存能的包含字符IR,

d、处于低态有效的信号的名称用一个盛号作为最后享例如TRST*,e,便用正逆续约定,也就是一个说期1追号是运载量辑值号用的两个电压中比轻正的那个电压。

2.6术话

2.6.1有效的artive

当关享到一个速电平时(例低态有效)这个术语标志这一逐辑电平,借号置为该电平就遗成规庭的动作发生,当美系到辑出巫效时(例如,有效驱动),这个术语说一快态,贴的爵始千该状态就能够决定它车接的网结电压,2.6.2双而脚bidirecionall in

条既能吸动外部连费又能从外部连换收信孕的端件引脚,2.6.3内装逻辑块规器(BILBO)buitt in togicblock pbscrver(B[LBO)一种用了某些避式的口测试电路设计的基于移位存器的轨持。2-6,4询间blindinterragatlo

在未率步了解穿过问的持定解件的测试课辑操作的情说下,对一种装置(倒妞,器件识别商存器>的访问。

2.6.5旁路BYPASS

用宁本标准规是测试逻辑的一案规定指令(犯了,4),2-6-6板上芯片测试chp-on-boardlestiug在一个器件组矩在申制电路板就其它基底上后对家的测试。2.6.7时钟CLOCK

一种情号·在既和高遥抵电平(或反过亲)间的转变用来指示一个存储状态器件(比妞一个双偿或锁存器)何时可以进行操作。2.6.8外部调试EXTET

用于本标准规定测试逻辑的一亲规定指令史7.7),2.6.9下降沿lalliag edge

,.个从高遂电平到低电平的转变,在正逐辑中,一个从辑1到逻辑心的变化,2- 6. 10 商 high

用来运载一个单独信息位的两个电压中较高的那个电压。对于正逆辑,是逻辑1。2.6.11标识码IXCODE

周工本标评提定测试逻辑的一签规定指零(见17)2. 6. 12待用的 inactive

当关系到一个够出坚动器(例如,一个得用的驱动),这个术沿说明这一状志,驱动器处于该状态就不能决定它连按的网络电压。2.6.13输入引脚inputpin

SJ/T10566—94

一个从外部接接收借号的器件即。2.6.14指令ur

·个因行移人木标准规定的划试巡辉的二进制款据字,用以规亲随后发生的操作。2-6-15用部测试INTE

用于不标推规定测试逐辨的条规足指令(则7,8)2-6-16最低有效应(LSD)legtaignficnnl bit(LSB)在一个,“选制微字中代裳尽小数值的那一,对丁移位寄存靠,邮位在最靠近牢行摘出处,或者第一个要移出的位。一个二进制字或移位备在期的最低有效位编号为心:,26电平敏感满设(eeitiar:ig)

行控设计技术的一种变型,它产生无竞争的可测试数字电电路。2. 6. 18低0%

用半运载一个单减估良位的两个电压中较低的那个电压。对于正逻拇是逻辑,2.619展商有效位(MSB)nastRnificantbittMS)在:个二过制数字中代志地大数佐的那-位。对于移位寄存器,足离中行输出最远的那一位敢客是量心帮出的那一总,以一进逆制形式表示的逻辑值将最商有效位放在主边2G-2非时钟 nonclcck

一种行号,它在低和尚遵担电乎间转变时,不成在储状起器件的操作,这个率报电平只布时钟信号发生拍效时习是正要间。2.6.21给出引upup:

一个将信母驱动到外前迁控上的最件引期,2.6.22脚21

在案成中路和其安装的与志《到打印制电路板》之间形成的连接点对于封滋的号件,它是过数引脚:对于直按安装在菌底上的器件,它是连获盘。2.6.23深购源priescurce

在凸二个出也么供引脚烂引脚兼弃器件的冰况下,原始源是推出这种器偿型号的出告香。

2.6.2专洲ive

预定专供该器独也逆者使用的一仲设计待性。2.6.25公用mlic

在盗下教与图表中提诺斑料的一种设计待性,可由该留件购买者使月:2.6.26上升沿:ising edge

-个从低到高逆每由平的转变,对于正逻辑-·个从趣辑心到避解1的变化。2.6.27运行内装自试RVLIBJST

出十本环随规定的测试逆的条规定的指令(.?.9),2.6.28取样顶装入SAMPLE/PRELOAD承F本标准织患的测试理辑的一录独宽的措令(见7.6)。2.6-29扫描计xcandesign

一种设技术,它将移位寄存通踏引入效宁电电替中并及面改普它们的可测性,2-6.30描通路saraEall

通过用归描说计技术设计的一个电路的移位部存暨通路。2.6-37.饮源enlun

SJ/T10566--94

在若十出每者提供叫脚对引再兼容举件的情记下,二次源供应都是原始谦以外的件出者。

2.6.32选定的测试数据毫存selectedtes:detoregister当报供治测试运择的一杀指令的操作需一个测试致据讲存器时就迷定一个,2.6.33待征分折signatureanalysis一种用小将来自一个被测电路的迟母值输出序列无储成一个小位数的数据(特征)的技术,该散据与存储的效携比较会指出电路中存在或不存在故摩,2-F.34独立的测 staod-alnneterting在一个器件按装在一块印制报或其它基底上之前进行的·种测试.例妇使用ATE。2. 6.35固定型做障 grk-ar taal在遇辑电龄中一种避成一个信号连接固定在心或1的故床,不管驱动它的电路操作如何,2.6.36系统syetem

属干这个电降的其测试功能,

2.6.37系统逻频sysemlogc

专门用于实现该器件的非测试功能的任何连辑装配或在感兴趣时配宣起来以实现非测试功能的基些方而的任何逻抵装置。2.5.38系统引9ysiemria

一种器什引博,定谈逆到芯片上的离统逆来变用该逻带快送到它,2.6.39谢试收(TA)teatceesspc(A)本标准规定的测试行取!!(见第3章)。26.40测时钟TCK)1:k(TK)

本标推规定的TAP中包含的测试时钟输人引(见3.2)。26.41试数输)testdatanputD)

本标准规定的TAP中包含的测试数据箱入引脚(见3.4)。2.6.42试数热输出法为本怀准奶定的御试遇扭续构的…个专用部分的仍问必辑装过戴在感兴趣时配起来作为本标准规定的测试逻较结构的一部分的任何退朝装置。2.6.44测试方式选择(TMS)[elmodesclec(TMS)本标准规定的下AP中也含的测试方支选拆物人引脚(见3.3)。2.6.45试忘铃用于益标准规定的测试还辑的一条规是的指令(见?,2)。2.6.4/—脑 8-state pin

一种器件输出引,其驱动可以是有效的或者待用的(例如:处工高阻航),3测试存取口

SJ/1056594

测试存单口(7P是一通用口,以提供对一不器件内装的许多试支持均能的访问,包指间本标雅规定的馈试逆辨,飞丧本标准规定的划试采辑所而的三个渐入连接和一个输出连接的最小两组成。一个选用的第四输大连接握供过本标准规定的测试逻辑的异步初始F.

3.1形成测试在股口的连据

3.1.1规范

a.TAP必动色括下例连报3.2.3.3.3.4机3.5中规定的>.TCK,TMS.FII利TDO.

.作为测试逆样内装动范部件内个结果.TA超制器在接通电源时小享位的场合+必须按照3.5中所定义极供一个TRST+摘人(见5.5)。C:所有T给人和拍出部必长对这器性专用湾情已就是就用的出再必须不用手在共日的》

3.1.2说明

专用TA连携是费要的,以便能账读间本标准企部强创性特性。32谢试时钟愉人(CK

TCK提供本标准规定的测试题步的时钟。3.2.1规范

测试量据中包指的存结裁态器件在加TK上的信号许止在心时必须无限期地特出们你状态

b、尚为对于许多薪件的TCK愉入可能是由一个单-的驱动器控制的、应该小心长出TCK渠供的负赖要尽可能小:

c,谢式没拼中包括的存储状声器件在加到TCK上的信亏停止在1时可以无限期地课持产们的状志,

3.2-2锐明

因为色合用心式输入,所总器件间的半行测式款据道路可以独立地由器规定的案统时钟使用,这器件和那一器件的系统时钟在瓶率上可以大不相间。它也,允许该器件进行系统探作的同时移动测试数据,募安尼一均能去支持一个希线系统监规的设计十他用TAP和测试数据寄序强。提供一个将立的时钟以保证色不欢变心片上累统逻辑状态的情况下可将测试整推传送例该芯片要出芯片送出来。如边界打挡寄存器在所有外境一,对即制板互速预试新可使到的诺,独立的时钟也趋重要的一一包括在一个强件中导出的系统时钟信号在其竺券件使用的情况。

内为在许多场合TCK将斗,个标准凸空比0%的口由时钟驱动,就可能有需要时钟停止一个周期的情说,一个子尺有存A工上专从后备存储器:例如:继盘)取测试教握时,因为其此试系统不旋月来在这独保作期间保持时钟运行。本标准要求在TCK可以无阻期地停小在(而不造成测试逻辑状志的任何改变。当工CK信号停止时,需要存请状恋器件保持它们的状态,便在时钟操作启动时测式宠啦可以绝续它的操性。作为-种选样,个SJ/T1056694

器件也可以许TC无限期地停止在I。3.3衡试式选泽愉入(TMS)

在1MS上接收的信导由TAP控问器评再以控划测试操作。3.3.1规范

在TMS山出我信号必须测试逆辑在TGK的上升沿取样a

b由TMS伊这的心路系统总须是这设计的,·个非驱动的愉人产生个等同于如上一个逻辑1的响应:

因为对许多器件的TS输入可以是小·个单·离动控制的,应该小心保证出.

了M提供的负载要尽能小,

因为包括规则3..:b.所以在个驱动TMS引脚场合让TAI控制端强制进人测试逻辑一复位(Tesr一nie一Rerer)控制等杰,这就保证个设计的上常操作可以继续而不受来凹测试退升的下扰(见5.3,对于品体算品休并逻抵(TT1.兼李的设计,可通过在该器件的1MS输入电路系就中包括--个上充电阻来满这-热州,在TM上出观的信号值品中划试逆辑作TK升沿职栏的,总线主控露(A工F,总线培制器等)将在TCK的下降消改变以连要群件的TMS输人的:求动信号,在木标准其它地方示出的波形反映出这种情况,

3.4测试数据输入(TPT)

测试逻辨在TDI1.换收车行谢试指令与数据:3.4.1规

3.在T上山现的信号必纳在TCK的上并收样选人测试举抖:山送的电路系统必测这样设个非驱动的输人产牛·个等同于那上·个调:的度

C.当数据存以TLI多动TD时在TDI.上接收的信号必纳在由指令选定测试效圾寄存器的长使谁乐的一乐教日的CK上升和下降沿后不赖倒地出现在TDO上。3.4.2说明

教据引脚(TT印TTX是为测试效据通过这个电路甲行信送而违备的,包括要不颜例地从明到传送粒据的费求,以简化在换印判电路核链接和本标兼穿的器件的操在TD1十出原的偿是在TCK的上记球到造的存(指含或测试数抵)中的,总规三控器(AI上,总线税制婴举)将在IK的不降沿改变坚动到一条行板级通路上第一器件工D1瘤入的信号。在本标准别的地方示品的该彦反映出这种惜况。因为包传规则3.4、1山,所以该核级行测试敢据尚陷中的踏放障造成-个规定的逻值移入测试起料,注意当达常数值移人指令寄存器时就会选定旁路许存器如挤准7.4中光一振讨论的),对下:T,落穿的设计,可通就士该器计的撤人路中包含一个1拉电阻米满足这一规则,

3.5测试款推筑出T0

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。

SJ/T 10566—94

可测性总线

第一部分;

标准测试存取口

与边界扫描结构

Testability bus

Part I:Standard test access port andboundary scan architecture

1994-08-08发布

1994-12-01实施

中华人民共和国电子工业部发布1-1

主题内穿与活用范压

主题内容

适用范围

操作费述

组装产品的测试应月

龙它日标的测斌应月

医标准结码

强试存设口

形成测试存取口的接

到试时邮输人TCK

测试方式选托入TMS

测试数据输人()

到试数揭输出)

测试复使输人TRST)

与本标准兼容的器伴的万连

测试避结划

测试避护的尝魂

TAP控制资

TAP控制器状杰国

TAP控器操作

TAP热制器初始化

指今等在器

指今可存器内设许与结构·

指令所器操作

指令…

测试量辑对指令的响应...

公用令

专肃指令

劳路(RYPASS>指令)

迎界扫措寄存器指令.

最烊/预装人(SAMPLE/PKELOAL)指令外训让EXTEST:指全

7.8内试INTEST>指全...

行装广测试(RUNS指令

7.1℃器件识别音据指含

7. 11 标识码(TDCODE)冬

72产SERCOE指会

.......

测试数据存器

测试数烟寄存能的规定

测试数据将弃解的设计与均造…测试数据奇存舒操作

劳路客存器·

学路产存器的设计与操作…

10近界月拖存器

1..边界扫描等弃单元的规定..

上O.2边界扫描寄存器的实现

In,:系续输人引时

1U.头系统时蚀教入:可

10.5二系统编出号年

10.6三系统出毕御

10. Y双向系统引脚.

11器件识别等学器·

儿:器料识别孕器的设计与换作11.2制选老标识路-

11.3部件5激码-.

11-4型式料·--

一能和文件确制受求

12.1请对车标推的·致性……

12.2原龄与三次源的器件

13.实他保要

一个性月要度论计汽文的典塑实(套素件)…南录A

的司电平测试逻驱设计

锁存器设计

FIA控制举的实现

指>寄存器的实现:

务路您存登的现…

边界扫捕资存器的实现……

附求!美知中英火语和指令名,端写字等一览表(参考)….31更中对照术证览表.

英中嘎些令名状东名与箱写字一览表B3中美对照术语一览表…

B4中英对期书令名、将总名与第写学一路装2

...(43)

..(46)

(645

(68)

(68)

(72)

...(74)

(7)

..(84)

. (95)bzxz.net

中华人民共和国申学行业标准

可测性总线

第一部分:标准测试存取口

与边界扫描结构

Testablltyhas

Part I:Standard test access port andhounilary scan areliltecture1主跑内容与适用范困

$3/T10566-94

本标准短定了做字集成电略和模拟/数宁泥合莱必电路的致字部分用游谢证导取口(TA卫)与边界扫描构。本标确规定的测试恶擀可但含在策实电路内,由一个达界拓描守存器和若干其它快街或,准可通过测试存取门进行存取。1. 2适用范围

本标准适用于在荣成迅路组装在·块印制电路极或共方底上后测试奥成电路间的互理性,测试染成电路本身和在这个器付止常工作期间规或修改电路的动作。2颠述

2.1提你概送

本条提既了与本际群兼容的器们提作的概据说明。本标准规定的申路系统充许测试指令和有关测试数据债送到一个器件,从而充许读出送些报令的执行果。所有信总(指令、测试数据和测试结果)部以行格点传递。拨作序列应由-.个总线主控器控制,主控器可以是-台自动测试没备(A1E)或者一个与一杀品测试总践接口的器件,作为一个完整案统维护结构的一部分,控制是过对连技别率举线土控器的各种器件的测试方式选拆(TMS:和测试时钟(TCK)拍入施加的信号而获得的。队划始状态前起动,本标准规定的测试电陷紊统在切始状高下是待用的,一种央的操作序列如下.

适常,菜一步是把要完成这种特定操作的指令弱出行地畏人这个器件,本标准规定范避示遇拆是这样计的,指令估忌的串行传遵对些由滋指令制其操作的电踏缺并不即量的,加到这些块的指令以在移他逆(指令装入)案成时改变。一巨指令已经装入:就配些成选定测试电路予以前应,然而,在某些场合,在可以做出一种有享义的在应之前将数摄装人这定的测试电是必翌的,这些数据以和前而装人该指令的过理类假的方式带行地装入这个器,注声测试效批的传送对出我在测试电路系统中扩这条令并无影案、

中华人民共和国电子工业部1924--01994-12-01实施

SJ/T10566—94

台这条指令执行后,在需要的地方整带供给的数期,测试结果可通这将双据移出该器件到或通过总线土控器进行检查。

注意,在一测试操作但以不同的数据重其的圾仑,新测试效据可在测试结果移出时移人该器件,无需量新装入这条指令。圳试电略的操作可表似上述力式通过数入和执行芳千另外的指令维续进行以返函测试电路而结束,而且在需要的地方芯HE案统电露可返回其初始状态,2.2维装产品的测试应用

本条给出在删试个已组装产品(刻划一块印制电路板)的过程中本标规宗的逆界扫挡电路的应用概要。

2.2.1板测试月标

一套器件树成的任何产品的测试何题帮可分船为三个日标:证实每个器件家成共所要求的功能;证变各器件是以正确方式五相连接的;b.

c.证实在产品宁的各器件间正确的相车作用和该产品完成其前定的功能。这种办法是层次式的,它可以用于由崇威电路均成的印制电路板,州于山印制山龄校转成的系统或用由一较单的劝能模块性成的一个复杂奥成电路,为了简化这一计论,以后这种说明将然中到由一查数牢集成电路情成的已组装印制电断振的情视。在印制级,日标:和1通常是采用在线测试装大实现的,血目标则需要到能曾试,然而对于包含表面安教的互连术,在线测试技术就受到很大的收制,例如,使用针床央具和印制电路板上的微小型部件进行前靠接触的困期。测试访间只限于对正常的电略连接,伙有及少量专用划证点时,可接不违三个方法达对上述一个测试日标,对于日标,用干印制版级设计的染成电路的出售者会有这种器件的测试办法,这些器件可以在一台专用自动测试设备系统上测试或用埋藏在设计中的口测试过程进行测试,所采用的测试方法的信息通常器件购买者是得不的。非便有自测试操作方式,用户也会固得不到资料面不能用,印制极测试老的另外测试款据源可能随在规测试系统提供的器独测试数据赋者用户为购买的器件按收检验前开发的测试程,这种件一日组装到印制出路损上,测试间题如只限于该组装电路的止皆连接,这填任务可据较为复杂。如柔用的器件是克杂的,或者如果印制板设计者将馨件的基此连接接到固定电平感者器件引脚保持末连接状变则更加繁势,通常,以该器件在两离情况下进行测试的问样方法来测试它是不可能的,除非能将实现一户在线测试。为了保证能够使用内装测试装无,成者能够范t所先存在的测试码模式(restpattarn)就需要一台主机,它可以用来运教送往或来户各个器件边界的测试数据,固而如果这些器忙是迹立式的就可以测试飞门.这种土机也允许访间和控制器件的内装测试装置,逆界扫括知一系测试边向总线绩合起来就提供总样一种主机。本标准的口的是规定一种边界扫描结均.可采用这种结括作为采放电踏设计的标准功能部件从而能略在已组装印制电路板上或其方产品上建境所的洲试主机,2.2-2什公展边界扫描?

选界扫描技术就是紧验每个薪件引典附加::个修位奇存器级(位含在一个边齐扫描单元中).内而可以旧扫挡测试原理控制和规测器件边异上的信号。图1说明-…个边界扫指单元的典型实现,达种单为可用于境成电路的输入或辆出连接。收2

SJ/T T0586—·94

决于证到多路变换器的控制信号,数据可以由信号输入1(例如摘人引肥)装人扫播穿存器,或者这十寄存群动通过这个单元的伤号输出口(视如进人这个器件设让的核心),在后-…种常况下,提供第二个双稳(由输入时钟B控制),以保证该单元驱动稳出的信号在新数据对辅人时A移位进入该单元时保持起来(见第(率),送种双稳并不是所有场合筛要:但图1包括主以简化这神讨诊,

扫描辅日

信性确人

暂位等人

日期入

时钟A

…种拉界期芦单元

次界扫势单

风互谨

器统五透

图2一种可以边罚划摧的归制电路校设计向号编山

的事入

一个器片的别再用的这当边养扫带追元是百注的,从丽南晓这一计的边界形成一不替位奇存器链:面这条道路装备有占行输入与输山评接印话当的时钟与控制号.在-个点并十禁均业降组装的产品中行个器恒的界扫招惠存器可以出行还控起来联成·条址酒整个设计的单一通路,如图2所示,当外,个位的识计,可以包括若十条额文证界范迪路。如果州关建造个电路的所有件都有边习携守器,部么形成的再穿带个设计的串行通踏可以两种法便用

为了让许冲将件间的互连可以衡试,测试教措可以们进人和件输出引脚有关的SJ/10566—94

所有边界扫描单元和并行通过器件互连数人和输出引脚有关的那些单元,b,为了让这块板上的解件可以测试,当进行内都自测试时,逻界持描存器可用来作为两离芯片上系统超辑和由周围器件接收双的融励的一种手段,另外,如果边界扫摘尚存器尽适当设计的,它可以允许进行芯片上系就辑的一种有限慢递静测试,因为它允许测试数增传逆到该舒件并检克试结果,

这些测试能够通注使用边界扫描毒存器适到的面讨论的前两个目标。实际上,快用这种新存器进行的测试可以检测当前在载测试仪寻找的许多故阐,而无需广泛的针床访间。仍您保留款第三个目标…在功能上测试这神完整产品的操作,它可用一台功能通过可即)自动测试系统或者用一个殊统级自测试来完股。注意通过井行装入一个器件的输入和输出处的这些单元和移出这些结果+边界扫描奇存挚也提供“圾样\流过·器件的数据的手段而且不下扰读签器件或该已组装印制板的行为,这种操作方式对于设计调试和欲障诊断是有价值的,因火它允许控查这种测试系扰不能正带访间的连接:

2.3对其它目标的禅试应用

除了在测试包含多个器件的印制电路组件和其定产品中应用外,本标准规定的谢试逻也可用来提供对建造在舒件本身内的题困广泛的为了测试而设计的功能都件(deaignfar-tcatf比c9)的访问。这样的功能部件可以包括内部打描通路,自副试功能(例如,使用内装逻辑块观酒器

2.4本标准结构

按本标准规定进行的电路设计,想其技术规范闲有各个部分详图的说明案料并据供实现的实例,就查品理解前面已给出本标准对测试由许多策胶电路渠感的电子产品数字部分的应用撼述。

本标准以后各章包括有关持性和待殊功能部件的说明、其中包括2.4.1和2.4.2两类资料。

2.4.1规范

规范的各细月为靶则、推荐和许可,规则规定本标准的强制性方山,据于现则的录款具有“必须\一词。推再指出对寻求合事标准的设计的优秀实战,属于推养的条款具有“应”或“应该”词许可示出如何随够将选用的功能部件引入寻求将合本标准的设计中。这此功能部件将扩限本际准规定的测试电路系娆的应用,属于许可的条款具有“可以”或“够”一词,2.4.2说明

说明资粮附明要规定的特性或功能部件的必要性或者它们的用遍。这种资料包括说明本标据中这些规积的可能实现的简图。本标准的时录包括另一个可选用的实观例子,这种说明资料也涉及任开发本标准期间数出的设计决策。注:本协准中创括的说明再料只用于说明且的,并不规定一神优选的实测方法。2.5约定

在本标准中使洲下列约定:

S1/T 10566—94

,每十规范细目中的规,推和许可分别以一个母作标识,按字母履序连续排列,对每个规则、推荐或许可可以下列格式用.如:15.1.1C(i).其中,15.1.1为条数号,C为标认,)为选用项:

1,本标准规定的措令和状态名称以累体学表示&,居于本标准规定的测达数携寄存器的态和信号名称包含字符DR,而层于指令寄存能的包含字符IR,

d、处于低态有效的信号的名称用一个盛号作为最后享例如TRST*,e,便用正逆续约定,也就是一个说期1追号是运载量辑值号用的两个电压中比轻正的那个电压。

2.6术话

2.6.1有效的artive

当关享到一个速电平时(例低态有效)这个术语标志这一逐辑电平,借号置为该电平就遗成规庭的动作发生,当美系到辑出巫效时(例如,有效驱动),这个术语说一快态,贴的爵始千该状态就能够决定它车接的网结电压,2.6.2双而脚bidirecionall in

条既能吸动外部连费又能从外部连换收信孕的端件引脚,2.6.3内装逻辑块规器(BILBO)buitt in togicblock pbscrver(B[LBO)一种用了某些避式的口测试电路设计的基于移位存器的轨持。2-6,4询间blindinterragatlo

在未率步了解穿过问的持定解件的测试课辑操作的情说下,对一种装置(倒妞,器件识别商存器>的访问。

2.6.5旁路BYPASS

用宁本标准规是测试逻辑的一案规定指令(犯了,4),2-6-6板上芯片测试chp-on-boardlestiug在一个器件组矩在申制电路板就其它基底上后对家的测试。2.6.7时钟CLOCK

一种情号·在既和高遥抵电平(或反过亲)间的转变用来指示一个存储状态器件(比妞一个双偿或锁存器)何时可以进行操作。2.6.8外部调试EXTET

用于本标准规定测试逻辑的一亲规定指令史7.7),2.6.9下降沿lalliag edge

,.个从高遂电平到低电平的转变,在正逐辑中,一个从辑1到逻辑心的变化,2- 6. 10 商 high

用来运载一个单独信息位的两个电压中较高的那个电压。对于正逆辑,是逻辑1。2.6.11标识码IXCODE

周工本标评提定测试逻辑的一签规定指零(见17)2. 6. 12待用的 inactive

当关系到一个够出坚动器(例如,一个得用的驱动),这个术沿说明这一状志,驱动器处于该状态就不能决定它连按的网络电压。2.6.13输入引脚inputpin

SJ/T10566—94

一个从外部接接收借号的器件即。2.6.14指令ur

·个因行移人木标准规定的划试巡辉的二进制款据字,用以规亲随后发生的操作。2-6-15用部测试INTE

用于不标推规定测试逐辨的条规足指令(则7,8)2-6-16最低有效应(LSD)legtaignficnnl bit(LSB)在一个,“选制微字中代裳尽小数值的那一,对丁移位寄存靠,邮位在最靠近牢行摘出处,或者第一个要移出的位。一个二进制字或移位备在期的最低有效位编号为心:,26电平敏感满设(eeitiar:ig)

行控设计技术的一种变型,它产生无竞争的可测试数字电电路。2. 6. 18低0%

用半运载一个单减估良位的两个电压中较低的那个电压。对于正逻拇是逻辑,2.619展商有效位(MSB)nastRnificantbittMS)在:个二过制数字中代志地大数佐的那-位。对于移位寄存器,足离中行输出最远的那一位敢客是量心帮出的那一总,以一进逆制形式表示的逻辑值将最商有效位放在主边2G-2非时钟 nonclcck

一种行号,它在低和尚遵担电乎间转变时,不成在储状起器件的操作,这个率报电平只布时钟信号发生拍效时习是正要间。2.6.21给出引upup:

一个将信母驱动到外前迁控上的最件引期,2.6.22脚21

在案成中路和其安装的与志《到打印制电路板》之间形成的连接点对于封滋的号件,它是过数引脚:对于直按安装在菌底上的器件,它是连获盘。2.6.23深购源priescurce

在凸二个出也么供引脚烂引脚兼弃器件的冰况下,原始源是推出这种器偿型号的出告香。

2.6.2专洲ive

预定专供该器独也逆者使用的一仲设计待性。2.6.25公用mlic

在盗下教与图表中提诺斑料的一种设计待性,可由该留件购买者使月:2.6.26上升沿:ising edge

-个从低到高逆每由平的转变,对于正逻辑-·个从趣辑心到避解1的变化。2.6.27运行内装自试RVLIBJST

出十本环随规定的测试逆的条规定的指令(.?.9),2.6.28取样顶装入SAMPLE/PRELOAD承F本标准织患的测试理辑的一录独宽的措令(见7.6)。2.6-29扫描计xcandesign

一种设技术,它将移位寄存通踏引入效宁电电替中并及面改普它们的可测性,2-6.30描通路saraEall

通过用归描说计技术设计的一个电路的移位部存暨通路。2.6-37.饮源enlun

SJ/T10566--94

在若十出每者提供叫脚对引再兼容举件的情记下,二次源供应都是原始谦以外的件出者。

2.6.32选定的测试数据毫存selectedtes:detoregister当报供治测试运择的一杀指令的操作需一个测试致据讲存器时就迷定一个,2.6.33待征分折signatureanalysis一种用小将来自一个被测电路的迟母值输出序列无储成一个小位数的数据(特征)的技术,该散据与存储的效携比较会指出电路中存在或不存在故摩,2-F.34独立的测 staod-alnneterting在一个器件按装在一块印制报或其它基底上之前进行的·种测试.例妇使用ATE。2. 6.35固定型做障 grk-ar taal在遇辑电龄中一种避成一个信号连接固定在心或1的故床,不管驱动它的电路操作如何,2.6.36系统syetem

属干这个电降的其测试功能,

2.6.37系统逻频sysemlogc

专门用于实现该器件的非测试功能的任何连辑装配或在感兴趣时配宣起来以实现非测试功能的基些方而的任何逻抵装置。2.5.38系统引9ysiemria

一种器什引博,定谈逆到芯片上的离统逆来变用该逻带快送到它,2.6.39谢试收(TA)teatceesspc(A)本标准规定的测试行取!!(见第3章)。26.40测时钟TCK)1:k(TK)

本标推规定的TAP中包含的测试时钟输人引(见3.2)。26.41试数输)testdatanputD)

本标准规定的TAP中包含的测试数据箱入引脚(见3.4)。2.6.42试数热输出

一种器件输出引,其驱动可以是有效的或者待用的(例如:处工高阻航),3测试存取口

SJ/1056594

测试存单口(7P是一通用口,以提供对一不器件内装的许多试支持均能的访问,包指间本标雅规定的馈试逆辨,飞丧本标准规定的划试采辑所而的三个渐入连接和一个输出连接的最小两组成。一个选用的第四输大连接握供过本标准规定的测试逻辑的异步初始F.

3.1形成测试在股口的连据

3.1.1规范

a.TAP必动色括下例连报3.2.3.3.3.4机3.5中规定的>.TCK,TMS.FII利TDO.

.作为测试逆样内装动范部件内个结果.TA超制器在接通电源时小享位的场合+必须按照3.5中所定义极供一个TRST+摘人(见5.5)。C:所有T给人和拍出部必长对这器性专用湾情已就是就用的出再必须不用手在共日的》

3.1.2说明

专用TA连携是费要的,以便能账读间本标准企部强创性特性。32谢试时钟愉人(CK

TCK提供本标准规定的测试题步的时钟。3.2.1规范

测试量据中包指的存结裁态器件在加TK上的信号许止在心时必须无限期地特出们你状态

b、尚为对于许多薪件的TCK愉入可能是由一个单-的驱动器控制的、应该小心长出TCK渠供的负赖要尽可能小:

c,谢式没拼中包括的存储状声器件在加到TCK上的信亏停止在1时可以无限期地课持产们的状志,

3.2-2锐明

因为色合用心式输入,所总器件间的半行测式款据道路可以独立地由器规定的案统时钟使用,这器件和那一器件的系统时钟在瓶率上可以大不相间。它也,允许该器件进行系统探作的同时移动测试数据,募安尼一均能去支持一个希线系统监规的设计十他用TAP和测试数据寄序强。提供一个将立的时钟以保证色不欢变心片上累统逻辑状态的情况下可将测试整推传送例该芯片要出芯片送出来。如边界打挡寄存器在所有外境一,对即制板互速预试新可使到的诺,独立的时钟也趋重要的一一包括在一个强件中导出的系统时钟信号在其竺券件使用的情况。

内为在许多场合TCK将斗,个标准凸空比0%的口由时钟驱动,就可能有需要时钟停止一个周期的情说,一个子尺有存A工上专从后备存储器:例如:继盘)取测试教握时,因为其此试系统不旋月来在这独保作期间保持时钟运行。本标准要求在TCK可以无阻期地停小在(而不造成测试逻辑状志的任何改变。当工CK信号停止时,需要存请状恋器件保持它们的状态,便在时钟操作启动时测式宠啦可以绝续它的操性。作为-种选样,个SJ/T1056694

器件也可以许TC无限期地停止在I。3.3衡试式选泽愉入(TMS)

在1MS上接收的信导由TAP控问器评再以控划测试操作。3.3.1规范

在TMS山出我信号必须测试逆辑在TGK的上升沿取样a

b由TMS伊这的心路系统总须是这设计的,·个非驱动的愉人产生个等同于如上一个逻辑1的响应:

因为对许多器件的TS输入可以是小·个单·离动控制的,应该小心保证出.

了M提供的负载要尽能小,

因为包括规则3..:b.所以在个驱动TMS引脚场合让TAI控制端强制进人测试逻辑一复位(Tesr一nie一Rerer)控制等杰,这就保证个设计的上常操作可以继续而不受来凹测试退升的下扰(见5.3,对于品体算品休并逻抵(TT1.兼李的设计,可通过在该器件的1MS输入电路系就中包括--个上充电阻来满这-热州,在TM上出观的信号值品中划试逆辑作TK升沿职栏的,总线主控露(A工F,总线培制器等)将在TCK的下降消改变以连要群件的TMS输人的:求动信号,在木标准其它地方示出的波形反映出这种情况,

3.4测试数据输入(TPT)

测试逻辨在TDI1.换收车行谢试指令与数据:3.4.1规

3.在T上山现的信号必纳在TCK的上并收样选人测试举抖:山送的电路系统必测这样设个非驱动的输人产牛·个等同于那上·个调:的度

C.当数据存以TLI多动TD时在TDI.上接收的信号必纳在由指令选定测试效圾寄存器的长使谁乐的一乐教日的CK上升和下降沿后不赖倒地出现在TDO上。3.4.2说明

教据引脚(TT印TTX是为测试效据通过这个电路甲行信送而违备的,包括要不颜例地从明到传送粒据的费求,以简化在换印判电路核链接和本标兼穿的器件的操在TD1十出原的偿是在TCK的上记球到造的存(指含或测试数抵)中的,总规三控器(AI上,总线税制婴举)将在IK的不降沿改变坚动到一条行板级通路上第一器件工D1瘤入的信号。在本标准别的地方示品的该彦反映出这种惜况。因为包传规则3.4、1山,所以该核级行测试敢据尚陷中的踏放障造成-个规定的逻值移入测试起料,注意当达常数值移人指令寄存器时就会选定旁路许存器如挤准7.4中光一振讨论的),对下:T,落穿的设计,可通就士该器计的撤人路中包含一个1拉电阻米满足这一规则,

3.5测试款推筑出T0

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。