中华人民共和国电子行业军用标准FL5962

SJ20163--92

半导体集成电路

Ju8086型微处理器详细规范

Detail specification of Ju8086 microprocessorfor semiconductor integrated circuits1992~11-19发布

1993-05-01实施

中华人民共和国电子工业部批准1范围

1.1主题内容

1.2.适而范围

1.3分类

2引用文件

3要求

详细要求

设计、结构和外形尺寸

引线材料和涂爱·

电特性

电试验要求

微处理器指令系统…

徽电路组的划分

质策渠证规起

拉样和检验…

鉴定捡验

质量一致性检验

检验方法

5交货准备

5.1包装要求·

6说明事项

关于测试矢量的一般规定

订货资料

功能说明。符号和定义

替代性

TYKAONKACa-

中华人民共和国电子行业军用标准半导体集成电路

Ju8086型微处理器详细规范

Detail specification of Jμ8086 imicroprocessorfor semiconductor integrated circuits子范围

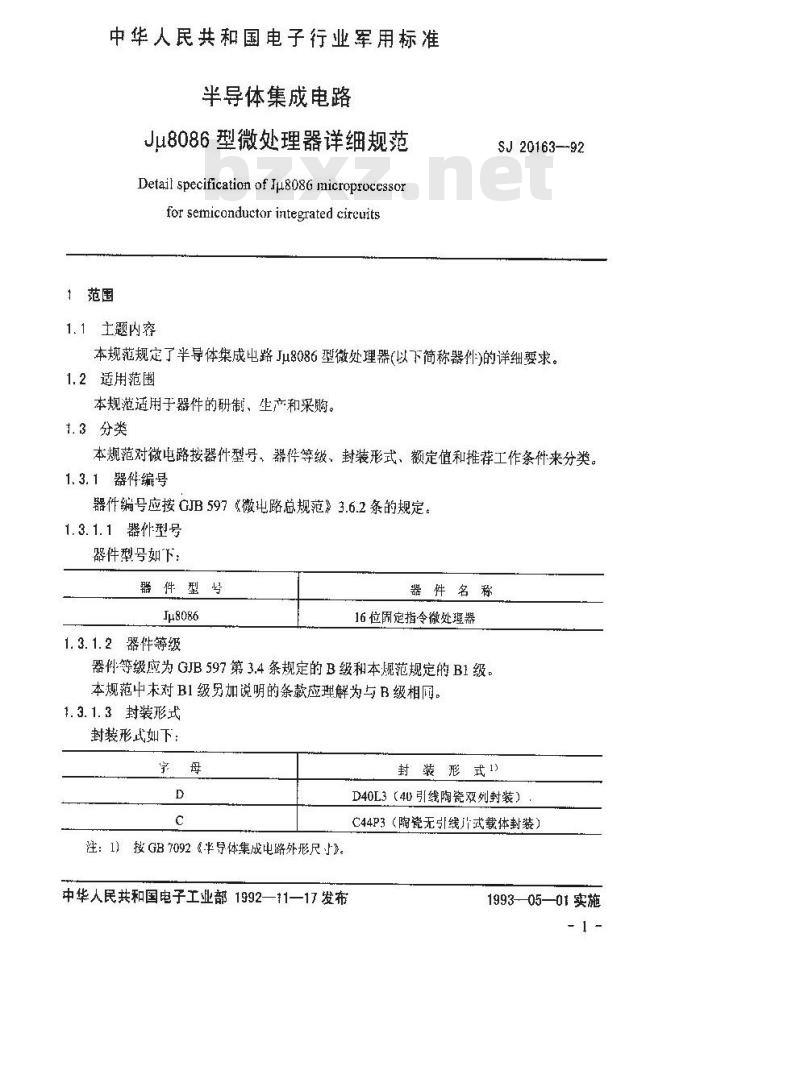

1.1±题内容

SJ 20163--92

本规范规定了半导体集成电路Ju8086型微处理器(以下简称器件)的详细要求。1.2适用范围

本规范适用于器件的研制、生产和采购。1.3分类

本规范对微电路按器件型号、器件等级,封装形式、额定值和推荐工作条件来分类。1.3.1器件编号

器件编号应按GJB597《微电路总规范》3.6.2条的规定。1.3.1.1器件型号

器件型号如下:

器件型号

Ju8086

1.3.1.2器件等级

器件名称

16位固定指令微处理器

器件等级应为GJB597第3.4条规定的B级和本规范规定的B1级。本规范中末对B1级另加说明的条款应理解为与B级相网。1.3.1.3封装形式

封装形式如下:

注:1)按GB7092《半导体集成电路外形尺寸》。中华人民共和国电子工业部1992—11—17发布封装形式1)

D40L3(40引线陶瓷双列封装)

C44P3(陶瓷无引线片式载体封装)1993—05—01实施

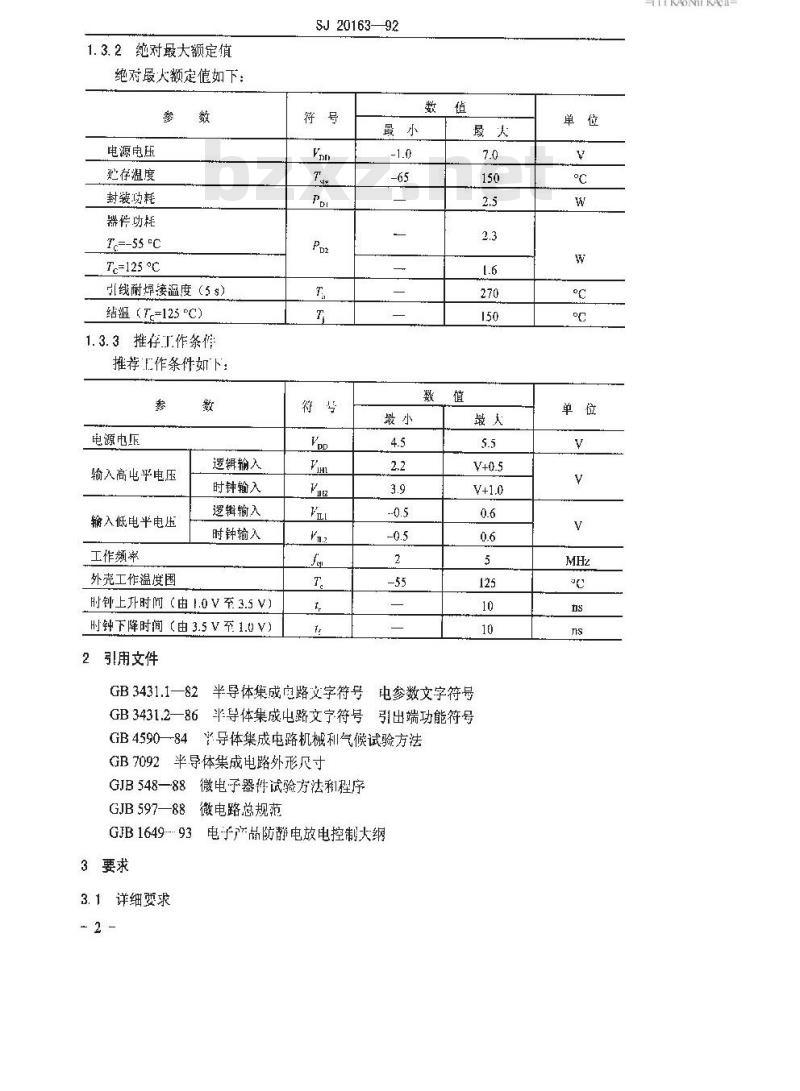

1.3.2绝对最大额定值

绝对最大额定值如下:

电源电压

北荐温度

封装功耗

器件功耗

Te=-55 -C

Te=125°c

引线耐焊接温度(5s)

结温(T=125°℃)

1.3.3推存工作条件

推荐作条件如下:

电源电压

输入高电平电压

输入低电平电压

工作频率

外壳工作温度围

逻辑输入

时钟输入

逻辑输入

时钟输入

时针上升时间(由1.0V至3.5V)时钟下降时间(由3.5V至1.0V)2引用文件

SJ20163—92

GB3431.1—82半导体集成电路文字符号电参数文字符号GB3431.2—86半导体集成电路文字符号引出端功能符号GB4590—84导体集成电路机械和气候试验方法GB7092半导体集成电路外形尺寸GJB548—88微电手器件试验片法和程序GJB597—88微电路总规范

GJB1649..93电子产品防静电放电控制大纲3要求

3.1详细要求

TTKAONKAa

SJ20163—92

各项要求应按GJB597和本规范的规定3.2设计、结构和外形尺寸

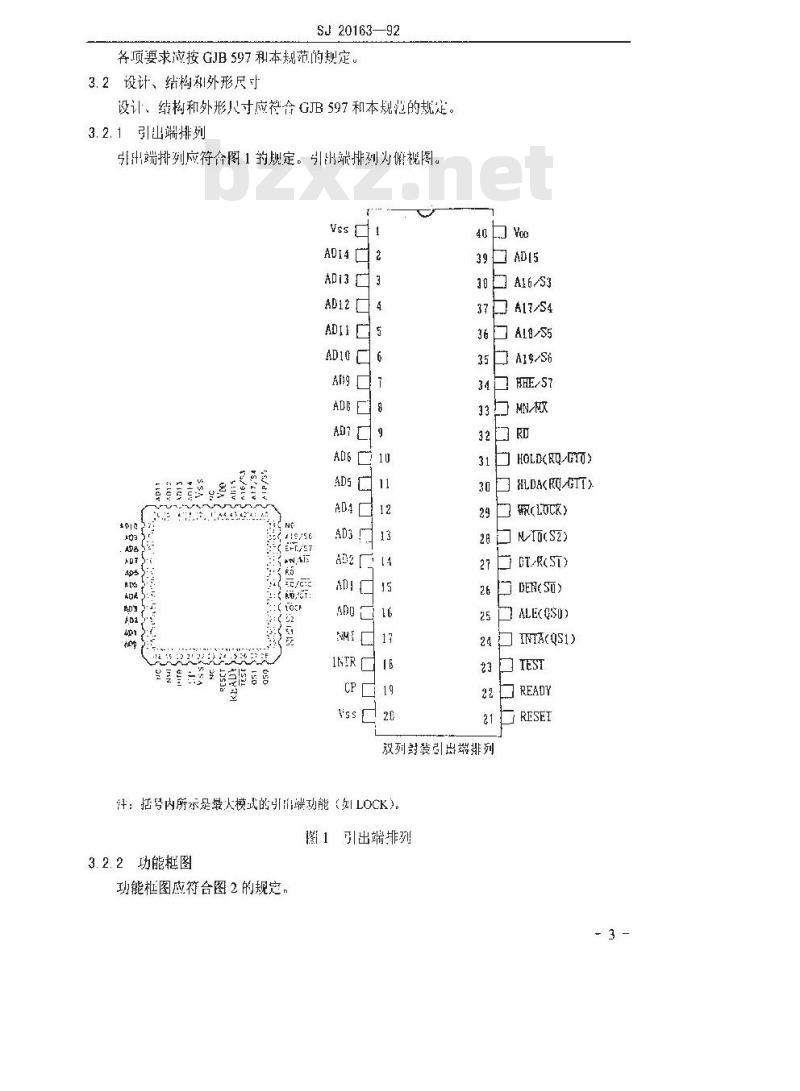

设计、结构和外形寸应符合GJB597和本规范的规定。3.2.1引出端排列

引出端排列应符合图1的规定。引出端排列为俯视图。Vss Www.bzxZ.net

EFL/57

( tocr

北更艾

全美YE食会

Vss 20

du Voo

■AD15

37 A17>54

AII>S5

A19-S6

口FES7

HOLDHLDA(RQGTT)

RCLOCK

DT-R(ST)

DEN( SU>

ALE(QSO)

双列对装引出端排列

洋:括号内所示是最大模式的引é端功能(刘LOCK)。图1引出端排列

3.2.2功能框图

功能图感箱合图2的规庭,

INTAQS1)

执行单元

寄存器组

数据指示器和

地趾寄存器

(8×16)

16 位算术逻辑

SJ20163—92

总线接口单元

再定位商存器组

殷寄存娶和

指令指示器

(5x16)

总线接口单元

6字节指令排队

控制和定时

←←香

RESET READY MN/MXV、VoD

图2功能框图

3.2.3功能说明、符号和定义

功能说明、符号和定义应符合本规范6.3条的规定。3.2.4封装形式

封装形式应符合本规范1.3.1.3条的规定3.3引线材料和涂覆

引线材料和涂覆应按GJB597第3.5.6条的规定。3.4电特性

BHE/S?

A16/53~A19/S6

ADD~ADI5

INTA、RD、WR

DTIR、DEN、ALE

>QS。、QS

TYKAOIKAca-

SJ 20163—92

出特性应符合表1的规定,者无其它规定,适合于全作温度范函。3.5电试验要求

各级器件的电试验要求应为表2所规定的有关分组,各分组的电测试按表3的规定。3.6微处理器指令系统

微处理器指令系统应按表4的规定。3.7标志

标志应按GJB597第3.6条的现定,3.8微电路组的划分

本规范所涉及的器件为第107微电路组(见GJB597附录E)。表1电特性

输入低电平电压(除

CP、MN/MX 外)

输入高电平电压(除

CP、MN/MX 外)

CP端输入低电电压

CP端输入高电电压

MN/MX端输入低电平

MN/MX端输入高电平

输出低平电压

输出高电平电压

电源电流

榆入低电平电流

(NMI、INTK、CP、

RESET READY.

TEST MN/MX)

输入高电平电液

(NMI、INTR、CP、

RESET READY.

TEST、MN/MX)

输入低电乎电流

(ADiI~ADI5)

翰入高电平电流

(ADO~-ADt5)

条秤3)

Ior=2.0 mA

采而图5负载

fan-—40U μA

Vop=4.5 V

采用图5负裁

Tc--55 °C

Vpu=5.5 V

Vpp=5.5 V

规范值

时序图

高阻态漏电流

[A/S、BHE/S7、RD、

DNE(SD)、DT/R(ST ),

M/10 (S2 )、WR (1.0CK ))

输入电容(除ADO~

AD15、丽/外的所

有入端)

输入/输出电容AD

AD15、颜/GT)

三态输出电容

[A/S、BHE/S7、RD、

DEN(SO)、DT/R(SI)

M/I0(S2)你R(LOCK )

时钟周期

时钟低电平时间

时高电平时问

数据建江时间

(到 CP下降沿)

数据保持时间

(从CP下降沿开始】

请求(RQ/GT)建立时间

(到 CP 上升沿)

状态有效延迟时间[从CP,

上升沿(S0~52)开始)

状态无效延迟时间[从 CP

下降沿(50~ S2)开始]

地址有效延迟时间[从CP

下降沿(AD0 ~ ADI5

A16/S3~A19/S6)开始】

控制有效延迟时间[从

CP 下降沿(B芷 /S7

QS1, QSO, LOCK )开始1

地址无效延退时间[从CP

下降沿(AD0 ~ AD15 、

A16/S3~A19/S6)开始

BHE /S7 无效延迟时间

(从 CP下降沿开始)

twrCE)

SJ 20163---92

续表1

条件3)

VDp=5.5 V

Var-0.45 V

Vpp=5.5 V

Var-2.4 V

Tsuuyi

a(CL-DX)

ISUINOLCHI

Ia.CH-SLi

Id cCE-SHi

fa(CL-AV)

1aicL-OSvi

aL-LUCKYA

faCL-AV)

farCL-BTIEV

采用图6负载

规范值

时序图

\, 8, 9,

10,11

10,11

7, 8, 9, 10

11,15

TTKAONKAa-

地址悬空延迟时间(从

CP下降沿开始)

数据有效延迟时间[从

CP下降沿(AD0~AD15)

状态有效延迟时间[从

CP 下降沿( /S7.

A16/S3~A19/S6)开始]

数据无效延迟时间[从

CP上升沿(AD(~AD15)

状态光效延迟时间[从

CP 上升沿(BHE/S7、

A16/S3~A10/S6)开始

R有效延迟时间(从CP

下降沿开始)

RD无效延迟时间(从CP

下降沿开始)

应答(/)有效延退

时间(从CP下降沿开始)

应答(R0/GT)无效延退

时间(从CP下降沿开始)

SJ20163—92

续表1

FdrCLA2)

taCLDV)

terCL-SV

T(CH-DZ)

FaiCH-sv)

ta(CL-RL

Fa(C1.-RH)

FarCE-GTL:

tarCL-GTH

条件3

采用图6负载

保持信号建立时间(到sLIHULDV-Cm)CP上开沿)

建立异步信号(NMI 、

INTR、TEST)所需时间

(到CP上升沿)

ALE脉宽

ALE有效延退时间(从

CP下降沿开始)

ALE无效延迟时间(从

CP 上升沿开始)

数据尤效到WR无效

(AD0~AD15)

WR、INTA有效延迟时

间(从CP下降沿开始)

TsuINMINCHS

aILSIY-CH

fwTALEH)

drCL-ALEH

(d(CH-ALEL)

LarH-n7)

fuCI-NTAL

规范值

7, 8、9

7, 8, 9

7,8,9

T/R、M/T有效廷

退时间(从CP上开

沿始)

控制光效延迟时间

(DEN. TNIA, WT)

(从CP下降沿开始)

HLDA 有效延迟时间

(从 CP下降沿开始)

DEV有效延迟时间

(从CP上升沿开始)

地址延退时带(从CP

下降沿开始)2)

就绪无效建立时间[到

CP(只姿到T2状态)

SJ 20163—92

续表1

条件3)

Ea(CH·DEV,

tacH-Mrvy

FaICI-DENH

fuCL-INTAH

areL-WH

TaiCL-HLDAV;

IarCH-DENE

fdicL-Av

+sUIREADYL-CL)

采用图6负载

规范值

汁:1)本裴中参数的序号对应的时序图中参数的编号是致的。最大

时序图

7,8,10

8,9,10

8, 9, 10

该延送是指请求/应答和HOLD/HLDA期间AD0~AD15、A19/S6~A16/S3、S0~S2、2)

RD、LOCK和BHE/S7信号线的延迅。3)若光其它规定,Vep=5.0V±10%:Tc-55--125°℃:Vs=0V。表2电试验要求

誠验要求

中南(老化前)电测试(方法5004)最终电测试)(方法5004)

A纠试验要求2)(方法5005)

B组 Vzap试验

C组终点电测诚(方法S005)

C组检验增加的分组

D组终点电测试(方法5005)

B级器件

分纽(现表3)

B1级器件

A1, A2, A3, A7, A8 A9,

AI, A2, A3, A4, A7, A8,

A9,A10,A11

见本规范4.5.3条

A2, A3,A8

不要求

A2,A8 (仅125 °C)

法:1)A1、A7分组要求PDA计算(见本规范4.2条)2) A4 分组(C、Cc)仅H于鉴定(见本规范 4.4. 1 条)。8-

A1. A2. A3,A7, A9

A1, A2, A3, A4, A7. A9

见本规范4.5.3条

A2,A8(仪125 °C)

A,All

A2,A8 (仅125°C)

TTKAONKAa-

分组1)

波形图

SJ20163—92

表 3A组电测试

被测端

DEN(SO)

DT/R(SI)

M/10($2)

WR(LOCK)

BHE/S?

A19/Sh

A18/S5

A17/S4

A16/S3

(1)除被测端外,其玄

端接域。

(2)测其中某一被测端

时,其端悬空。

(1) 测 AD4~AD14 被

测端时,除这些端外,

其它端接地。

(2) 测 ADO ~ AD3、

HLDA(RQ/GTI)

HOLD(RQ/GTO)

AD15被测端时,除这

些端外,其它端接地。

(3)测其中某一被翘端

时,尤另外说明的其

它被测端悬空。

(1)(17、18、[9)端基

(2)测其中某被测端

附时、除该端和(17、18,

19)端外,其它端接

测其中菜一被测端

时,该端接0.45V,

Von=5.5 V, Vss-0 V.

其它端悬空。

测其亨某一被測端

时,该端接5.5V.

Vpn-5.5 V, Vss-0 V.

其它端悬空。

规范值1>4)

最小「最夫

分组1

- 10 -

波形图

DEN(SO)

DT/R(S1)

M/10($2)

WR(LOCK)

BHE/S?

A19/S6

A18/S5

A17/S4

A16/S3

SJ 20163--92

续表3

(1)时钟脉冲电平在

0~0.4V之间#

(2)测某“ 被测端

时,该端接0.45 V,

Ypp=5.5 V, (1, 17.

18、20、21、22、23

33)端接地,其它端悬

(1)时钟脉冲电平在

0~0.4之间;

(2)測某一被测端

时,该端接5.5V,Vpp=

5.5 V, (1、17、18、

20、21、22、23、33)

端接地,其它端悬

1)时钟脉冲电半在

00.4 V之间:

(2) 测某一被测端

时:该端接 0.45 V,

Vpp=5.5 V, (22、31、

33、)端接 3 V, (1~

18、20、21、23、39)

端接地,其它端悬

规范值1>4

最小最大

-1010μA

TTTKAONTKAca-

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。

✕

✕