SJ 20758-1999

基本信息

标准号: SJ 20758-1999

中文名称:半导体集成电路CMOS门阵列器件规范

标准类别:电子行业标准(SJ)

英文名称: Specification for semiconductor integrated circuit CMOS gate array devices

标准状态:现行

发布日期:1999-11-10

实施日期:1999-12-01

出版语种:简体中文

下载格式:.rar.pdf

下载大小:810868

标准分类号

中标分类号:>>>>L5962

关联标准

出版信息

出版社:电子工业出版社

页数:19页

标准价格:18.0 元

出版日期:1999-11-01

相关单位信息

起草人:毕思庆、王连友

起草单位:电子工业部第四十七研究所

发布部门:中华人民共和国信息产业部

标准简介

本规范规定了半导体集成电路CMOS型门阵列器件(以下简称器件)的详细要求。本规范适用于器件的研制生产和采购。 SJ 20758-1999 半导体集成电路CMOS门阵列器件规范 SJ20758-1999 标准下载解压密码:www.bzxz.net

标准图片预览

标准内容

中华人民共和国电子行业军用标准FL5962

SJ20758—1999

半导体集成电路

CMOS门阵列器件规范

Semiconductor integrated circuitsSpecification for COMS gate array devices1999-11-10 发布

1999-12-01实施

中华人民共和国信息产业部批准1范围

1.1主题内容

1.2适用范围.

1.3分类

绝对最大额定值

1.5推荐T作条件

2引用文件

详细要求

用户设计规范要求

封装形式

设计、结构和外形尺寸

引线材料和镀涂

电特性

也试验要求

附加生产线认证要求

功能延迟模拟

版图检查

电源线的模拟(适用时)

修改已鉴定合格软作创的程序

4质量保证规定

抽样和检验

鉴定检验

质量一致性检验

检验方法

5交货准备

包装要求

说明事项

6.1订货资料

缩写词、符号和定义

替代性

6.4操作

iKAoNrKAca-

1范围

中华人民共和国电子行业军用标准半导体集成电路bZxz.net

CMOS门阵列器件规范

Semiconductor integrated circuitsSpecificationfor CMosgatearraydevices1.1主题内容

SJ 20758—1999

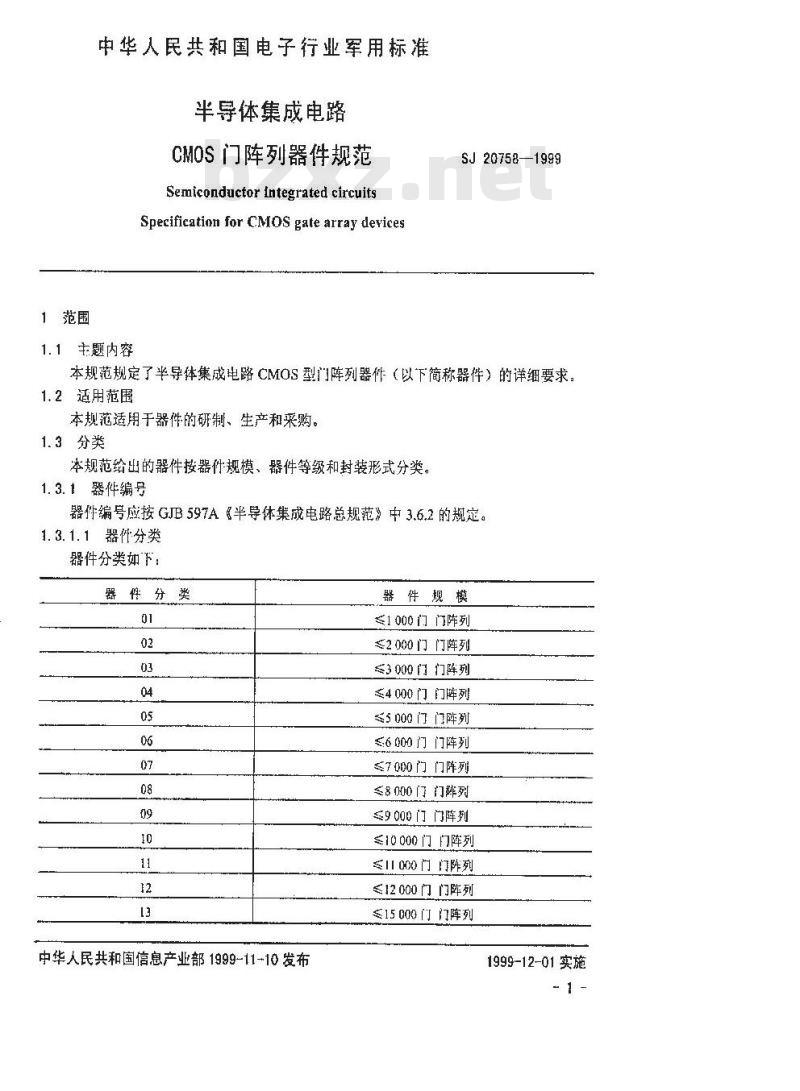

本规范规定了半导体集成电路CMOS型门阵列器件(以下简称器件)的详细要求。1.2适用范围

本规范适用于器件的研制、生产和采购。1.3分类

本规范给出的器件按器竹规模、器件等级和封装形式分类,1.3.1器件编号

器件编号应按GJB597A《半导体集成电路总规范》中3.6.2的规定。1.3.1.1器件分类

器件分类如下:

器件分类

中华人民共和国信息产业部1999-11-10发布器件规模

≤1000门门阵列

≤2 000门门阵列

≤3 000 门 门阵列

≤4 000门门阵列

S5 000门门阵列

≤6000门门阵列

≤7000门门阵列

≤8 000门门列

9000门门阵列

≤10000门门阵列

≤ 000门门阵列

≤12000门门阵列

≤15000门门阵列

1999-12-01实施

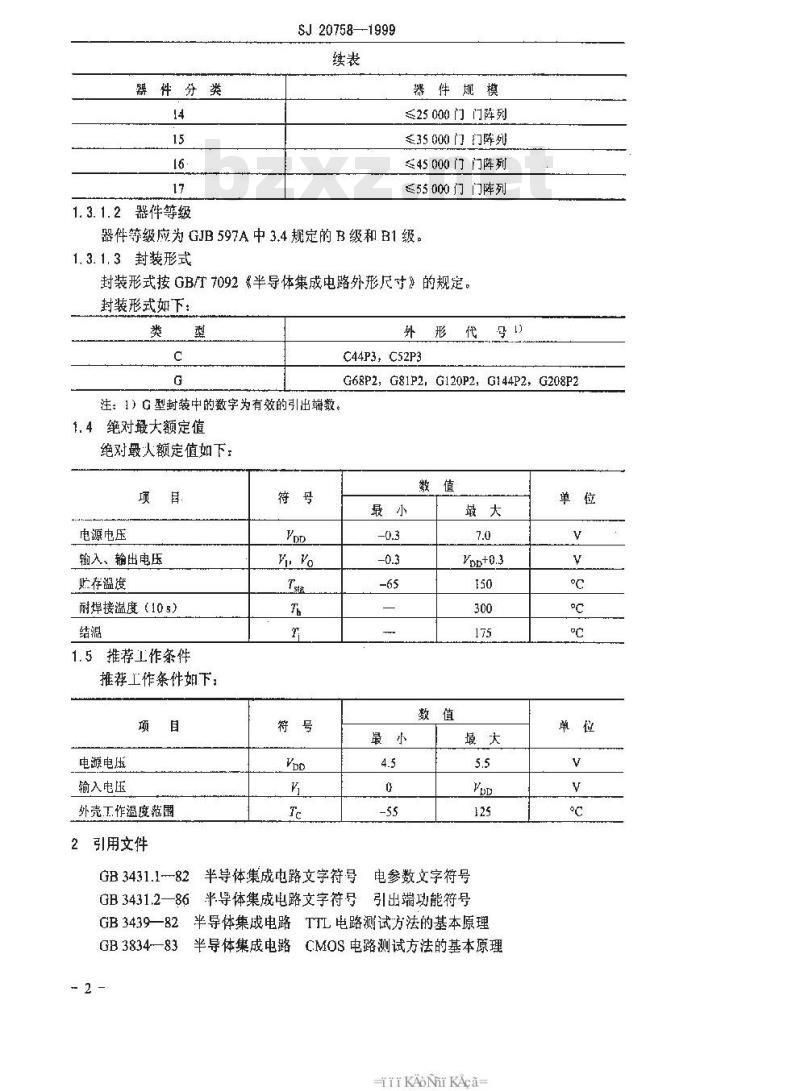

器件分类

1.3.1.2器件等级

SJ 20758--1999

器件规模

≤25 000门门阵列

≤35000门门阵列

≤45000门门阵列

≤55000门门阵列

器件等级应为GJB597A中 3.4规定的B级和B1级。1.3.1.3封装形式

封装形式按GB7092《半导体集成电路外形尺寸》的规定。封装形式如下:

注:1)G型封装中的数字为有效的引出端数,1.4绝对最大额定值

绝对人额定值如下;

电源电压

输入、输出电压

贮存温度

耐焊接溢度(10s)

1.5推荐工作条件

推荐工作条件如下:

电源电压

输入电压

外壳工.作温度范围

2引用文件

外形代

C44P3,C52P3

G68P2, G81P2, G120P2, G144P2, G208P2数值

GB3431.1-82半导体集成电路文字符号电参数文字符号GB3431.2一86半导体集成电路文字符号引出端功能符号GB3439—82半导体集成电路TTL电路测试方法的基本原理GB3834-83半导体集成电路CMOS电路测试方法的基本原理- 2 -

KAoNrKAca-

SJ 20758---1999

GB/T7092-93半导体集成电路外形尺寸GB/T15650—1995半导体集成电路系列和品种CMOS门阵列电路系列的品种GJB548A—96微电子器件试验方法和程序GJB597A—96半导体集成电路总规范GJB1208—91微电路的认证要求

3要求

3.1详细要求

各项要求应按 GJB 597A 和本规范的规定。3.2订购方设计规范要求

下列项目必须由订购方作为规范的一部分提供给承制方。3.2.1引出端排列和用途。

3.2.2封装类型从承制方提供的封装形式中选择(见1.3.1.3)。3.2.3功能框图。

3.2.4功能说明、符号和定义。

3.2.5逻辑图。

3.2.6引出端功能说明。

3.2.7电路图

电路图应符合GB/T15650的规定。3.2.8测试失量

测试矢量至少必须检测所有可测的固定“0”态故障和固定“1”态故障的百分之力十五。

3.2.9器件电特性

器件电特性应包括直流参数(最低要求见本规范表1)、交流参数和交流关键路径:可从承制方的数据表中选择。电特性适用于推荐的外壳T.作温度范围。3.2.10时序图

时序图应表示出所有输入和输出信号间严格的相互关系。时序图由一个或多个图组成,用来表示二个或多个信号之间严格的相互关系。象建立时间和保持时间这类参数的时序要求也应表示出来。

3.2.11老炼电路

老炼电路如图1所示。

3.2.12最大功耗

设计应符合最大功耗要求。

3.3封装形式

封装形式应符合本规范1.3.1.3的规定。3.4设计,结构和外形尺寸

设计、结构和外形尺寸应符合GJB597A和本规范的规定。3.4.1粘片材料

允许使用含银玻璃(银浆)芯片粘接材料。3.5引线材料和镀涂

SJ 20758-1999

引线材料和镀涂应按GJB597A中3.5.6的规定。3.6电特性

承制方应向鉴定机构提交一份数据表,详细说明待鉴定的门阵列系列或品种。这份数据表应包括所有的直流参数,功能和交流参数,以及与承制方有关而设计师也要求考虑的任何其他数据。承制方的所有器件必须满足表1中的参数极限值。所有电特性适用于推荐的外壳工作温度范围。【承制方的标准评价电路(SEC)(见4.3.2.2)的电特性应符合订购方设计规范的规定。]

3.7电试验要求

各等级器件的电试验要求,应为本规范表2所规定的有关分组。每个分组的电试验在订购方设计规范中和在承制方SEC的规范中说明。电试验要求至少应满足本规范图2利表3的要求。

3.8标志

标志应按GJB597A中3.6的规定:订购方设计规范的编号应由承制方加在标志上。3.8.1抗辐射总剂量标志

抗辐射总剂量标志应按GJB597A中3.6.2.4的规定,3.9附加生产线认证要求

除GJB1208的要求外,还应符合GIB548A中方法5010A附录A中A1.1的要求。3.10功能延迟模拟

应符合GJB548A中方法5010A附录A中A1.2的要求。3.11版图验证

应符含GJB548A中方法5010A附录A中A1.3的要求。3.12电源线的模拟(适用时)

应符合GJB548A中方法5010A附录A中A1.4的要求。3.13修改已鉴定合格软件包的程序承制方应向鉴定机构提交一个验证程序,用于验收已鉴定合格的软件包的修改和修订版。对于接收/拒绝修改和修订内部或商用软件包的过程,这个程序应简述其方法,并提供有关使用过程的测试说明。此要求仅适用于承制方在门阵列设计过程中所用的软件包。

表1电特性

输入正箍位电压

输入负箱位电压

输出高电平电压

诺无其他规定,-55℃≤T≤125℃Vrp=5 V+10%)

Vpp接地,被测输入端 Ik=I mA。测所有输入端

Vss接地,被测输入ik=-1 mA。

测所有输入端

TTL接:loH -2 mA

CMOS 接T:JoH ≤-1 μA

极限值

接承制方数据

接承制方数据

TKAoNrKAca-

输出低电乎电压

输入高电平电压

输入低电平电压

输入高电平电流

轮入低电平电流

输出高阳态高电平电流

输出离阻态低电平电流

静态电源电流

输入电容

输出电容

中间(老炼前)电测试

中间(老炼后)电测试

最终电测试

A纽检验电测试

B组终点电测试

C组终点电测试

D纽终点电测试

SJ 20758--1999

续表1

(若无其他规定,-55°℃≤T≤125°℃Vpp*=5 V±10%)

TTL 接: IoL =2.4 mA

CMOS 接口:uL IμA

TTL 接口

CMOS接

TTL接口

CMOS接口

Vo-Yss

仅适用无上拉或下拉的

仅适用无止拉或下拉的

F1 MH., T. -25 °℃

f-1 MHz, Tc-25°C

表2电试验要求

分组(见表3)

极限值

按设计规定

变化量极限

Al, A2, A3, A7, A8a, A8b, A9, At0, A11Al, A2+ A3+ A4, A7, A8a, A8b, A9, A10, A11Al

注:1)该分组要求PDA计算(见本规范4.2)。4 2)

2)老炼和寿命试验要求的变化壁(4)测量只适用于A2分纠,变化鼠极限按本规范4.5.2的规定。

引用标准

GB3834

GE3439

GB3439

SJ 20758-1999

表3电测试

(诺无其他规定,GND=0V,Te=25°C)Vep 接地、被测输入端 Iik =1 mA。测所有输入端

Vs接地,被溅输入端 Iik=1 mA。测所有输入端

V=4.5 V,测所

有适用的瓣出端。

Ypp=4.5 V, 所

有适用的输出端。

TTL: IoH *-2 mA

CMOS: JoH ≤-1 μA

TTL: ToL -2.4 mA

CMOS: JOL SIμA

Vpp-5.5 V, V'l=5.5 V,

测所有输入端。

YDD-=5.5 V, V'=0 V,

测所有输入端。

Von=5.5 V, Yo-Ved*

测所有输出端。

Vpp=5.5 V, Vo-0 V,

测所有输出端:

仅适用无上拉或

下拉的器件

仅适用无上拉或

下拉的器件

Vpp-5.5 V,测 Vpp端.

Tc=125°C,所有参数、条件和规范值同A1分组。7。--55°C.所有参数、条件和规范值间 A1 分组。G

F-1MHz,溉所有输入端对 GND的电容。f1 MHz,测所有输出端对 GND 的电容。Ypp=4.5V:按设计性能:符合用户设计规范要求。见图2.T=125\C,其他同A7分组。

Tc --55 °C,其他同 A7 分组

Yop*4.5V。按设计性能:符合用户设计规范要求。见图2。Tc-125°C,其他同A9分组,

Tc--55\C,其他同 A9 分组。

注:1)若被测的某一端是专门设计的,必须在用户设计规范中说明。极限值

「最大

按承制方数据

按承制方数据

按设计规定

2)实现功能和开关特性检测的测试失量是专门设计的,必须包含在户设计规范中。关量系统必须符合本规范3.2.8的要求。极限值在用户设计规范中规定。4质量保证规定

4.1抽样和检验

除本规范另有规定外,抽样和检验程序应按GJB597A和GJB548A方法5005A的规-6-

KAoNrKAca-

4.2筛选

SJ20758—1999

在鉴定检验和质量致性捡验之前,全部器件应按GJB548A方法5004A和本规范表4的规定进行筛选。

表4筛选程序

若无其它规定,表中采用的方法系指GJB548A的试验方法。筛选项日

内部目检(封装前)

稳定性烘焙

(不要求终点电测试)

温度循环

恒定加速度

中间(老炼前)电测试

中间(老炼后)电测试

允许的不合格品率(PDA)

及其计算

最终电测试

粗检漏

外部目检

鉴定和质量一致性检验的试

验样品抽取

4.3鉴定检验

4. 3. 1鉴定检验

条件和要求

试验条件B

试验条件C

(150 °℃, 24 h)

试验条件 C

试验条件DY1方向

本规范A2分组

试验杂件 A

125 °℃, 160 h

试验条件D

125°℃,160 h

本规范A2分组

和表104极限

10%。当不合格品率

不翻过20%时,可重

新提交老炼,但只允

许一次。

本规范A1,A2,A3.

A4, A7 A8a, A8b.

A9, A10. A11 分组

试验条件:A1或A2

试验条件:CI或 C2

试验后进行目检,引线断落、外壳破裂、封盖脱落为失效。

用4极限值计算 PDA 时,要求

记录 Iops值。

采用本规范图1所示的电路。可

选取静态、动态老炼的其中一种方式。

用老炼失效数(超过42分组极

限值或超过4极龈值的器件)除

以提交老炼的器数即为

PDA。不大于规定的 PDA 时,

则该批应接收。

本项筛选后,若引线镀涂改变或返工,则应再进行 A1 分组测试鉴定检验应按GJB597A中4.4的规定。所进行的检验应符合GJB548A方法5005A-7 -

SJ 20758—1999

和本规范A、B、C、D和E组检验(见本规范4.4.1~4.4.5)的规定。另外,下述5个鉴定阶段应该用确定的鉴定媒体来完成。4.3.2鉴定阶段和媒体

鉴定阶段

工艺监控和稳定性

工艺可靠性

宏单元设计和模拟

CAD布线和布线后模拟

设计检查软件验证

鉴定媒体

I.艺监控图形(PM)

标准评价电路(SEC)

宏单元测试芯片图形

门阵列的测试图形标准

承制方的试验情况

宏单元设计和模拟的鉴定,以及CAD布线和布线后模拟应以承制方的设计、布局和布线的能力为基础,并且承制方器件的实测性能特性(如传输延迟、上升和下降时间、驱动特性、触发电平等)应在模拟的性能特性极限值之内(见4.3.2.4)。YD

1op/2~YpD

注:①对于静态老炼,所有输入端道过电阻接Ppp,输出为开路或通过电阻连接到Vpp12~Vpp电阻R=6802~47k2,实际阻值应反映出最严的负载条件。若输出为开路,则输出端电阻可以任选。

②对于动态老炼,所有输入端通过电阻并连到时钟脉冲(CP)上,输出端通过电阻连接到Vop/2+0.5V。输入端电阻R=680247k2,输出端电阻R=1k2±5%输入借号要求,方波:占空比为50%±15%:频率fcp=100kHzt50%幅度:Vi-4.5 V~Ypm Vu=0±0.5 V.转换时间≤0.5 μs。? Vpn=5.0 V±0.5 V.

④}一输入端;0输出端:N(M)一最大编号的输入(输出)端。③在多电源端或多块端的情况下,所有的电源或地端都应连接到与其相适应的电平上。③引出端符号由用户确定。

图1静态、动态老炼和稳态寿命试验电路图8-

TTTKAONrKAca

兰态输出测试电路图

c.波形图

SJ20758--1999

标准输出测试电路图

测试点

注:①C=50pF±10%,包括探头和夹具电容。器件

一测试点

②输入脉冲特性:4≤6ns:F1MHz;占空比:50%。③所有不用的输入端连接到Ypp或GND。@ IThli- ttHL2* tThLi tTlh2- Itlhi= ITlho③当逃行功能测试和所有交流测试时(输出允许测试除外),S1闭合。对于ipzH测试,当S2打并时,S1和S3闭合。对于tpzL测试,当s3打并时,SI和S2闭合。①对\三态输出,R,=1kQ+10%。对-F非三态输出,Rz由在VoH=2.4V条件下的lon决定。③R,由Yn-0.05V时的loL(最小值)减去通过R到地的电流决定,图2开关测试电路和波形图

4.3.2.1T.艺控制和稳定性

SJ 20758—1999

直流参数的工艺控制和稳定性必须通过承制方和工艺监控图形(PM)米证明。为了直流工艺参数(承制方可以选择是否包括交流参数)的测试,PM(或专门插入或放置在划片槽中)可被设计成晶片形式或封装好的器件形式。PM设计在鉴定之前应送交鉴定机构批准,并且至少包括下列结构:a.N沟器件(最小结构)

b,P沟器件(最小结构)

N沟器件(大器件)

P沟器件(大器件)

薄层电阻测试结构

金属台阶分布结构

场阅值器件

h.金属间氧化物完整性结构

连接链(长度要足以代表接触电阻)(1)金属到多晶(适用时)

(2)金属1到金属2(适用时)的通道电阻。(3)反相器链(用于交流测试:由承制方定)。(4)金属到扩散层(适用时)。为了鉴定,应測试最少 3个不同批(每个晶片至少4个PM)的 PM,以保证建立有效的统计数据,并以此为依据判断承制方的工艺是否稳定和受控。可采用最近批的历史数据来满足这个要求(由承制方选择)。4.3.2.2工艺可靠性

可采用SEC(标准评价电路),来鉴定工艺可靠性,SEC设计应包括从3.2.1~3.2.1C所述的基本信息,在使用承制方的订购方设计规范之前,应提交给鉴定机构批准。它的制造工艺与生产和本规范的任何专用门阵列器件的制造工艺相同。SEC应设计成能对底层设计(扩散等)的可靠性及设计规则最坏情况条件进行评价。设计应利用宏单元库并形成振荡回路以及各种测试结构,这些测试结构在可靠性寿命试验中,可以检测金属与金属间短路或开路,高的通孔电阻及介质针孔。SEC应在最大规模(即器件分类中有最大门数的器件,若适用时其门阵列的封装应有最多的引出端数)的器件上实现。承制方的门阵列系列中有最多引出端数面有较少门数的器件品种或有较少引出端数较少门数的器件品种的鉴定通过扩展的方式进行(见4.3.3)。对于下列(4.4.1,4.4.2,4.4.3,4.4.4)电测试来说,SEC也是主要的鉴定媒体。对于承制方的SEC求说,测试极限值在订购方设计规范中规定(对于直流参数的最低要求,见本规范表1)。每个分组的电测试按表3的规定进行。当对SEC进行寿命试验时(见4.4.3),应适用于静态偏置老炼。4.3.2.3宏单元设计和模拟的鉴定应符合GJB548A中方法5010A附录A中A1.5的要求。4.3.2.4CAD布线和布线后模拟

应符合GJB548A中方法5010A附录A中A1.6的要求。4.3.2.5设计检查软件的验证

TTTKAONrKAca-

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。

SJ20758—1999

半导体集成电路

CMOS门阵列器件规范

Semiconductor integrated circuitsSpecification for COMS gate array devices1999-11-10 发布

1999-12-01实施

中华人民共和国信息产业部批准1范围

1.1主题内容

1.2适用范围.

1.3分类

绝对最大额定值

1.5推荐T作条件

2引用文件

详细要求

用户设计规范要求

封装形式

设计、结构和外形尺寸

引线材料和镀涂

电特性

也试验要求

附加生产线认证要求

功能延迟模拟

版图检查

电源线的模拟(适用时)

修改已鉴定合格软作创的程序

4质量保证规定

抽样和检验

鉴定检验

质量一致性检验

检验方法

5交货准备

包装要求

说明事项

6.1订货资料

缩写词、符号和定义

替代性

6.4操作

iKAoNrKAca-

1范围

中华人民共和国电子行业军用标准半导体集成电路bZxz.net

CMOS门阵列器件规范

Semiconductor integrated circuitsSpecificationfor CMosgatearraydevices1.1主题内容

SJ 20758—1999

本规范规定了半导体集成电路CMOS型门阵列器件(以下简称器件)的详细要求。1.2适用范围

本规范适用于器件的研制、生产和采购。1.3分类

本规范给出的器件按器竹规模、器件等级和封装形式分类,1.3.1器件编号

器件编号应按GJB597A《半导体集成电路总规范》中3.6.2的规定。1.3.1.1器件分类

器件分类如下:

器件分类

中华人民共和国信息产业部1999-11-10发布器件规模

≤1000门门阵列

≤2 000门门阵列

≤3 000 门 门阵列

≤4 000门门阵列

S5 000门门阵列

≤6000门门阵列

≤7000门门阵列

≤8 000门门列

9000门门阵列

≤10000门门阵列

≤ 000门门阵列

≤12000门门阵列

≤15000门门阵列

1999-12-01实施

器件分类

1.3.1.2器件等级

SJ 20758--1999

器件规模

≤25 000门门阵列

≤35000门门阵列

≤45000门门阵列

≤55000门门阵列

器件等级应为GJB597A中 3.4规定的B级和B1级。1.3.1.3封装形式

封装形式按GB7092《半导体集成电路外形尺寸》的规定。封装形式如下:

注:1)G型封装中的数字为有效的引出端数,1.4绝对最大额定值

绝对人额定值如下;

电源电压

输入、输出电压

贮存温度

耐焊接溢度(10s)

1.5推荐工作条件

推荐工作条件如下:

电源电压

输入电压

外壳工.作温度范围

2引用文件

外形代

C44P3,C52P3

G68P2, G81P2, G120P2, G144P2, G208P2数值

GB3431.1-82半导体集成电路文字符号电参数文字符号GB3431.2一86半导体集成电路文字符号引出端功能符号GB3439—82半导体集成电路TTL电路测试方法的基本原理GB3834-83半导体集成电路CMOS电路测试方法的基本原理- 2 -

KAoNrKAca-

SJ 20758---1999

GB/T7092-93半导体集成电路外形尺寸GB/T15650—1995半导体集成电路系列和品种CMOS门阵列电路系列的品种GJB548A—96微电子器件试验方法和程序GJB597A—96半导体集成电路总规范GJB1208—91微电路的认证要求

3要求

3.1详细要求

各项要求应按 GJB 597A 和本规范的规定。3.2订购方设计规范要求

下列项目必须由订购方作为规范的一部分提供给承制方。3.2.1引出端排列和用途。

3.2.2封装类型从承制方提供的封装形式中选择(见1.3.1.3)。3.2.3功能框图。

3.2.4功能说明、符号和定义。

3.2.5逻辑图。

3.2.6引出端功能说明。

3.2.7电路图

电路图应符合GB/T15650的规定。3.2.8测试失量

测试矢量至少必须检测所有可测的固定“0”态故障和固定“1”态故障的百分之力十五。

3.2.9器件电特性

器件电特性应包括直流参数(最低要求见本规范表1)、交流参数和交流关键路径:可从承制方的数据表中选择。电特性适用于推荐的外壳T.作温度范围。3.2.10时序图

时序图应表示出所有输入和输出信号间严格的相互关系。时序图由一个或多个图组成,用来表示二个或多个信号之间严格的相互关系。象建立时间和保持时间这类参数的时序要求也应表示出来。

3.2.11老炼电路

老炼电路如图1所示。

3.2.12最大功耗

设计应符合最大功耗要求。

3.3封装形式

封装形式应符合本规范1.3.1.3的规定。3.4设计,结构和外形尺寸

设计、结构和外形尺寸应符合GJB597A和本规范的规定。3.4.1粘片材料

允许使用含银玻璃(银浆)芯片粘接材料。3.5引线材料和镀涂

SJ 20758-1999

引线材料和镀涂应按GJB597A中3.5.6的规定。3.6电特性

承制方应向鉴定机构提交一份数据表,详细说明待鉴定的门阵列系列或品种。这份数据表应包括所有的直流参数,功能和交流参数,以及与承制方有关而设计师也要求考虑的任何其他数据。承制方的所有器件必须满足表1中的参数极限值。所有电特性适用于推荐的外壳工作温度范围。【承制方的标准评价电路(SEC)(见4.3.2.2)的电特性应符合订购方设计规范的规定。]

3.7电试验要求

各等级器件的电试验要求,应为本规范表2所规定的有关分组。每个分组的电试验在订购方设计规范中和在承制方SEC的规范中说明。电试验要求至少应满足本规范图2利表3的要求。

3.8标志

标志应按GJB597A中3.6的规定:订购方设计规范的编号应由承制方加在标志上。3.8.1抗辐射总剂量标志

抗辐射总剂量标志应按GJB597A中3.6.2.4的规定,3.9附加生产线认证要求

除GJB1208的要求外,还应符合GIB548A中方法5010A附录A中A1.1的要求。3.10功能延迟模拟

应符合GJB548A中方法5010A附录A中A1.2的要求。3.11版图验证

应符含GJB548A中方法5010A附录A中A1.3的要求。3.12电源线的模拟(适用时)

应符合GJB548A中方法5010A附录A中A1.4的要求。3.13修改已鉴定合格软件包的程序承制方应向鉴定机构提交一个验证程序,用于验收已鉴定合格的软件包的修改和修订版。对于接收/拒绝修改和修订内部或商用软件包的过程,这个程序应简述其方法,并提供有关使用过程的测试说明。此要求仅适用于承制方在门阵列设计过程中所用的软件包。

表1电特性

输入正箍位电压

输入负箱位电压

输出高电平电压

诺无其他规定,-55℃≤T≤125℃Vrp=5 V+10%)

Vpp接地,被测输入端 Ik=I mA。测所有输入端

Vss接地,被测输入ik=-1 mA。

测所有输入端

TTL接:loH -2 mA

CMOS 接T:JoH ≤-1 μA

极限值

接承制方数据

接承制方数据

TKAoNrKAca-

输出低电乎电压

输入高电平电压

输入低电平电压

输入高电平电流

轮入低电平电流

输出高阳态高电平电流

输出离阻态低电平电流

静态电源电流

输入电容

输出电容

中间(老炼前)电测试

中间(老炼后)电测试

最终电测试

A纽检验电测试

B组终点电测试

C组终点电测试

D纽终点电测试

SJ 20758--1999

续表1

(若无其他规定,-55°℃≤T≤125°℃Vpp*=5 V±10%)

TTL 接: IoL =2.4 mA

CMOS 接口:uL IμA

TTL 接口

CMOS接

TTL接口

CMOS接口

Vo-Yss

仅适用无上拉或下拉的

仅适用无止拉或下拉的

F1 MH., T. -25 °℃

f-1 MHz, Tc-25°C

表2电试验要求

分组(见表3)

极限值

按设计规定

变化量极限

Al, A2, A3, A7, A8a, A8b, A9, At0, A11Al, A2+ A3+ A4, A7, A8a, A8b, A9, A10, A11Al

注:1)该分组要求PDA计算(见本规范4.2)。4 2)

2)老炼和寿命试验要求的变化壁(4)测量只适用于A2分纠,变化鼠极限按本规范4.5.2的规定。

引用标准

GB3834

GE3439

GB3439

SJ 20758-1999

表3电测试

(诺无其他规定,GND=0V,Te=25°C)Vep 接地、被测输入端 Iik =1 mA。测所有输入端

Vs接地,被溅输入端 Iik=1 mA。测所有输入端

V=4.5 V,测所

有适用的瓣出端。

Ypp=4.5 V, 所

有适用的输出端。

TTL: IoH *-2 mA

CMOS: JoH ≤-1 μA

TTL: ToL -2.4 mA

CMOS: JOL SIμA

Vpp-5.5 V, V'l=5.5 V,

测所有输入端。

YDD-=5.5 V, V'=0 V,

测所有输入端。

Von=5.5 V, Yo-Ved*

测所有输出端。

Vpp=5.5 V, Vo-0 V,

测所有输出端:

仅适用无上拉或

下拉的器件

仅适用无上拉或

下拉的器件

Vpp-5.5 V,测 Vpp端.

Tc=125°C,所有参数、条件和规范值同A1分组。7。--55°C.所有参数、条件和规范值间 A1 分组。G

F-1MHz,溉所有输入端对 GND的电容。f1 MHz,测所有输出端对 GND 的电容。Ypp=4.5V:按设计性能:符合用户设计规范要求。见图2.T=125\C,其他同A7分组。

Tc --55 °C,其他同 A7 分组

Yop*4.5V。按设计性能:符合用户设计规范要求。见图2。Tc-125°C,其他同A9分组,

Tc--55\C,其他同 A9 分组。

注:1)若被测的某一端是专门设计的,必须在用户设计规范中说明。极限值

「最大

按承制方数据

按承制方数据

按设计规定

2)实现功能和开关特性检测的测试失量是专门设计的,必须包含在户设计规范中。关量系统必须符合本规范3.2.8的要求。极限值在用户设计规范中规定。4质量保证规定

4.1抽样和检验

除本规范另有规定外,抽样和检验程序应按GJB597A和GJB548A方法5005A的规-6-

KAoNrKAca-

4.2筛选

SJ20758—1999

在鉴定检验和质量致性捡验之前,全部器件应按GJB548A方法5004A和本规范表4的规定进行筛选。

表4筛选程序

若无其它规定,表中采用的方法系指GJB548A的试验方法。筛选项日

内部目检(封装前)

稳定性烘焙

(不要求终点电测试)

温度循环

恒定加速度

中间(老炼前)电测试

中间(老炼后)电测试

允许的不合格品率(PDA)

及其计算

最终电测试

粗检漏

外部目检

鉴定和质量一致性检验的试

验样品抽取

4.3鉴定检验

4. 3. 1鉴定检验

条件和要求

试验条件B

试验条件C

(150 °℃, 24 h)

试验条件 C

试验条件DY1方向

本规范A2分组

试验杂件 A

125 °℃, 160 h

试验条件D

125°℃,160 h

本规范A2分组

和表104极限

10%。当不合格品率

不翻过20%时,可重

新提交老炼,但只允

许一次。

本规范A1,A2,A3.

A4, A7 A8a, A8b.

A9, A10. A11 分组

试验条件:A1或A2

试验条件:CI或 C2

试验后进行目检,引线断落、外壳破裂、封盖脱落为失效。

用4极限值计算 PDA 时,要求

记录 Iops值。

采用本规范图1所示的电路。可

选取静态、动态老炼的其中一种方式。

用老炼失效数(超过42分组极

限值或超过4极龈值的器件)除

以提交老炼的器数即为

PDA。不大于规定的 PDA 时,

则该批应接收。

本项筛选后,若引线镀涂改变或返工,则应再进行 A1 分组测试鉴定检验应按GJB597A中4.4的规定。所进行的检验应符合GJB548A方法5005A-7 -

SJ 20758—1999

和本规范A、B、C、D和E组检验(见本规范4.4.1~4.4.5)的规定。另外,下述5个鉴定阶段应该用确定的鉴定媒体来完成。4.3.2鉴定阶段和媒体

鉴定阶段

工艺监控和稳定性

工艺可靠性

宏单元设计和模拟

CAD布线和布线后模拟

设计检查软件验证

鉴定媒体

I.艺监控图形(PM)

标准评价电路(SEC)

宏单元测试芯片图形

门阵列的测试图形标准

承制方的试验情况

宏单元设计和模拟的鉴定,以及CAD布线和布线后模拟应以承制方的设计、布局和布线的能力为基础,并且承制方器件的实测性能特性(如传输延迟、上升和下降时间、驱动特性、触发电平等)应在模拟的性能特性极限值之内(见4.3.2.4)。YD

1op/2~YpD

注:①对于静态老炼,所有输入端道过电阻接Ppp,输出为开路或通过电阻连接到Vpp12~Vpp电阻R=6802~47k2,实际阻值应反映出最严的负载条件。若输出为开路,则输出端电阻可以任选。

②对于动态老炼,所有输入端通过电阻并连到时钟脉冲(CP)上,输出端通过电阻连接到Vop/2+0.5V。输入端电阻R=680247k2,输出端电阻R=1k2±5%输入借号要求,方波:占空比为50%±15%:频率fcp=100kHzt50%幅度:Vi-4.5 V~Ypm Vu=0±0.5 V.转换时间≤0.5 μs。? Vpn=5.0 V±0.5 V.

④}一输入端;0输出端:N(M)一最大编号的输入(输出)端。③在多电源端或多块端的情况下,所有的电源或地端都应连接到与其相适应的电平上。③引出端符号由用户确定。

图1静态、动态老炼和稳态寿命试验电路图8-

TTTKAONrKAca

兰态输出测试电路图

c.波形图

SJ20758--1999

标准输出测试电路图

测试点

注:①C=50pF±10%,包括探头和夹具电容。器件

一测试点

②输入脉冲特性:4≤6ns:F1MHz;占空比:50%。③所有不用的输入端连接到Ypp或GND。@ IThli- ttHL2* tThLi tTlh2- Itlhi= ITlho③当逃行功能测试和所有交流测试时(输出允许测试除外),S1闭合。对于ipzH测试,当S2打并时,S1和S3闭合。对于tpzL测试,当s3打并时,SI和S2闭合。①对\三态输出,R,=1kQ+10%。对-F非三态输出,Rz由在VoH=2.4V条件下的lon决定。③R,由Yn-0.05V时的loL(最小值)减去通过R到地的电流决定,图2开关测试电路和波形图

4.3.2.1T.艺控制和稳定性

SJ 20758—1999

直流参数的工艺控制和稳定性必须通过承制方和工艺监控图形(PM)米证明。为了直流工艺参数(承制方可以选择是否包括交流参数)的测试,PM(或专门插入或放置在划片槽中)可被设计成晶片形式或封装好的器件形式。PM设计在鉴定之前应送交鉴定机构批准,并且至少包括下列结构:a.N沟器件(最小结构)

b,P沟器件(最小结构)

N沟器件(大器件)

P沟器件(大器件)

薄层电阻测试结构

金属台阶分布结构

场阅值器件

h.金属间氧化物完整性结构

连接链(长度要足以代表接触电阻)(1)金属到多晶(适用时)

(2)金属1到金属2(适用时)的通道电阻。(3)反相器链(用于交流测试:由承制方定)。(4)金属到扩散层(适用时)。为了鉴定,应測试最少 3个不同批(每个晶片至少4个PM)的 PM,以保证建立有效的统计数据,并以此为依据判断承制方的工艺是否稳定和受控。可采用最近批的历史数据来满足这个要求(由承制方选择)。4.3.2.2工艺可靠性

可采用SEC(标准评价电路),来鉴定工艺可靠性,SEC设计应包括从3.2.1~3.2.1C所述的基本信息,在使用承制方的订购方设计规范之前,应提交给鉴定机构批准。它的制造工艺与生产和本规范的任何专用门阵列器件的制造工艺相同。SEC应设计成能对底层设计(扩散等)的可靠性及设计规则最坏情况条件进行评价。设计应利用宏单元库并形成振荡回路以及各种测试结构,这些测试结构在可靠性寿命试验中,可以检测金属与金属间短路或开路,高的通孔电阻及介质针孔。SEC应在最大规模(即器件分类中有最大门数的器件,若适用时其门阵列的封装应有最多的引出端数)的器件上实现。承制方的门阵列系列中有最多引出端数面有较少门数的器件品种或有较少引出端数较少门数的器件品种的鉴定通过扩展的方式进行(见4.3.3)。对于下列(4.4.1,4.4.2,4.4.3,4.4.4)电测试来说,SEC也是主要的鉴定媒体。对于承制方的SEC求说,测试极限值在订购方设计规范中规定(对于直流参数的最低要求,见本规范表1)。每个分组的电测试按表3的规定进行。当对SEC进行寿命试验时(见4.4.3),应适用于静态偏置老炼。4.3.2.3宏单元设计和模拟的鉴定应符合GJB548A中方法5010A附录A中A1.5的要求。4.3.2.4CAD布线和布线后模拟

应符合GJB548A中方法5010A附录A中A1.6的要求。4.3.2.5设计检查软件的验证

TTTKAONrKAca-

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。