GB/T 14241-1993

基本信息

标准号: GB/T 14241-1993

中文名称:信息处理 处理机系统总线接口(欧洲总线A)

标准类别:国家标准(GB)

标准状态:现行

发布日期:1993-03-16

实施日期:1993-01-02

出版语种:简体中文

下载格式:.rar.pdf

下载大小:2649954

标准分类号

标准ICS号:信息技术、办公机械设备>>35.200接口和互连设备

中标分类号:电子元器件与信息技术>>计算机>>L65系统设备接口

关联标准

采标情况:ISO 6951-1986

出版信息

出版社:中国标准出版社

页数:平装16开, 页数:80, 字数:160千字

标准价格:31.0 元

相关单位信息

首发日期:1993-03-16

复审日期:2004-10-14

起草单位:机电部第六研究所

归口单位:全国信息技术标准化技术委员会

发布部门:国家技术监督局

主管部门:国家标准化管理委员会

标准简介

本标准规定了一种称为欧洲总线A的处理机系统总线接口。它是应用于军事、工业和其他领域里的模块数据采集、通信处理和系统控制的一系列接口之一。 GB/T 14241-1993 信息处理 处理机系统总线接口(欧洲总线A) GB/T14241-1993 标准下载解压密码:www.bzxz.net

标准图片预览

标准内容

中华人民共和国国家标准

信息处理

处理机系统总线接口

(欧洲总线A)

Information processing-Processur systembus interface (Eurobus A)

GB/T14241—93

ISO6951-1986

本标准等同采用国际标推1SO6951--1986《倍息处理处理机系统总线按口(欧洲总线A)》。0引言

0.1概述

本标准规定了构成总线本身的信号线和与该总线相连接的设备的接口。本标推规定了对请求传送数据的设备进行总线时问分配和设备间传输数据的规约。然而,本标准不规定优先规则,这些规则留给特定的系统分别处理。本标准规定厂一整套的信号规则:负责分配总线的设备和传输数据的设备都遵循这些规测。附录F(补充件)中对每一种可能的传输类型都给山了说明例子。第6章中规定的电气和信号定时要求唯一地定义了欧洲总线A的接[1。第G章中还规定广一些机械要求,这些机械要求只是直接影响电气特性的那些部分(如总线的物理长度、连按器的间距,连接器的引脚距离,以及连接器上的信号分配)。但本标准不再进一步规定机械实现。附录J(补充件>中给出了二个选的欧洲总线的机械实现的例了。欧洲总线A可以实现8位、16位,24位、32位等数据宽度,但具有不向数据宽度的设备可以在问总线上操作。附录A(补充件)到D(补充件)总结了前四种数据宽度的逻辑实现。附录E(补充件)规定了连接器分配。

构成欧洲总线A的这组信号线为插在一个单一设备架总线底板上的设备提供厂一种进制数宁信息的传输媒介,一个总线底板上最多可以插人20个设备。这些设备分时复用总线。总线底板的最人长度限制为460mm。这些信号线形成一个异步非均衡电接口,它的最大传输能力为每秒6.5×10°字或字节。

0.2数据宽度和寻址能力

理论上讲,任何使用本总线的设备的数据/地址宽度足不受限制的。然而,欧洲总线A的异步规约和寻址设施允许数据宽度为8位、16位、21位和32.位的设备共享总线。并月,当这样共享总线时,最大的数据宽度就是数据最宽设备的数据宽度。总线的寻址能力允许设备访问山下列两种情况定义的苔通地址宽间的任一字内的任字节:a。由数据/地址位数所确定的子址范固;b对a项进行两位扩展,两位的全扩展只适用于非共享宽度总线:对下共享宽度总线,这两位的应用受到限制。

此外,还可以访问第一种地空间(此空间称作伪地址空间中任一完整字这第一种地址空问与第一种范围相等。

0.3设备

国家技术监督局1993-03-16批准1993-12-01实施bzxz.net

W.bzsoso.coIGB/T14241—93

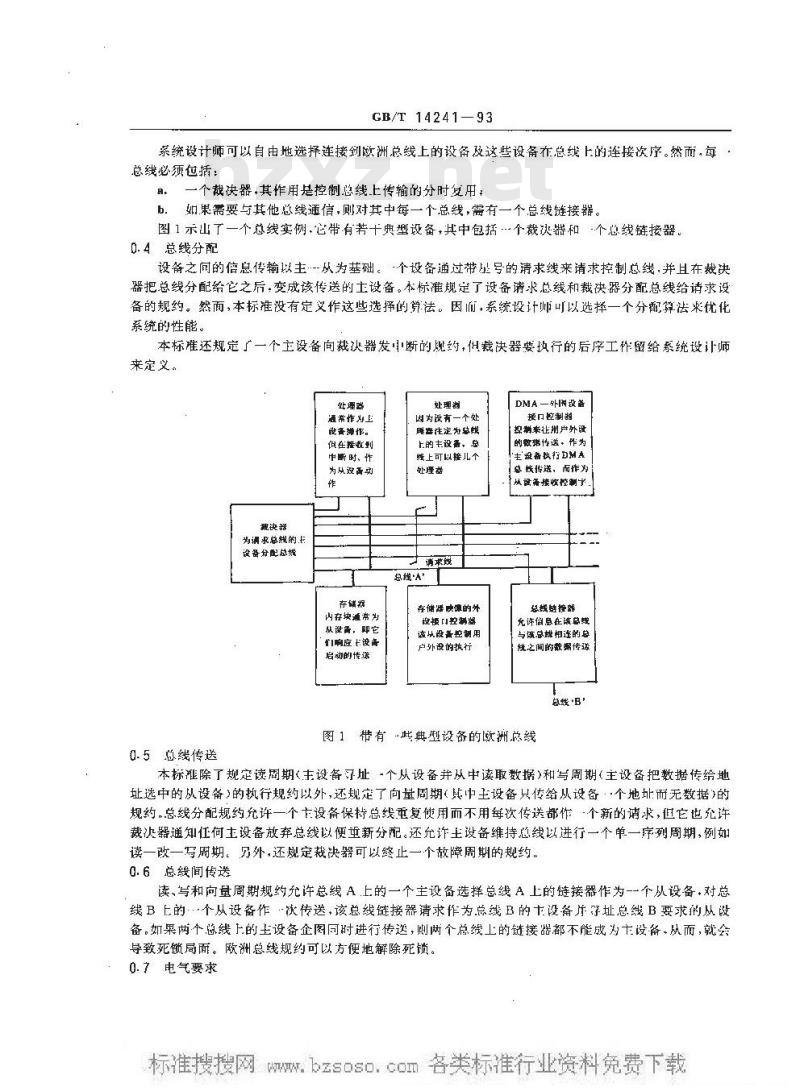

系统设计师可以自电地选择连接到欧洲总线上的设备及这些设备在总线上的连接次序。然而,每总线必须包括:

一个裁决器.其作用是控制总线上传输的分时复用:如果需要与其他总线通信,则对其中每一个总线,需有一个总线链接器。b.

图1示出了一个总线实例,它带有芳十典型设备,其中包括…个裁次器和个总线链接器。0.4总线分配

设备之间的信息传输以主·-从为基础。个设备通过带星号的清求线来请求控制总线,并且在裁决器把总线分配给它之后,变成该传送的士设备。本标准规定了设备请求总线和裁决器分配总线给请求设备的规约。然面,本标准没有定义作这些选择的算法。因而,系统设计师可以选择一个分配弹法来优化系统的性能、

本标准还规定了一个主设备向裁决器发中断的规药,供裁决器要执行的后序工作留给系统设计师来定义。

处理器

通常作为上

检备操作。

但在接收型

中断时、作

为以设否动

现快器

为调求总线的

设备分配总线

存储据

内存块通常为

从险雷,即它

↑响应士设病

启动的传送

处理器

因为有一个处

是造注定为总频

上的主设备,总

虽上可以接儿个

处理器

请求戏

总线·A

存储腰映课的外

设损控制器

该以设备控制用

户外设的执行

DMA一外用设备

换口控制器

控制率用户外设

的收据性送。作为

主设备执行EMA

总战传送,而作为

以设备接收控制了

总线鞋接器

允许信息在该总线

与该总划相逆的总

就之间的散竭传进

总线·B'

图1带有~些典型设备的欧洲总线05总线传送

本标准除了规定读周期(主设备子止个从设备并从中读取数据)和与写周期(主设备把数据传给地址选中的从设备)的执行规约以外,还规定了向量周期(其中主设备只传给从设备:·个地址而无数据)的规约,总线分配规约允许一个设备保持总线重复使用而不用每次传送部作-个新的请求,但它也允许裁次器通知任何主设备放弃总线以便重新分配。还允许土设备维持总线以进行一个单一序列周期,例如读一改一写周期。另外,还规定裁决器可以终止一个故障周期的规约,0.6总线间传送

读、写和向量周期规约允许总线A上的一个主设备选择总线A上的链接器作为--个从设备.对总线B上的个从设备作·次传送,该总线链接器请求作为总线B的十设备片寻址总线B要求的从设备,如果两个总线上的主设备企图同时进行传送,则两个总线上的链接器都不能成为士设备,从而,就会导致死锁局面。欧洲总线规约可以方便地解除死锁。0.7电气要求

GB/T14241—93

本标推规定了欧洲总线A设备需要遵循的电和定时要求,电气要求包括:总线上有效和无效逻辑状态的电压范围;b.

要求的端接网络特性;

c.要求的.总线发送器和接收豁特性;d.

要求的连到总线上的插件的特性,所规定的这套电气特性假定信号线上发生跳变所用的特定的稳定时间。因此,还规定了-些特定的定时限制。这些限制保证了在相应的控制信号跳变之前,相关的信号线已经稳定到要求的状态。0.8商用和军用版本

本标准规定了欧洲总线A的两种版本,一种是商用版本,温度范围0~70℃,另一种是军用版本,温度范围一55~125℃。当要求不同时,对两种版本分别进行规定。主题内容与适用范围

本标准规定了种称为欧洲总线A的处理机系统总线接口(下文简称为\总线”),它是应用于军事、工业和其他领域里的模块数据采集、通信处理和系统控制的一系列接口之一注:(D关于本标准规定的要求,包括数据宽度和寻址能力、总线上连接的设备、总线分配,总线传输、总线间传输、电气要求、背景知识等的详细情况。见第0章。②本标准中,用人写学母来表示总线周期名称的第一个字册。本标准所引用的标准列丁附录R(补充件)中。2定义

以下定义适用于本标:

2.1地址address

一数据字的位置,或若在任何读、写或向量周期的寻址阶段呈现在高速通路上的值,2.2裁决器arbitcr

执行总线裁决功能的设备·它还负责处理中断,超时放障周期并中止它。2.3 裁决 arbitration

把总线分配给请求设备并使其成为土设备的方法。2.4总线底板backplane

带有供插件板插放连接器的.总线组件,2.5请求设备bidding device

企图启动个或几个总线周期并请求使用总线的设备,2.6总线bus

一特定欧洲总线实现所用的总线线的完整集合。2.7总线周期bus cyele

连接在总线上的各设备间传递信息的一组密划关连的总线信号。该组信号山地址阶段与后序的数据阶段(向量周期只有前者)组成:在地址阶段,主设备把地址放在总线上并让从设备来识别。2.8总线线hus line

两个或几个设备之间的电气连接线。2.9总线链接器bus linker

一插入两个或多个总线上的设备,通过它一个总线上的主设备可以与另:个总线上的从设备互送信息,

2.10总线电压busvoltage

总线线上相对于总线零参考电压测得的电压俏。W.bzsoso.coI2.11字节byte

组连续的8位二进制位.

2.12电路板circuit card

GB/T 14241—93

二个可以在其工安装各种电子器件.并叮以捕件板的形式插入欧洲总线底板的板。2.13数据dala

地址处保存的,从地址处读出的或写进地址处的信息。2.14 死锁deadly embrace

使用同,总线链接器的两个总线问的传送已启动,但均不能完成传送的状态。2.15设备device

个功能块,山一块或儿块电路板组成,它可以通过总线或其子集与其他功能块通信。2.16延伸板extender panel

-个可以插入总线和刃一电路板之间的电路板。使得容易接触另一电路板,而义保持该电路板与总线相连。

2.17保持周期hold cycles

.个周期序列,在此期问裁决器不要求主设备释放总线以进行再分配。2.18 高速通路lighway

用丁在欧洲总线上的设备间传送数据和地址的那些总线线。2.19不可分割操作indivisible operation一个总线周期序列,在此期问内,为保证正确的系统功能得到实现,不得有其他总线周期在此序列中出现。

例如:读一改一写序列。

2.20总线间传输interbux transfer指在使用两个或彩个总线以及,个或多个总线链接器的设备之问的信息传送,2.21 中断 interrupt

一个设备为了启动一个预先设定的依赖于系统的功能而向裁决器传递的一个标志。2.22主设备master

启动传送的设备。

2.23昔通地址帘间 normal address space容量由总线高速路的线数决定·并且可以作为字或字节子址的地址空问。2.24 规约 protocol

用于总线连接的设备间传递信或命令的信号规则。2.25伪地证空间pseudo addrcss suace另-种独立的地址空问,其容垦由高速通路线数决足,位只能进行字访问。2.26读周期rtadeycle

主设备由从设备得到字或字节的总线周期。2.27复位reset

使连在总线上的设备均回到预先设定的初始状态的操作,2.28维持周期retain cycles

一种总线周期,在其尾部士设备仍控制总线以完成一个不可分制操作,2.29稳定时间 selling lime

总线线从其前一状态完全稳定到新的逻辑状态所用的时间。2.30插箱shelf

固定底板和插在其上的循件板的物理结构。W2.31时滞skew

GB/T 14241—93

假定在两条总线线上同时启动两个逻辑跳变,则时滞是指连在总线上特定点的插件板上的两个接收器接到这两个跳变的时间差。2.32从设备sla

对主设备置于总线上的地址,在确定的周期内给予响应的设备。2.33插件spu

连到总线两端之问某点的设备,2.34(总线线)状态stale(ofabus linc)总线线的有效和无效状态之·。2.35向量周期vectorcycle

一种总线周期,其日的足使土设备把一地址传送给从设备而不传送数据。2.36字word

位数等于在一个总线周期内总线上叮以传送的最大数据宽度的数组。2.37oV

信号返回路径,它是所行电兆测量的参考电压。注:0V不是安全地。本标准中,引间安垒地的地方+均特别标明。2.38字用期writecycke

个总线周期,在其间上设备把一个字书或·个宁写到从设备上。3具体的欧洲总线的命名

欧洲总线A系列中的每一种应按下列格命务。欧谜总线

命名中的每-项中以下项目决定:a.

地址资度

地址宽度可以等于10.18、26或34等(见注(());b。A代表第6章中规定的电气特性;限定信息

限定信息是说明版本的附加文宁(0.8条),也可以是供用户标识特定机械实现的标识文。注:(T:地址宽度为高速通路位数,即它等于数据位数2。)建议应提供充分的限定倍息以使用六或潜在用户标识欧洲总线的具体机械实现。例如,欧洲总线A的-一个18位地址实现的命名(忽略可选的限定息)为:“欧洲总线18/A商用\。4一致性

4.1设备的完全致性

符合本标准的设备应满足:

a:第5章的逻辑要求;

第6章的电气要求;

连接器分配的要求(见4.1条)。4.2逻辑致性

4.2.1被称作逻辑-致性的设备应该符合第与章的规约要求或衍合这些要求的一个适当子集。注:例如一个只用作从设备的设备可以不必作为请求设备。·个被称作具有逻辑一效性的实现应该由下列情况之确定:4.2.2

总线线只用于本标准规定的用途或如果总线的某些线不用于规定的用途;则:b.

WCB/T 14241—93

(1)按规定的规约进行操作的设备之间,总线上的正带信号不会在有关实现上引起任何误动作。

(2)该实现内部所产生的信号不会对按本标难规定的规约进行操作的总线上的设备产生任何异常。

4.3电气一致性

被称作具有电气,-致性的设备应:a.符合6.1和6.2条关于设备的电气要求;或b,当连入.总线时,它不应导致总线违反6.3条中关于总线电气的要求。如果一个设备逻辑上一致(见 4.2条),IⅡ电气方面与b项相符(即,与a 项不符),则与本标准有关的设备描述应包括一个明确的说明,以指出要连入的设备会对系统带来哪些限制。4.4机械一致性

数据宽度为8、16,24和32位的连接器分配将在附录E(补充件)中规定。5欧洲总线A规约

5.1预备知识

5.1.1概述

5.2条中将规定构成欧洲总线A的信号集。用于对潜在用户分配总线从而影响总线上传输的信号的规约将在 5.3 和 5. 4 条中规定。注:(I)随录F(补充件)中将给出与这些要求一致的总线规约的操作例了②)应用既洲总线规约的任何传送一般涉及三种设备。2。裁决器,它的作用为;

(1)允许一个请求设备使用总线,然后该设备变成上设备;或(2)允许现行主设备继续使用总线,b,主设备,烂通过对另一个设备寻址来启动传输,C。识别地止,接受传送从而成为从设备的设备。5.1.2基本总线周期

存在如下三种基木类型的总线周期(见表1):a.

读周期,在其间主设备将数据由从设备中读出;写周期,在其间主设备将数据写入从设备:向量周期,在其间地址由主设备传往从设备。注:主设备用以标识一个从设备所能识别的位益单元地址是总线在向案周期中能传送的唯·-信息。5.1.3总线派生周期

每一种基本总线周期可以有两种派生周期:a.

读并且保持;

读并且维持;

写并且保持,

写并月维持;

向量并且保持;

向拿并且维持。

法:①保持周期的主要目的是允许要求多个总线周期的设备(如处理器)可以重复访问总线而不必对每周期进行请求。因为使用这种周期会延迟对另外设备的总线分配,所以,建议只有当有关设备使用下一总线调期的可能性很高时才使用这种周期。

维持周期的上要日的是允许一些不可分制操作,如该·改一笃,得以实现。②派生周期与基本周期的区别与裁决器使设备释放总线以进行重新分配所需时间有关,W③总线分配规约的设计使得:

GB/T14241—93

1。一个空闲总线分配经所最小可避免的起迟;b.只要可能,总线分配与总线周期重登以减少延迟:c.一个要求多个总线周期的设备(如·个处理器)不必对每-周期都要作一次请求}…-设备可以实现不可分割周期(这--功能提供一种必要的于段,例如.以-个读周期后跟-个写周期,构成一个读效写周期}#

e.除可执行读、写或向量周期以外.还可以间裁决器发-中断·然后裁决器负责处理该中断。5.2信号

5.2.1总线线的使用

所有裁决器、主设备和从设备之间的通信都足通过表1中定义的欧洲总线规约线来进行的。这些线的用法是这样的:任何一个设备或儿个设备同时可以置线有效。如果没有任何设备置某线有效,则该线保持无效。

5.2.2位编号

数锯和地址线的最高位的位编零按式(1)计算:N- 8P 1

式中,N——位编号:

任何正整数,

最高有效字节地址线的位编号M这样计算:M为小L[(N+1)/8的最人整数,

注:例如为「子址--个36位数锯字中的-个学节,N-15.H

M:tog:16/8,即 M-1

所以M=,即只要-个字节地址线。5.2.3字节方式地址选择

当前总线主设备应通过对字节工作方式和字节地址线的编码(见表2),来舰定选择全字工作方式或字节工作方式。如果选择全字工作方式,则编码还要进-一步选择伪地止空间或普通地址空间。如果选择字节工作方式,则要进一步规定编码以确定寻址哪一字节:这时伪地址空间不可用。5.3地址识别规约

5.3.1数据宽度

如果一个总线上的所有设备的数据宽度相间.则由AdM1)AdM(0),H(N)至H(0)所提供的2(N十3)位高速通路全寻址能力可用丁所有设备的数据觉度全部相同的总线对于--个8位数据宽度,这一寻址能力由表3中给出的方法确定,对丁具有不同数据宽度的设备的总线.地址分配的方法在附录G(补充件)中规定。注:总线的功能不依赖此方法。5.3.2地址修改位的识别

如果总线上操作的一从设备与其他不同数据宽度的设备共亨该总线,则在所有的情况下,它应识别地址修改线的一个编码,而且仪识别一个编码。在任何系统中,某具体数据究度的设备所识别的特定编码山下列规则分配:a、在表4列出的码中.首先应分配题头为第块所对应的编码(第3和第1列)b、如需要进一步编码.则依次分配题头为第2.3、4块对应的编码(第5到第10列)。这些编码的分配按数据宽度由小到大的顾序进行,且已分配的任何码不应再对其他数据进行分配;(1)如果第2.3或第4快已分配给8位设备识别.则16位的设备应分配下-个更高的可用块。GB/T 14241: 93

(2)如果第2、3或第4块已分配给8位和16位设备来识别,则24位设备应分配下-个更高的可用块。

(3)如果第2.3或第4块已分配给8位、16位和24位的设备来识别,则32位设备应分配下个更高的可用块。

任何未用的块应可用来扩展任何设备的地止范围。5.4欧洲总线A规约规则

5.4.1预备知识

表1中规定和命名的总线线的使用规则应按5.1.2~5.4.6系的规定:a.

设备请求使用总线和裁决器允许使用总线见5.4.2条的规删A1到A12对于设备选择并与从设备通信,见5.4.3条的规则MI到M11:对于从设备响应主设备,见5.4.4系的规则S1到S6;对下裁决器终正总线周期,见5.4.5条的规则C1到C4#对于总线链接器请求总线重新分配;见5.4.6条的规则D1到D2注:在本标准中采用点一数编导。为易于安排和标识规则甜条件,使用大写字母、小写字性和小写罗马数字代码。每一规则用一字母和一数字表示(如“A9\)。在每一规则中,替换条件*或\用小写英文字尽丧示,而并列杀件“与”州小写罗马数字表示。

5.4.2总线分配规则

规则AI:当设备n请求使用总线时,它通过保持Ru(n)有效来申请,当且仅当:(i)它末被封锁(规则A7和A12):并且(i)BusG足无效的:并且

(i)R足无效的。

规则A2:裁决器将通过保持相应的丽线有效来分配总线给其中一个请求设备,当且仅当:(i)Rq(n)已右效;并且

(i)裁决器还未保持R线有效并且(Hi)BusG效;并旺

(iv)BusAcq无效,并且

(v)无效;并且

(vi)BusDeallocate无效并月

(vii)CcAbort无效:并耳

(vill)Rs无效。

规则A3.裁决器保持Bus江有效,当且仅当:(ai)通过规则A2,裁决器巴作出分配,并且(aii)Rs是无效:或

注:总线分配已完吨。

(bi)裁决器未保持Ra线有效:并凡(bi)CcBn有效:并凡

(bii) CeRes无效,并月

【biv)BusDeallacate有效,并H(bv)CcRes在Bus[)eallocate变为有效时是无效的;作且(bvi)Rs无效。

注:裁决器重新分配从设备拒绝的周期,信号名(缩笃)

高速通路线

数据/地址

(H()-H(N))

地址修改线

位(0),(1)

(AdM(0),AdM(1))

字节方式/地址空间选择线

学节工作方式

(Bytwk)

节地比

粒(0)--(M)

(ByiAd(O)到

ByrAd(M))

总线分配规约线

诸求(n)

总线不授与

(RusGr)

总线获取

(BusAca)

传送控制握手线

GB/T 14241—93

表1欧洲总线A规约线

1/每一蓓在

总线主设备

分时复用双向数据和地址线。H(0)应用作最低有效位。最高有效位的编号H(N)应按5.2.2条中的规定。地址偿改线。它们现成可用,也可以被用来扩展由H(の)~I(N)所追义的容量之外的地址空间,并对共享同·总线的不间数据宽度的设备进行选择(见5.3条

这些线将通过字节方式/地址空间选择编码(见5.2.3条)来限定高速通路上的地址。般高有效字节地址位的编号(M)应按5.2.2条中的规定。如果N.7,字节工作方式毁将保持尤效每一可能请求总线分配的设备都有一条请求线。这些线以星形方式将设备接到裁决器上。请求(n)线成由设备(n)来激励以通知裁决器它请求总线分配。裁决器应使该请求线有效.同时激励总线投与线米把总线分配给设备(n)。

裁决器在激励特定设备的请求继以产生一新的总线分配的同时,肩动该线。该设备将成为下一传输的当前总线主设备。

裁决器还可以激励该条线而不激励请求线来重新分配当前的总线主设备(见5.4.5茶)。当前总线主设备将激励该条线以表明它已接受总线授与。如果该从设备准备励BusDeallocnt,则此线可由该从设备保持有效。

这条线由当前总线卡设备激励以通知裁决器它要请求个中断胤期

W周期开始

(CBn))

累期响应

(CeRes)

周期宠成

(CeFin)

周期中止

信号名(缩写)

(AiFL)

复位(Rs)

总线量新分配

(BusDeallacate)

Fiy+wk

BytAd(M)

GB/T 14241

续表1

这条线由当前主设备徽励以表示,,高速通路上的地址和字节方式/地址空间选择线足稳定的;

b.周期完成线(它在传送的这点表示是读/向量周期或写周期)是薇定的。

这条线出一设备来激励以指出它认别了高速逛路上:的地址并H已成为当前总线从设备。主设备在检测到此线变为有效之后,应撤消高逆路上的地址。这条双向线应由下列设备激励:a\前主设备

(1)在读周期指出地址已撤消。

(2)在写周期来标识此周期为写周期并且当烂被释放时,表示写数据己被撤消。b.读数据时传输由在当前从设备激动,此线由裁决1

器励以中止:个无效的总线周期复位线,此线与总线上的所有设备相理。当此线被任何设备(该设备具有此线激能力)激励时,将导改一个总线总复位。

此线出总线链接器来激励以通知裁决器a.总线链接器请求打断死锁,或b. 要求裁决需让总线:设备释收总线以重新分配。在总线重新分配线被激励时,周期响应绒的状态应用米规定上述哪-种情说有效

表2字节方式/地址空间选择线编码BytAd(M-1)

BycAdo)

普通地址空间整个字(N十1位)伪地址空间整个字(N:1位)

最低有效学节(字节0)

普通地址空间

字节:2(M+1)—2)

7书(2(M+)-)

注:(在表2和以后的丧中,缔写“Acv\表示有效状态,“\表示尤效状态。符号“X\表示两种状态的任一种。(② 关于 M 和 N 的值见 5. 2. 2 条~W.AdMd(1)

注:见者2注(0

总线数

据宽度

(位)

设备数

据宽度

(位)

: GB/T14241—93

表3地址识别规约(N=7)

AdMd(o)

8位设备第4块

8位设备第3块

8 位设备第 2 块

8位设备第1块

共享同

-总线的不同宽度的从设备要识别的地址修改码用丁地址块识别的地址修改码

第1块

AdM(1)

注,见表2注①

第2块

AdM(1)

规则A4:请求设备应释放其Rq线,当且仅当:(a)BusGr有效,或

(b)Rs有效。

规则A5:设备应保持BuSACC有效当目付当,(ai)BusGr有效;并且

AdM(0)

第3块

(ai)其R线有效(而且不是它自已保持此线有效):并且(aili)CcBn无效,并且

(aiv)CcRes无效;并且

(av)CeFin效并且

avi)该设备未保持It线有效:月且(avii)CeAbort无效:并且

(avi)Rs无效:或

注:该主设备获得总线。

(bi)CeRcs无效并且

(bi)CeB有效,并丑

AdM(o)

H(7)H(O)

第4块

AdM(1)

AdM(u)

(bli)高速通路上的信号和对应丁一地址的字节方式线上的信号已被该设备识别,并月(biv)该设备末保持CcFin有效,并月(bv)根据规则Dla惑(在应用规则Sl后)规划Dlh,此设备准备保持EusIeallocate有效并且W(bvi)CAori无效:并且

(bvii)R效。

GB/T14241—93

注,如果一从段备企图请求裁决器撤消对当前主设备的分配,则它在CcRes之前保持BusAc有效。或者,如果它企图拒绝该周期.则飞在Rxcnllacate之前保持BusAcq有效。规则A6:作为规则A5的另--种选择,设备应保持右效,并由此启动一个中断周期,当几仪当:(i)BusGr有效:并且

(i)其Ro线有效(并且不足它自巴保持此线有效):并且(ili)它未保持BusAcq有效:并凡Gv)CeAbur无效R

(v)Rs无效。

注:士设备间裁决器发一个中断。规则A7:一设备应被锁住,当凡仪当:(a)根据规则A5a保持BusAc有效;或(b)根据规则A6保持工有效。

规则A8:裁决器应释放BusGr,当且仅当:ai)BusAc有效,并且

(aii)BusDeallocate无效,或

注!裁器应答总线我得。

(hi)I有效,许H

(bii)BusDeallocale无效,或注:裁决器应答一中断、

(i)它未保持一Rq线有效;

(ci)BusAq无效;或

注:裁决器完成撤消总线分配交接过程。(di)它保持CcAbori有效;并且(dii)BusDeallocate无效,或

(c) Rs有效。

规则A9:裁决器应释放它日前保持有效的任仰Rg线,当且仅当:(ai)Bust无效并

ali)BusA效;并

(all)瓦无效;并且

(aiv)裁决器不准备依规则A3保持BusGr有效;或浅。最后分配的主设备已完成使用总线。(bi)Bus(无效;并且

(bi):设备保持其Rg线有效;并且(bili)裁次器不推备依规划A3保持BusGr有效;或注:一设备请求分配时,另一已分配的士设备仍在使用总线。(c)Bus)eallocate有效:或

注:裁决器请求已分配的尘设备放总线以进行再分配。(d)它保持CAbort有效;或

(e)复位信号有效。

规则A10:保持Bu5Acq有效的设备应释放它,当且仅当:(ai)当前总线尚期已建立(规则M5),并几(aii)设备的Rq线有效;并且

W.

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。

信息处理

处理机系统总线接口

(欧洲总线A)

Information processing-Processur systembus interface (Eurobus A)

GB/T14241—93

ISO6951-1986

本标准等同采用国际标推1SO6951--1986《倍息处理处理机系统总线按口(欧洲总线A)》。0引言

0.1概述

本标准规定了构成总线本身的信号线和与该总线相连接的设备的接口。本标推规定了对请求传送数据的设备进行总线时问分配和设备间传输数据的规约。然而,本标准不规定优先规则,这些规则留给特定的系统分别处理。本标准规定厂一整套的信号规则:负责分配总线的设备和传输数据的设备都遵循这些规测。附录F(补充件)中对每一种可能的传输类型都给山了说明例子。第6章中规定的电气和信号定时要求唯一地定义了欧洲总线A的接[1。第G章中还规定广一些机械要求,这些机械要求只是直接影响电气特性的那些部分(如总线的物理长度、连按器的间距,连接器的引脚距离,以及连接器上的信号分配)。但本标准不再进一步规定机械实现。附录J(补充件>中给出了二个选的欧洲总线的机械实现的例了。欧洲总线A可以实现8位、16位,24位、32位等数据宽度,但具有不向数据宽度的设备可以在问总线上操作。附录A(补充件)到D(补充件)总结了前四种数据宽度的逻辑实现。附录E(补充件)规定了连接器分配。

构成欧洲总线A的这组信号线为插在一个单一设备架总线底板上的设备提供厂一种进制数宁信息的传输媒介,一个总线底板上最多可以插人20个设备。这些设备分时复用总线。总线底板的最人长度限制为460mm。这些信号线形成一个异步非均衡电接口,它的最大传输能力为每秒6.5×10°字或字节。

0.2数据宽度和寻址能力

理论上讲,任何使用本总线的设备的数据/地址宽度足不受限制的。然而,欧洲总线A的异步规约和寻址设施允许数据宽度为8位、16位、21位和32.位的设备共享总线。并月,当这样共享总线时,最大的数据宽度就是数据最宽设备的数据宽度。总线的寻址能力允许设备访问山下列两种情况定义的苔通地址宽间的任一字内的任字节:a。由数据/地址位数所确定的子址范固;b对a项进行两位扩展,两位的全扩展只适用于非共享宽度总线:对下共享宽度总线,这两位的应用受到限制。

此外,还可以访问第一种地空间(此空间称作伪地址空间中任一完整字这第一种地址空问与第一种范围相等。

0.3设备

国家技术监督局1993-03-16批准1993-12-01实施bzxz.net

W.bzsoso.coIGB/T14241—93

系统设计师可以自电地选择连接到欧洲总线上的设备及这些设备在总线上的连接次序。然而,每总线必须包括:

一个裁决器.其作用是控制总线上传输的分时复用:如果需要与其他总线通信,则对其中每一个总线,需有一个总线链接器。b.

图1示出了一个总线实例,它带有芳十典型设备,其中包括…个裁次器和个总线链接器。0.4总线分配

设备之间的信息传输以主·-从为基础。个设备通过带星号的清求线来请求控制总线,并且在裁决器把总线分配给它之后,变成该传送的士设备。本标准规定了设备请求总线和裁决器分配总线给请求设备的规约。然面,本标准没有定义作这些选择的算法。因而,系统设计师可以选择一个分配弹法来优化系统的性能、

本标准还规定了一个主设备向裁决器发中断的规药,供裁决器要执行的后序工作留给系统设计师来定义。

处理器

通常作为上

检备操作。

但在接收型

中断时、作

为以设否动

现快器

为调求总线的

设备分配总线

存储据

内存块通常为

从险雷,即它

↑响应士设病

启动的传送

处理器

因为有一个处

是造注定为总频

上的主设备,总

虽上可以接儿个

处理器

请求戏

总线·A

存储腰映课的外

设损控制器

该以设备控制用

户外设的执行

DMA一外用设备

换口控制器

控制率用户外设

的收据性送。作为

主设备执行EMA

总战传送,而作为

以设备接收控制了

总线鞋接器

允许信息在该总线

与该总划相逆的总

就之间的散竭传进

总线·B'

图1带有~些典型设备的欧洲总线05总线传送

本标准除了规定读周期(主设备子止个从设备并从中读取数据)和与写周期(主设备把数据传给地址选中的从设备)的执行规约以外,还规定了向量周期(其中主设备只传给从设备:·个地址而无数据)的规约,总线分配规约允许一个设备保持总线重复使用而不用每次传送部作-个新的请求,但它也允许裁次器通知任何主设备放弃总线以便重新分配。还允许土设备维持总线以进行一个单一序列周期,例如读一改一写周期。另外,还规定裁决器可以终止一个故障周期的规约,0.6总线间传送

读、写和向量周期规约允许总线A上的一个主设备选择总线A上的链接器作为--个从设备.对总线B上的个从设备作·次传送,该总线链接器请求作为总线B的十设备片寻址总线B要求的从设备,如果两个总线上的主设备企图同时进行传送,则两个总线上的链接器都不能成为士设备,从而,就会导致死锁局面。欧洲总线规约可以方便地解除死锁。0.7电气要求

GB/T14241—93

本标推规定了欧洲总线A设备需要遵循的电和定时要求,电气要求包括:总线上有效和无效逻辑状态的电压范围;b.

要求的端接网络特性;

c.要求的.总线发送器和接收豁特性;d.

要求的连到总线上的插件的特性,所规定的这套电气特性假定信号线上发生跳变所用的特定的稳定时间。因此,还规定了-些特定的定时限制。这些限制保证了在相应的控制信号跳变之前,相关的信号线已经稳定到要求的状态。0.8商用和军用版本

本标准规定了欧洲总线A的两种版本,一种是商用版本,温度范围0~70℃,另一种是军用版本,温度范围一55~125℃。当要求不同时,对两种版本分别进行规定。主题内容与适用范围

本标准规定了种称为欧洲总线A的处理机系统总线接口(下文简称为\总线”),它是应用于军事、工业和其他领域里的模块数据采集、通信处理和系统控制的一系列接口之一注:(D关于本标准规定的要求,包括数据宽度和寻址能力、总线上连接的设备、总线分配,总线传输、总线间传输、电气要求、背景知识等的详细情况。见第0章。②本标准中,用人写学母来表示总线周期名称的第一个字册。本标准所引用的标准列丁附录R(补充件)中。2定义

以下定义适用于本标:

2.1地址address

一数据字的位置,或若在任何读、写或向量周期的寻址阶段呈现在高速通路上的值,2.2裁决器arbitcr

执行总线裁决功能的设备·它还负责处理中断,超时放障周期并中止它。2.3 裁决 arbitration

把总线分配给请求设备并使其成为土设备的方法。2.4总线底板backplane

带有供插件板插放连接器的.总线组件,2.5请求设备bidding device

企图启动个或几个总线周期并请求使用总线的设备,2.6总线bus

一特定欧洲总线实现所用的总线线的完整集合。2.7总线周期bus cyele

连接在总线上的各设备间传递信息的一组密划关连的总线信号。该组信号山地址阶段与后序的数据阶段(向量周期只有前者)组成:在地址阶段,主设备把地址放在总线上并让从设备来识别。2.8总线线hus line

两个或几个设备之间的电气连接线。2.9总线链接器bus linker

一插入两个或多个总线上的设备,通过它一个总线上的主设备可以与另:个总线上的从设备互送信息,

2.10总线电压busvoltage

总线线上相对于总线零参考电压测得的电压俏。W.bzsoso.coI2.11字节byte

组连续的8位二进制位.

2.12电路板circuit card

GB/T 14241—93

二个可以在其工安装各种电子器件.并叮以捕件板的形式插入欧洲总线底板的板。2.13数据dala

地址处保存的,从地址处读出的或写进地址处的信息。2.14 死锁deadly embrace

使用同,总线链接器的两个总线问的传送已启动,但均不能完成传送的状态。2.15设备device

个功能块,山一块或儿块电路板组成,它可以通过总线或其子集与其他功能块通信。2.16延伸板extender panel

-个可以插入总线和刃一电路板之间的电路板。使得容易接触另一电路板,而义保持该电路板与总线相连。

2.17保持周期hold cycles

.个周期序列,在此期问裁决器不要求主设备释放总线以进行再分配。2.18 高速通路lighway

用丁在欧洲总线上的设备间传送数据和地址的那些总线线。2.19不可分割操作indivisible operation一个总线周期序列,在此期问内,为保证正确的系统功能得到实现,不得有其他总线周期在此序列中出现。

例如:读一改一写序列。

2.20总线间传输interbux transfer指在使用两个或彩个总线以及,个或多个总线链接器的设备之问的信息传送,2.21 中断 interrupt

一个设备为了启动一个预先设定的依赖于系统的功能而向裁决器传递的一个标志。2.22主设备master

启动传送的设备。

2.23昔通地址帘间 normal address space容量由总线高速路的线数决定·并且可以作为字或字节子址的地址空问。2.24 规约 protocol

用于总线连接的设备间传递信或命令的信号规则。2.25伪地证空间pseudo addrcss suace另-种独立的地址空问,其容垦由高速通路线数决足,位只能进行字访问。2.26读周期rtadeycle

主设备由从设备得到字或字节的总线周期。2.27复位reset

使连在总线上的设备均回到预先设定的初始状态的操作,2.28维持周期retain cycles

一种总线周期,在其尾部士设备仍控制总线以完成一个不可分制操作,2.29稳定时间 selling lime

总线线从其前一状态完全稳定到新的逻辑状态所用的时间。2.30插箱shelf

固定底板和插在其上的循件板的物理结构。W2.31时滞skew

GB/T 14241—93

假定在两条总线线上同时启动两个逻辑跳变,则时滞是指连在总线上特定点的插件板上的两个接收器接到这两个跳变的时间差。2.32从设备sla

对主设备置于总线上的地址,在确定的周期内给予响应的设备。2.33插件spu

连到总线两端之问某点的设备,2.34(总线线)状态stale(ofabus linc)总线线的有效和无效状态之·。2.35向量周期vectorcycle

一种总线周期,其日的足使土设备把一地址传送给从设备而不传送数据。2.36字word

位数等于在一个总线周期内总线上叮以传送的最大数据宽度的数组。2.37oV

信号返回路径,它是所行电兆测量的参考电压。注:0V不是安全地。本标准中,引间安垒地的地方+均特别标明。2.38字用期writecycke

个总线周期,在其间上设备把一个字书或·个宁写到从设备上。3具体的欧洲总线的命名

欧洲总线A系列中的每一种应按下列格命务。欧谜总线

命名中的每-项中以下项目决定:a.

地址资度

地址宽度可以等于10.18、26或34等(见注(());b。A代表第6章中规定的电气特性;限定信息

限定信息是说明版本的附加文宁(0.8条),也可以是供用户标识特定机械实现的标识文。注:(T:地址宽度为高速通路位数,即它等于数据位数2。)建议应提供充分的限定倍息以使用六或潜在用户标识欧洲总线的具体机械实现。例如,欧洲总线A的-一个18位地址实现的命名(忽略可选的限定息)为:“欧洲总线18/A商用\。4一致性

4.1设备的完全致性

符合本标准的设备应满足:

a:第5章的逻辑要求;

第6章的电气要求;

连接器分配的要求(见4.1条)。4.2逻辑致性

4.2.1被称作逻辑-致性的设备应该符合第与章的规约要求或衍合这些要求的一个适当子集。注:例如一个只用作从设备的设备可以不必作为请求设备。·个被称作具有逻辑一效性的实现应该由下列情况之确定:4.2.2

总线线只用于本标准规定的用途或如果总线的某些线不用于规定的用途;则:b.

WCB/T 14241—93

(1)按规定的规约进行操作的设备之间,总线上的正带信号不会在有关实现上引起任何误动作。

(2)该实现内部所产生的信号不会对按本标难规定的规约进行操作的总线上的设备产生任何异常。

4.3电气一致性

被称作具有电气,-致性的设备应:a.符合6.1和6.2条关于设备的电气要求;或b,当连入.总线时,它不应导致总线违反6.3条中关于总线电气的要求。如果一个设备逻辑上一致(见 4.2条),IⅡ电气方面与b项相符(即,与a 项不符),则与本标准有关的设备描述应包括一个明确的说明,以指出要连入的设备会对系统带来哪些限制。4.4机械一致性

数据宽度为8、16,24和32位的连接器分配将在附录E(补充件)中规定。5欧洲总线A规约

5.1预备知识

5.1.1概述

5.2条中将规定构成欧洲总线A的信号集。用于对潜在用户分配总线从而影响总线上传输的信号的规约将在 5.3 和 5. 4 条中规定。注:(I)随录F(补充件)中将给出与这些要求一致的总线规约的操作例了②)应用既洲总线规约的任何传送一般涉及三种设备。2。裁决器,它的作用为;

(1)允许一个请求设备使用总线,然后该设备变成上设备;或(2)允许现行主设备继续使用总线,b,主设备,烂通过对另一个设备寻址来启动传输,C。识别地止,接受传送从而成为从设备的设备。5.1.2基本总线周期

存在如下三种基木类型的总线周期(见表1):a.

读周期,在其间主设备将数据由从设备中读出;写周期,在其间主设备将数据写入从设备:向量周期,在其间地址由主设备传往从设备。注:主设备用以标识一个从设备所能识别的位益单元地址是总线在向案周期中能传送的唯·-信息。5.1.3总线派生周期

每一种基本总线周期可以有两种派生周期:a.

读并且保持;

读并且维持;

写并且保持,

写并月维持;

向量并且保持;

向拿并且维持。

法:①保持周期的主要目的是允许要求多个总线周期的设备(如处理器)可以重复访问总线而不必对每周期进行请求。因为使用这种周期会延迟对另外设备的总线分配,所以,建议只有当有关设备使用下一总线调期的可能性很高时才使用这种周期。

维持周期的上要日的是允许一些不可分制操作,如该·改一笃,得以实现。②派生周期与基本周期的区别与裁决器使设备释放总线以进行重新分配所需时间有关,W③总线分配规约的设计使得:

GB/T14241—93

1。一个空闲总线分配经所最小可避免的起迟;b.只要可能,总线分配与总线周期重登以减少延迟:c.一个要求多个总线周期的设备(如·个处理器)不必对每-周期都要作一次请求}…-设备可以实现不可分割周期(这--功能提供一种必要的于段,例如.以-个读周期后跟-个写周期,构成一个读效写周期}#

e.除可执行读、写或向量周期以外.还可以间裁决器发-中断·然后裁决器负责处理该中断。5.2信号

5.2.1总线线的使用

所有裁决器、主设备和从设备之间的通信都足通过表1中定义的欧洲总线规约线来进行的。这些线的用法是这样的:任何一个设备或儿个设备同时可以置线有效。如果没有任何设备置某线有效,则该线保持无效。

5.2.2位编号

数锯和地址线的最高位的位编零按式(1)计算:N- 8P 1

式中,N——位编号:

任何正整数,

最高有效字节地址线的位编号M这样计算:M为小L[(N+1)/8的最人整数,

注:例如为「子址--个36位数锯字中的-个学节,N-15.H

M:tog:16/8,即 M-1

所以M=,即只要-个字节地址线。5.2.3字节方式地址选择

当前总线主设备应通过对字节工作方式和字节地址线的编码(见表2),来舰定选择全字工作方式或字节工作方式。如果选择全字工作方式,则编码还要进-一步选择伪地止空间或普通地址空间。如果选择字节工作方式,则要进一步规定编码以确定寻址哪一字节:这时伪地址空间不可用。5.3地址识别规约

5.3.1数据宽度

如果一个总线上的所有设备的数据宽度相间.则由AdM1)AdM(0),H(N)至H(0)所提供的2(N十3)位高速通路全寻址能力可用丁所有设备的数据觉度全部相同的总线对于--个8位数据宽度,这一寻址能力由表3中给出的方法确定,对丁具有不同数据宽度的设备的总线.地址分配的方法在附录G(补充件)中规定。注:总线的功能不依赖此方法。5.3.2地址修改位的识别

如果总线上操作的一从设备与其他不同数据宽度的设备共亨该总线,则在所有的情况下,它应识别地址修改线的一个编码,而且仪识别一个编码。在任何系统中,某具体数据究度的设备所识别的特定编码山下列规则分配:a、在表4列出的码中.首先应分配题头为第块所对应的编码(第3和第1列)b、如需要进一步编码.则依次分配题头为第2.3、4块对应的编码(第5到第10列)。这些编码的分配按数据宽度由小到大的顾序进行,且已分配的任何码不应再对其他数据进行分配;(1)如果第2.3或第4快已分配给8位设备识别.则16位的设备应分配下-个更高的可用块。GB/T 14241: 93

(2)如果第2、3或第4块已分配给8位和16位设备来识别,则24位设备应分配下-个更高的可用块。

(3)如果第2.3或第4块已分配给8位、16位和24位的设备来识别,则32位设备应分配下个更高的可用块。

任何未用的块应可用来扩展任何设备的地止范围。5.4欧洲总线A规约规则

5.4.1预备知识

表1中规定和命名的总线线的使用规则应按5.1.2~5.4.6系的规定:a.

设备请求使用总线和裁决器允许使用总线见5.4.2条的规删A1到A12对于设备选择并与从设备通信,见5.4.3条的规则MI到M11:对于从设备响应主设备,见5.4.4系的规则S1到S6;对下裁决器终正总线周期,见5.4.5条的规则C1到C4#对于总线链接器请求总线重新分配;见5.4.6条的规则D1到D2注:在本标准中采用点一数编导。为易于安排和标识规则甜条件,使用大写字母、小写字性和小写罗马数字代码。每一规则用一字母和一数字表示(如“A9\)。在每一规则中,替换条件*或\用小写英文字尽丧示,而并列杀件“与”州小写罗马数字表示。

5.4.2总线分配规则

规则AI:当设备n请求使用总线时,它通过保持Ru(n)有效来申请,当且仅当:(i)它末被封锁(规则A7和A12):并且(i)BusG足无效的:并且

(i)R足无效的。

规则A2:裁决器将通过保持相应的丽线有效来分配总线给其中一个请求设备,当且仅当:(i)Rq(n)已右效;并且

(i)裁决器还未保持R线有效并且(Hi)BusG效;并旺

(iv)BusAcq无效,并且

(v)无效;并且

(vi)BusDeallocate无效并月

(vii)CcAbort无效:并耳

(vill)Rs无效。

规则A3.裁决器保持Bus江有效,当且仅当:(ai)通过规则A2,裁决器巴作出分配,并且(aii)Rs是无效:或

注:总线分配已完吨。

(bi)裁决器未保持Ra线有效:并凡(bi)CcBn有效:并凡

(bii) CeRes无效,并月

【biv)BusDeallacate有效,并H(bv)CcRes在Bus[)eallocate变为有效时是无效的;作且(bvi)Rs无效。

注:裁决器重新分配从设备拒绝的周期,信号名(缩笃)

高速通路线

数据/地址

(H()-H(N))

地址修改线

位(0),(1)

(AdM(0),AdM(1))

字节方式/地址空间选择线

学节工作方式

(Bytwk)

节地比

粒(0)--(M)

(ByiAd(O)到

ByrAd(M))

总线分配规约线

诸求(n)

总线不授与

(RusGr)

总线获取

(BusAca)

传送控制握手线

GB/T 14241—93

表1欧洲总线A规约线

1/每一蓓在

总线主设备

分时复用双向数据和地址线。H(0)应用作最低有效位。最高有效位的编号H(N)应按5.2.2条中的规定。地址偿改线。它们现成可用,也可以被用来扩展由H(の)~I(N)所追义的容量之外的地址空间,并对共享同·总线的不间数据宽度的设备进行选择(见5.3条

这些线将通过字节方式/地址空间选择编码(见5.2.3条)来限定高速通路上的地址。般高有效字节地址位的编号(M)应按5.2.2条中的规定。如果N.7,字节工作方式毁将保持尤效每一可能请求总线分配的设备都有一条请求线。这些线以星形方式将设备接到裁决器上。请求(n)线成由设备(n)来激励以通知裁决器它请求总线分配。裁决器应使该请求线有效.同时激励总线投与线米把总线分配给设备(n)。

裁决器在激励特定设备的请求继以产生一新的总线分配的同时,肩动该线。该设备将成为下一传输的当前总线主设备。

裁决器还可以激励该条线而不激励请求线来重新分配当前的总线主设备(见5.4.5茶)。当前总线主设备将激励该条线以表明它已接受总线授与。如果该从设备准备励BusDeallocnt,则此线可由该从设备保持有效。

这条线由当前总线卡设备激励以通知裁决器它要请求个中断胤期

W周期开始

(CBn))

累期响应

(CeRes)

周期宠成

(CeFin)

周期中止

信号名(缩写)

(AiFL)

复位(Rs)

总线量新分配

(BusDeallacate)

Fiy+wk

BytAd(M)

GB/T 14241

续表1

这条线由当前主设备徽励以表示,,高速通路上的地址和字节方式/地址空间选择线足稳定的;

b.周期完成线(它在传送的这点表示是读/向量周期或写周期)是薇定的。

这条线出一设备来激励以指出它认别了高速逛路上:的地址并H已成为当前总线从设备。主设备在检测到此线变为有效之后,应撤消高逆路上的地址。这条双向线应由下列设备激励:a\前主设备

(1)在读周期指出地址已撤消。

(2)在写周期来标识此周期为写周期并且当烂被释放时,表示写数据己被撤消。b.读数据时传输由在当前从设备激动,此线由裁决1

器励以中止:个无效的总线周期复位线,此线与总线上的所有设备相理。当此线被任何设备(该设备具有此线激能力)激励时,将导改一个总线总复位。

此线出总线链接器来激励以通知裁决器a.总线链接器请求打断死锁,或b. 要求裁决需让总线:设备释收总线以重新分配。在总线重新分配线被激励时,周期响应绒的状态应用米规定上述哪-种情说有效

表2字节方式/地址空间选择线编码BytAd(M-1)

BycAdo)

普通地址空间整个字(N十1位)伪地址空间整个字(N:1位)

最低有效学节(字节0)

普通地址空间

字节:2(M+1)—2)

7书(2(M+)-)

注:(在表2和以后的丧中,缔写“Acv\表示有效状态,“\表示尤效状态。符号“X\表示两种状态的任一种。(② 关于 M 和 N 的值见 5. 2. 2 条~W.AdMd(1)

注:见者2注(0

总线数

据宽度

(位)

设备数

据宽度

(位)

: GB/T14241—93

表3地址识别规约(N=7)

AdMd(o)

8位设备第4块

8位设备第3块

8 位设备第 2 块

8位设备第1块

共享同

-总线的不同宽度的从设备要识别的地址修改码用丁地址块识别的地址修改码

第1块

AdM(1)

注,见表2注①

第2块

AdM(1)

规则A4:请求设备应释放其Rq线,当且仅当:(a)BusGr有效,或

(b)Rs有效。

规则A5:设备应保持BuSACC有效当目付当,(ai)BusGr有效;并且

AdM(0)

第3块

(ai)其R线有效(而且不是它自已保持此线有效):并且(aili)CcBn无效,并且

(aiv)CcRes无效;并且

(av)CeFin效并且

avi)该设备未保持It线有效:月且(avii)CeAbort无效:并且

(avi)Rs无效:或

注:该主设备获得总线。

(bi)CeRcs无效并且

(bi)CeB有效,并丑

AdM(o)

H(7)H(O)

第4块

AdM(1)

AdM(u)

(bli)高速通路上的信号和对应丁一地址的字节方式线上的信号已被该设备识别,并月(biv)该设备末保持CcFin有效,并月(bv)根据规则Dla惑(在应用规则Sl后)规划Dlh,此设备准备保持EusIeallocate有效并且W(bvi)CAori无效:并且

(bvii)R效。

GB/T14241—93

注,如果一从段备企图请求裁决器撤消对当前主设备的分配,则它在CcRes之前保持BusAc有效。或者,如果它企图拒绝该周期.则飞在Rxcnllacate之前保持BusAcq有效。规则A6:作为规则A5的另--种选择,设备应保持右效,并由此启动一个中断周期,当几仪当:(i)BusGr有效:并且

(i)其Ro线有效(并且不足它自巴保持此线有效):并且(ili)它未保持BusAcq有效:并凡Gv)CeAbur无效R

(v)Rs无效。

注:士设备间裁决器发一个中断。规则A7:一设备应被锁住,当凡仪当:(a)根据规则A5a保持BusAc有效;或(b)根据规则A6保持工有效。

规则A8:裁决器应释放BusGr,当且仅当:ai)BusAc有效,并且

(aii)BusDeallocate无效,或

注!裁器应答总线我得。

(hi)I有效,许H

(bii)BusDeallocale无效,或注:裁决器应答一中断、

(i)它未保持一Rq线有效;

(ci)BusAq无效;或

注:裁决器完成撤消总线分配交接过程。(di)它保持CcAbori有效;并且(dii)BusDeallocate无效,或

(c) Rs有效。

规则A9:裁决器应释放它日前保持有效的任仰Rg线,当且仅当:(ai)Bust无效并

ali)BusA效;并

(all)瓦无效;并且

(aiv)裁决器不准备依规则A3保持BusGr有效;或浅。最后分配的主设备已完成使用总线。(bi)Bus(无效;并且

(bi):设备保持其Rg线有效;并且(bili)裁次器不推备依规划A3保持BusGr有效;或注:一设备请求分配时,另一已分配的士设备仍在使用总线。(c)Bus)eallocate有效:或

注:裁决器请求已分配的尘设备放总线以进行再分配。(d)它保持CAbort有效;或

(e)复位信号有效。

规则A10:保持Bu5Acq有效的设备应释放它,当且仅当:(ai)当前总线尚期已建立(规则M5),并几(aii)设备的Rq线有效;并且

W.

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。