GB/T 20515-2006

基本信息

标准号: GB/T 20515-2006

中文名称:半导体器件 集成电路 第5部分:半定制集成电路

标准类别:国家标准(GB)

标准状态:现行

发布日期:2006-10-10

实施日期:2007-02-01

出版语种:简体中文

下载格式:.rar.pdf

下载大小:738427

标准分类号

标准ICS号:电子学>>31.200集成电路、微电子学

中标分类号:电子元器件与信息技术>>微电路>>L56半导体集成电路

关联标准

采标情况:IEC 60748-5:1997

出版信息

出版社:中国标准出版社

页数:平装16开 页数:20, 字数:34千字

标准价格:13.0 元

计划单号:20020171-T-339

出版日期:2007-02-01

相关单位信息

首发日期:2006-10-10

起草单位:信息产业部四所

归口单位:全国半导体器件标准化技术委员会

发布部门:中华人民共和国国家质量监督检验检疫总局 中国国家标准化管理委员会

主管部门:信息产业部(电子)

标准简介

本部分为第5部分,等同采用IEC 60748-5:1997《半导体器件 集成电路 第5部分:半定制集成电路》,本部分规定了集成电路(IC)分类体系树中有关半定制集成电路子类的标准。 GB/T 20515-2006 半导体器件 集成电路 第5部分:半定制集成电路 GB/T20515-2006 标准下载解压密码:www.bzxz.net

标准图片预览

标准内容

ICS31.200

中华人民共和国国家标准

GB/T20515—2006/IEC60748-5:1997半导体器件

集成电路

第5部分:半定制集成电路

Semiconductor devices-Integrated circuits-Part 5:Semicustom integrated circuits(IEC 60748-5:1997,IDT)

2006-10-10发布

中华人民共和国国家质量监督检验检疫总局中国国家标准化管理委员会

2007-02-01实施

半导体器件集成电路系列标准包括如下标准:KAONKAca

GB/T20515-—2006/IEC60748-5:1997GB/T16464--1996半导体器件集成电路第1部分:总则(idt1EC60748-1:1984);—GB/T16465—1996膜集成电路和混合膜集成电路分规范(来用能力批准程序)(idtIEC60748-22:1992);

GB/T17574—1998

1985);

GB/T17940-2000

1986);

-IEC60748-4

半导体器件集成电路

第2部分:数字集成电路(idtIEC60748-2:半导体器件集成电路第3部分:模拟集成电路(idtIEC60748-3:半导体器件集成电路第4部分:接口集成电路;GB/T205152006半导体器件集成电路第5部分:半定制集成电路;1半导体器件集成电路第11部分:半导体集成电路分规范(不包括混合IEC6074811

电路),

膜集成电路和混合膜集成电路总规范;IEC60748-20

IEC60748-21膜集成电路和混合膜集成电路分规范(采用鉴定批准程序)。本标准为第5部分,等同采用1EC60748-5:1997《半导体器件集成电路第5部分:半定制集成路》(英文版),

为便于使用,本标准做了如下编辑性修改:a)删除国际标准中的前言。

b)已经等同转化为国家标准的引用国家标准,否则引用IEC原文。本标准由中华人民共和国信息产业部提出。本标准由全国半导体器件标准化技术委员会归口。本标准起草单位:中国电子技术标准化研究所(CESI)。本标准主要起草人:王琪。

GB/T20515—2006/IEC60748-5:1997引言

1998和GB/T16464-—1996是十分必作为一个准则,在本标准涉及到的时候,引用GB/工17573要的。在本标准中,用户将会发现所有基本信息:术语;

图形符号;

一基本额定值和特性;

功能描述;

测试方法;

接收和可靠性;

设计方面;

用户/承制方接口。

条款顺序对应于GB/T17573—1998,第Ⅱ篇,2.1分款I

1总则

1.1范围www.bzxz.net

KAONTKAca

GB/T20515-—2006/IEC60748-5.1997半导体器件集成电路

第5部分:半定制集成电路

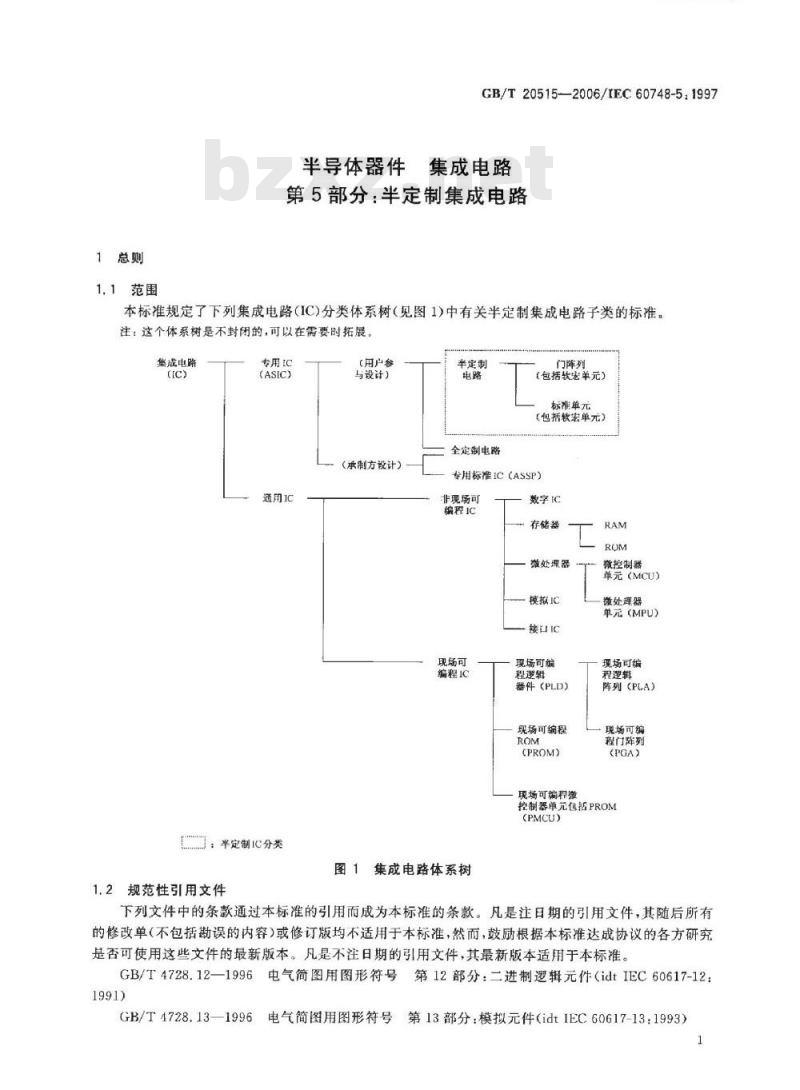

本标准规定了下列集成电路(IC)分类体系树(见图1)中有关半定制集成电路子类的标准。注:这个体系树是不封闭的,可以在需要时拓展。集成电路

专用IC

(ASIC)

通用IC

:半定制IC分类

1.2规范性引用文件

(用户参

与设计)

(承制方设计)

半定制

全定制电路

门阵列

(包括软宏单元)

标准单元

(包括软宏单元)

专用标准IC(ASSP)

非现场可

编程IC

现场可

编程IC

图1集成电路体系树

数字IC

存储器

激处理器

模拟IC

接口IC

现场可编

程逻辑

器件(PLD)

现场可编程

CPROM)

微控制器

单元(MCU)

微处理器

单元(MPU)

现场可编

程逻辑

阵列(PLA)

现场可编

程门阵列

现场可编程微

控制器单元包括PROM

(PMCU)

下列文件中的条款通过本标准的引用而成为本标准的条款。凡是注日期的引用文件,其随后所有的修改单(不包括勘误的内容)或修订版均不适用于本标准,然而,鼓励根据本标准达成协议的各方研究是否可使用这些文件的最新版本。凡是不注日期的引用文件,其最新版本适用于本标准。GB/T4728.12—1996电气简图用图形符号第12部分:二进制逻辑元件(idtIEC60617-12:1991)

GB/T4728.13—1996电气简图用图形符号第13部分:模拟元件(idtIEC60617-13:1993)1

GB/T20515—2006/IEC60748-5:1997GB/T16464-1996

半导体器件集成电路第1部分:总则(idtIEC60748-1:1984)GB/T17573—1998半导体器件分立器件和集成电路第1部分:总则(idtIEC60747-11983)GB/T17574-1998半导体器件集成电路第2部分:数字集成电路(idtIEC60748-2:1985)GB/T17940—2000半导体器件集成电路第3部分:模拟集成电路(idtIEC60748-3:1986)IEC60748-4:1987半导体器件集成电路第4部分:接口集成电路修订1:1991

修订2:1994

IEC60748-11:1990半导体器件集成电路第11部分:半导体集成电路分规范(不包括混合电路)2术语和图形符号

2.1总则

见GB/T17574--1998,第Ⅱ篇。

2.2半定制集成电路的相关术语

为特定应用而设计的一种集成电路。2.2.2

基于单元的集成电路cell-based integrated circuits选择一种或者多种预特征化的单元或宏单元集成在一块芯片上的电路,随后在自动芯片版图设计过程中与芯片上的其他电路元件连接起来实现特定的电功能。注,这个定义爱蛊了传统标准单元设计和基于单元的设计。2.2.3

半定制集成电路semicustomintegrated cireuit由预特征化的线路、单元和宏单元组成的一种集成电路,它能在自动芯片版图设计过程中被调用从而形成一个专用电路。

全定制集成电路:full customintegratedcircuit全定制IC指为一个用户设计或仅为一个应用设计的集成电路(例如一些专用无线电通信电路):2.2.5

门阵列gatearray

包含一种电路元件固定拓扑结构的一种集成电路,用于形成宏单元和宏功能,也可互连完成一个逻辑功能。

通道门阵列channelledgatearray由预特征化的电路元件(单元和/或宏单元)组成的一种门阵列,在一块芯片上被分成不同区域以用于互连。

门海sea of gates

由预特征化的电路元件(单元和/或宏单元)组成的一种门阵列,被互连电路覆盖。在一个门海版图中,互连区域通过牺牲门列产生。2.2.5.3

电路元件circuitelement

一个电路的基本组成部分,除互连外,包括电阻器、电容器和晶体管。2

单元cell

KAONKAca-

GB/T20515-2006/1EC60748-5:1997有特定版图设计和互连端能完成一个电气功能的预特征化的电路元件。2.2.6.1

标准单元standardcell

由承制方所建立固定物理的和电气特性的一种单元。2.2.6.2

基本单元basiccell

为了便于集成,由一些晶体管和无源元件组成的单元。2.2.7

宏单元macro

具有特定电气连接的单元的集成,它的特性源于它的组成单元的特性。注:这个定义包括了超级集成,它由一个或多个预特征化的大型单元或宏单元组成2.2.7.1

硬宏单元

hardmacro

特征化的固定版图和基本单元互连,以完成一种电气功能。注:特性可由生产好的器件测试产生,也可由计算机模拟产生。特性可包括以下方面:物理尺寸、逻辑功能、可测试性、版图设计规则和可靠性。

软宏单元softmacro

基本单元和/或单元连接实现一种电气功能,但是没有预定物理版图。2.2.7.3

用户的宏单元user'smacro

由用户提供的宏单元。

2.3半定制集成电路图形符号

在考虑中。

3承制方提供的半定制集成电路的基本资料3.1总则

本章给出了由承制方建立的关于半定制集成电路的最基本资料,例如门阵列或标准单元。3.2电路识别和类型

3.2.1名称和类型

如果器件属于一个功能性或电气性的分类,应该标注出。功能和电气分类可以是数字、模拟、数字和模拟或数字接口电路

3.2.2通用功能描述

当半定制集成电路可用于个系列时,应当标注出。主要功能特性包括可用门的最大数目、RAM、ROM、MPU和/或功能框图也应给出。此外,还应给出管芯尺寸和可用压焊点数目。3.2.3工艺技术

单片集成电路应当标注出例如CMOS、双极、BICMOS等工艺技术,还有互连层的类型和数目,以及CMOS的门长度和可选的(有效)沟道长度。3.3应用的相关描述

3.3.1主要应用

如果需要,应给出主要应用,对应用的任何限制都应给出。3

GB/T20515—2006/IEC60748-5:19973.3.2包装识别

应该标注出IEC和/或国家外形图参考编号或非标准封装图,包括引出端编号和主要封装材料,例如:陶瓷、塑料等。应给出每一个封装的最小和最大芯片尺寸范围。如果需要还应给出热阻。3.4库单元功能描述的规定

3.4.1基本单元的详细框图(单元特性)应在应用数据手册或设计指南包括其修订本中给出基本单元的功能。基本单元的详细框图或等效电路信息也应给出。关于功能,下列每一个出版物中对应的第Ⅲ篇给出描述:GB/T17574一1998,GB/T17940一2000和IEC60748-4。功能用图形符号也应给出。这也可以从标准图形符号手册或GB/T4728.12或GB/T4728.13获得。3.4.1.1硬宏单元

应描述硬宏单元的主要功能,并列出所有硬宏单元,包括物理尺寸。也应给出所有附加信息,例如硬宏单元的可用数目和可能安置位置。3.4.1.2软宏单元

应描述软宏单元的主要功能,不同基本单元的数目也应给出。3.4.2引出端识别和功能

应标注出每一个预定义的引出端,对应用的限制也应给出3.5极限值(绝对最大额定值体系)除另有规定外,这些值适用于全工作温度范围。极限值并不用于检验。除另有规定外,应给出以下极限值:应包括集成电路特有的任何告警状态。若有相互关联的被限值存在应给出。极限值应用的所有条件都应给出。若有外部连接和/或接触单元,例如,热沉,影响到额定值,带单元连接和/或接触的集成电路额定值应描述出。如果引用最小和/或最大值,应表明它们是绝对值还是代数值。若允许瞬时过载,应给出幅度和持续时间。

所有电压以一个确定参考端为基准(Vs、GND等)表1极限值示例

电源电压

电源电流,适用时

输人电压

输入电流

强制输出电压

输出电流

贮存温度

结温,适用时

耐焊接温度,适用时

焊接持续时间,适用时

VoeVo,Vss,Ve

Ioe,Ipo,Iss,e

Vo(强制)

适用时,应给出其他极限条件例如电流持续时间、频率、安装方法、额定值依靠的温度等。适用时,应给出最大蔚焊接温度。4

3.6推荐工作条件(在规定工作温度范围内)这些条件不作为检验项目,但可用于质量评定的工作条件。所有电压以一个确定参考端为基准(Vss,GND等)。YKAOKAca

GB/T20515-2006/IEC60748-5:1997表2推荐工作条件示例

电源电压

低电平输人电压

高电平输入电压

输人上升和下降时间

工作温度

Tamb和/或Ta

注:适用时,任何其他工作条件,例如频率和负载电流,根据GB/T17574-1998,GB/T17940--2000和IEC60748-4给出。

3.7库单元电特性

除另有规定外,电特性适用于全工作温度范围和电源电压。电路指定参数在工作温度范围内变化的,应给出25℃下和高、低温下的输入,输出电压值和对应的电流。应给出每个不同功能类型的输入和/或输出对应的电流和电压值。应给出特性和时序或其他要求。3.7.1静态特性

所有电压以一个确定参考端为基准。表3

3静态特性示例

电源电流,工作时

静态电源电流

施密特触发正向阅值,适用时

施密特触发负向阈值,适用时

施密特滞后,适用时

低电平输出电压

高电平输出电压

低电平输入电流

高电平输入电流

带上拉/下拉的输人电流

带上拉/下拉的输人电流

输出漏电流,适用时

输出漏电流,适用时

测试条件

Ve-GND,VH=VcC.

V,=GNDVm=VEam

V=GND.Vu-VDD.m

应给出频率(时钟输入),输人和输出条件(例如不激活InDo的上拉和下拉)

Vi=Vpp

Vi=-Vop

V。ov

Vo=Vuu

应给出对应特性的人和输出宏单元的名称。最小

GB/T205152006/IEC60748-5:19973.7.2动态特性

从外部输人到外部输出的传输延迟依靠布局和互连布线,内部阻抗和内部电容,还有基本单元固有的传输延迟。「应在一张表中给出传输延迟的估计值,还应对这些值进行验证。3.7.3时序图

时序图应表明所有关联的输人和输出。时序图由一个或多个图组成,这些图表明两个或更多信号间内部关系。应给出例如建立和保持时问这样的时序要求。见图2给出的时序图示例。例

时钟信号

输入信号组1

输入信号组2,等

输出信号

所有或不网输出选通

3.7.4电容

宏名·

输人电容

输入/输出电容

输出电容

Cor/oct

XXXXXXX

图2时序图示例

电容示例

测试条件

应给出对应特性的输人和输出宏单元的名称。3.8附加资料

应给出对应于检验条件的静电放电资料。参照GB/T175741998,第Ⅲ篇,5.5条和6.3条给出CMOS锁定特性的资料,也可参见1EC60748-11:1990中10.9。测试方法

4.1总则

除另有规定外,GB/T16464—1996,第班篇结合GB/T17573—1998,第切篇,第1节、第2节。6

4.2特殊要求

下列条款中描述的方法适用于技术试验路线:GB/T17574-1998,第V篇,第1节,第2条;-GB/T17940一2000第IV篇,第1节,第2条;-IEC60748-4:1987,第V章,第1节,第2条。4.3静态特性

KAONTKAca

GB/T20515-—2006/IEC60748-5:1997见GB/T17574-1998GB/T17940—2000和IEC607484:1987中相关要点。4.4动态特性

见GB/T17574—1998GB/T17940—-2000和IEC60748-4:1987中相关要点。5接收和可靠性

5.1电耐久性试验

5.1.1总则

见GB/T16464—1996,第谨篇,第3节,第2条和IEC60748-11。5.1.2特殊要求

见GB/T16464—1996,第篇,第3节,第3条和IEC60748-11。5.2环境试验

见相关IEC出版物。

5.3失效分析程序

见相关IEC出版物。

6设计方面

6.1总则

本条款列出实现半定制IC功能所需要的设计信息,例如,其中应提供的数据或信息安排的形式(如数据手册或设计手册),及提供方(如用户或承制方)。文件将由用户或承制方提供,根据第7章选择接口级。6.2库(由承制方批准)

应给出库的版本,所有单元和宏单元的库应按照下列几项加以描述。每个单元电路的图形符号:

\功能描述(例如逻辑图,真值表);所有相关静态和动态电特性,包括输出负载能力、输人负载因子、静态和动态功耗等;详细电路图,包括晶体管尺寸;带有全部独特结构的单元版图设计;根据几何、功能、电气和时序检查来描述单元库模拟验证。6.3计算机辅助工程(CAE)设计硬件应给出CAE硬件(例如工作站、操作系统及其版本号、存储器要求、局域网、主机等)的描述和结构列表。

6.4CAE设计软件

6.4.1CAE设计系统

给出软件包的列表,包括名称、版本、制造厂、描述语言数据格式等。CAE系统将包括下面部分或7

GB/T20515—2006/IEC60748-5:1997所有的工具,对它们所包含的内容并不加限制。a)电路图输人:使用能以特定格式产生网表的图形编辑器将半定制IC的电路图输入到CAE系统中。

b)综合:电路图能从半定制IC的功能措述或通过特定编译器编译的功能模块(例如布尔方程)中产生。编译器必须产生一种特定格式的电路图信息,且被CAE系统的其他工具所接收。综合工具也应该包括工艺拓扑结构方面的内容。模拟:半定制IC的功能可以用一个模拟程序来验证,该模拟程序接受表征设计的输入网表,还c)

接受表征应用的一系列测试向量。电路的逻辑响应和交流性能,在布局布线前用预估负载,而在布局布线后用从版图中提取的负载并进行反标注,能在不同的测试条件(最好情况、典型情况、最坏情况)下进行评价。

d)时序分析:传输延迟由一个程序来决定,该程序能将沿所有信号通道的带负载的独立元件的延迟叠加起来,且能报告用户建立的判据。e)工程规则检查:为确定半定制IC是否能够投人生产,工艺(例如某些并行或“线或”连接的输出端口,某些电源电压引出端等)采用的设计准则的兼容性,均由包含承制方要求的检查程序验证(这种工具通常由承制方提供)。可测性设计检查:通过特定的软件工具可以检测包含测试策略(如扫描通道,LSSD,边界扫描f

等)的设计结构的兼容性。

自动测试图形生成:用于产生测试程序的图形可以通过在格式上与CAE系统中其他工具兼g

容的特定丁具产生。

故障分级:故障分级是对半定制IC设计中那些被电子测试程序读取和激活的节点的统计评h)

估。在半定制IC用户和承制方之间就能接受的最小故障覆盖值达成一致。版图(布局布线):将半定制IC中的库单元布局在硅片的表面,并用专门的版图设计程序连接。这些程序将产生关于版图设计的信息,其格式与生产工具兼容。设计规则检查:可由专用程序检查受到制造约束(例如在硅片上可实现的最小几何图形及其间1

的最小间距等)的版图设计的正确性。并将可能出现的错误信息和警告文件化。6.4.2CAE软件质量和升级

每个供应商应对其设计软件工具的改版和升级所采用的方法提供说明。用户可以要求获得这些升级和改版的方法说明。供应商应该对用户正在使用的软件或商业供应的软件工具包是否进行改版升级的测试方法进行概述或描述有关的方法。该要求仅适用于承制方面向应用设计过程所使用的软件工具包。针对系统设计公司或外部设计公司使用的部分设计工具(如电原理图输入)或非承制方的软件工具,应当有相应的处理。

注:为保证CAE软件升级后的质量请参阅相关的质量评估程序。7用户/承制方接口

7.1用户/承制方设计接口的概念在半定制集成电路领域,用户和承制方在很多阶段有接口,下列表5的流程图说明了接口可能发生的典型设计点。这种设计接口不含盖任何一方的责任。8

接口级别

功能级接口

遥辑级接口

电路级接口

版图级接口

模级接口

工程样品级接口

系统设计

iiKAONYKAca-

GB/T20515--2006/IEC60748-5:1997表5用户和承制方之间的典型接口级接口级别

承制方

逻辑设计

布局布线

后模撒

掩模和工

程制作

封装和测试

(工程

样品)

7.2用户/承制方典型接口文件

下列表6所示的文件,示例格式见附录A。支持工具

设计手册

功能说明

工程工作站

CAE系统

承制方

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。

中华人民共和国国家标准

GB/T20515—2006/IEC60748-5:1997半导体器件

集成电路

第5部分:半定制集成电路

Semiconductor devices-Integrated circuits-Part 5:Semicustom integrated circuits(IEC 60748-5:1997,IDT)

2006-10-10发布

中华人民共和国国家质量监督检验检疫总局中国国家标准化管理委员会

2007-02-01实施

半导体器件集成电路系列标准包括如下标准:KAONKAca

GB/T20515-—2006/IEC60748-5:1997GB/T16464--1996半导体器件集成电路第1部分:总则(idt1EC60748-1:1984);—GB/T16465—1996膜集成电路和混合膜集成电路分规范(来用能力批准程序)(idtIEC60748-22:1992);

GB/T17574—1998

1985);

GB/T17940-2000

1986);

-IEC60748-4

半导体器件集成电路

第2部分:数字集成电路(idtIEC60748-2:半导体器件集成电路第3部分:模拟集成电路(idtIEC60748-3:半导体器件集成电路第4部分:接口集成电路;GB/T205152006半导体器件集成电路第5部分:半定制集成电路;1半导体器件集成电路第11部分:半导体集成电路分规范(不包括混合IEC6074811

电路),

膜集成电路和混合膜集成电路总规范;IEC60748-20

IEC60748-21膜集成电路和混合膜集成电路分规范(采用鉴定批准程序)。本标准为第5部分,等同采用1EC60748-5:1997《半导体器件集成电路第5部分:半定制集成路》(英文版),

为便于使用,本标准做了如下编辑性修改:a)删除国际标准中的前言。

b)已经等同转化为国家标准的引用国家标准,否则引用IEC原文。本标准由中华人民共和国信息产业部提出。本标准由全国半导体器件标准化技术委员会归口。本标准起草单位:中国电子技术标准化研究所(CESI)。本标准主要起草人:王琪。

GB/T20515—2006/IEC60748-5:1997引言

1998和GB/T16464-—1996是十分必作为一个准则,在本标准涉及到的时候,引用GB/工17573要的。在本标准中,用户将会发现所有基本信息:术语;

图形符号;

一基本额定值和特性;

功能描述;

测试方法;

接收和可靠性;

设计方面;

用户/承制方接口。

条款顺序对应于GB/T17573—1998,第Ⅱ篇,2.1分款I

1总则

1.1范围www.bzxz.net

KAONTKAca

GB/T20515-—2006/IEC60748-5.1997半导体器件集成电路

第5部分:半定制集成电路

本标准规定了下列集成电路(IC)分类体系树(见图1)中有关半定制集成电路子类的标准。注:这个体系树是不封闭的,可以在需要时拓展。集成电路

专用IC

(ASIC)

通用IC

:半定制IC分类

1.2规范性引用文件

(用户参

与设计)

(承制方设计)

半定制

全定制电路

门阵列

(包括软宏单元)

标准单元

(包括软宏单元)

专用标准IC(ASSP)

非现场可

编程IC

现场可

编程IC

图1集成电路体系树

数字IC

存储器

激处理器

模拟IC

接口IC

现场可编

程逻辑

器件(PLD)

现场可编程

CPROM)

微控制器

单元(MCU)

微处理器

单元(MPU)

现场可编

程逻辑

阵列(PLA)

现场可编

程门阵列

现场可编程微

控制器单元包括PROM

(PMCU)

下列文件中的条款通过本标准的引用而成为本标准的条款。凡是注日期的引用文件,其随后所有的修改单(不包括勘误的内容)或修订版均不适用于本标准,然而,鼓励根据本标准达成协议的各方研究是否可使用这些文件的最新版本。凡是不注日期的引用文件,其最新版本适用于本标准。GB/T4728.12—1996电气简图用图形符号第12部分:二进制逻辑元件(idtIEC60617-12:1991)

GB/T4728.13—1996电气简图用图形符号第13部分:模拟元件(idtIEC60617-13:1993)1

GB/T20515—2006/IEC60748-5:1997GB/T16464-1996

半导体器件集成电路第1部分:总则(idtIEC60748-1:1984)GB/T17573—1998半导体器件分立器件和集成电路第1部分:总则(idtIEC60747-11983)GB/T17574-1998半导体器件集成电路第2部分:数字集成电路(idtIEC60748-2:1985)GB/T17940—2000半导体器件集成电路第3部分:模拟集成电路(idtIEC60748-3:1986)IEC60748-4:1987半导体器件集成电路第4部分:接口集成电路修订1:1991

修订2:1994

IEC60748-11:1990半导体器件集成电路第11部分:半导体集成电路分规范(不包括混合电路)2术语和图形符号

2.1总则

见GB/T17574--1998,第Ⅱ篇。

2.2半定制集成电路的相关术语

为特定应用而设计的一种集成电路。2.2.2

基于单元的集成电路cell-based integrated circuits选择一种或者多种预特征化的单元或宏单元集成在一块芯片上的电路,随后在自动芯片版图设计过程中与芯片上的其他电路元件连接起来实现特定的电功能。注,这个定义爱蛊了传统标准单元设计和基于单元的设计。2.2.3

半定制集成电路semicustomintegrated cireuit由预特征化的线路、单元和宏单元组成的一种集成电路,它能在自动芯片版图设计过程中被调用从而形成一个专用电路。

全定制集成电路:full customintegratedcircuit全定制IC指为一个用户设计或仅为一个应用设计的集成电路(例如一些专用无线电通信电路):2.2.5

门阵列gatearray

包含一种电路元件固定拓扑结构的一种集成电路,用于形成宏单元和宏功能,也可互连完成一个逻辑功能。

通道门阵列channelledgatearray由预特征化的电路元件(单元和/或宏单元)组成的一种门阵列,在一块芯片上被分成不同区域以用于互连。

门海sea of gates

由预特征化的电路元件(单元和/或宏单元)组成的一种门阵列,被互连电路覆盖。在一个门海版图中,互连区域通过牺牲门列产生。2.2.5.3

电路元件circuitelement

一个电路的基本组成部分,除互连外,包括电阻器、电容器和晶体管。2

单元cell

KAONKAca-

GB/T20515-2006/1EC60748-5:1997有特定版图设计和互连端能完成一个电气功能的预特征化的电路元件。2.2.6.1

标准单元standardcell

由承制方所建立固定物理的和电气特性的一种单元。2.2.6.2

基本单元basiccell

为了便于集成,由一些晶体管和无源元件组成的单元。2.2.7

宏单元macro

具有特定电气连接的单元的集成,它的特性源于它的组成单元的特性。注:这个定义包括了超级集成,它由一个或多个预特征化的大型单元或宏单元组成2.2.7.1

硬宏单元

hardmacro

特征化的固定版图和基本单元互连,以完成一种电气功能。注:特性可由生产好的器件测试产生,也可由计算机模拟产生。特性可包括以下方面:物理尺寸、逻辑功能、可测试性、版图设计规则和可靠性。

软宏单元softmacro

基本单元和/或单元连接实现一种电气功能,但是没有预定物理版图。2.2.7.3

用户的宏单元user'smacro

由用户提供的宏单元。

2.3半定制集成电路图形符号

在考虑中。

3承制方提供的半定制集成电路的基本资料3.1总则

本章给出了由承制方建立的关于半定制集成电路的最基本资料,例如门阵列或标准单元。3.2电路识别和类型

3.2.1名称和类型

如果器件属于一个功能性或电气性的分类,应该标注出。功能和电气分类可以是数字、模拟、数字和模拟或数字接口电路

3.2.2通用功能描述

当半定制集成电路可用于个系列时,应当标注出。主要功能特性包括可用门的最大数目、RAM、ROM、MPU和/或功能框图也应给出。此外,还应给出管芯尺寸和可用压焊点数目。3.2.3工艺技术

单片集成电路应当标注出例如CMOS、双极、BICMOS等工艺技术,还有互连层的类型和数目,以及CMOS的门长度和可选的(有效)沟道长度。3.3应用的相关描述

3.3.1主要应用

如果需要,应给出主要应用,对应用的任何限制都应给出。3

GB/T20515—2006/IEC60748-5:19973.3.2包装识别

应该标注出IEC和/或国家外形图参考编号或非标准封装图,包括引出端编号和主要封装材料,例如:陶瓷、塑料等。应给出每一个封装的最小和最大芯片尺寸范围。如果需要还应给出热阻。3.4库单元功能描述的规定

3.4.1基本单元的详细框图(单元特性)应在应用数据手册或设计指南包括其修订本中给出基本单元的功能。基本单元的详细框图或等效电路信息也应给出。关于功能,下列每一个出版物中对应的第Ⅲ篇给出描述:GB/T17574一1998,GB/T17940一2000和IEC60748-4。功能用图形符号也应给出。这也可以从标准图形符号手册或GB/T4728.12或GB/T4728.13获得。3.4.1.1硬宏单元

应描述硬宏单元的主要功能,并列出所有硬宏单元,包括物理尺寸。也应给出所有附加信息,例如硬宏单元的可用数目和可能安置位置。3.4.1.2软宏单元

应描述软宏单元的主要功能,不同基本单元的数目也应给出。3.4.2引出端识别和功能

应标注出每一个预定义的引出端,对应用的限制也应给出3.5极限值(绝对最大额定值体系)除另有规定外,这些值适用于全工作温度范围。极限值并不用于检验。除另有规定外,应给出以下极限值:应包括集成电路特有的任何告警状态。若有相互关联的被限值存在应给出。极限值应用的所有条件都应给出。若有外部连接和/或接触单元,例如,热沉,影响到额定值,带单元连接和/或接触的集成电路额定值应描述出。如果引用最小和/或最大值,应表明它们是绝对值还是代数值。若允许瞬时过载,应给出幅度和持续时间。

所有电压以一个确定参考端为基准(Vs、GND等)表1极限值示例

电源电压

电源电流,适用时

输人电压

输入电流

强制输出电压

输出电流

贮存温度

结温,适用时

耐焊接温度,适用时

焊接持续时间,适用时

VoeVo,Vss,Ve

Ioe,Ipo,Iss,e

Vo(强制)

适用时,应给出其他极限条件例如电流持续时间、频率、安装方法、额定值依靠的温度等。适用时,应给出最大蔚焊接温度。4

3.6推荐工作条件(在规定工作温度范围内)这些条件不作为检验项目,但可用于质量评定的工作条件。所有电压以一个确定参考端为基准(Vss,GND等)。YKAOKAca

GB/T20515-2006/IEC60748-5:1997表2推荐工作条件示例

电源电压

低电平输人电压

高电平输入电压

输人上升和下降时间

工作温度

Tamb和/或Ta

注:适用时,任何其他工作条件,例如频率和负载电流,根据GB/T17574-1998,GB/T17940--2000和IEC60748-4给出。

3.7库单元电特性

除另有规定外,电特性适用于全工作温度范围和电源电压。电路指定参数在工作温度范围内变化的,应给出25℃下和高、低温下的输入,输出电压值和对应的电流。应给出每个不同功能类型的输入和/或输出对应的电流和电压值。应给出特性和时序或其他要求。3.7.1静态特性

所有电压以一个确定参考端为基准。表3

3静态特性示例

电源电流,工作时

静态电源电流

施密特触发正向阅值,适用时

施密特触发负向阈值,适用时

施密特滞后,适用时

低电平输出电压

高电平输出电压

低电平输入电流

高电平输入电流

带上拉/下拉的输人电流

带上拉/下拉的输人电流

输出漏电流,适用时

输出漏电流,适用时

测试条件

Ve-GND,VH=VcC.

V,=GNDVm=VEam

V=GND.Vu-VDD.m

应给出频率(时钟输入),输人和输出条件(例如不激活InDo的上拉和下拉)

Vi=Vpp

Vi=-Vop

V。ov

Vo=Vuu

应给出对应特性的人和输出宏单元的名称。最小

GB/T205152006/IEC60748-5:19973.7.2动态特性

从外部输人到外部输出的传输延迟依靠布局和互连布线,内部阻抗和内部电容,还有基本单元固有的传输延迟。「应在一张表中给出传输延迟的估计值,还应对这些值进行验证。3.7.3时序图

时序图应表明所有关联的输人和输出。时序图由一个或多个图组成,这些图表明两个或更多信号间内部关系。应给出例如建立和保持时问这样的时序要求。见图2给出的时序图示例。例

时钟信号

输入信号组1

输入信号组2,等

输出信号

所有或不网输出选通

3.7.4电容

宏名·

输人电容

输入/输出电容

输出电容

Cor/oct

XXXXXXX

图2时序图示例

电容示例

测试条件

应给出对应特性的输人和输出宏单元的名称。3.8附加资料

应给出对应于检验条件的静电放电资料。参照GB/T175741998,第Ⅲ篇,5.5条和6.3条给出CMOS锁定特性的资料,也可参见1EC60748-11:1990中10.9。测试方法

4.1总则

除另有规定外,GB/T16464—1996,第班篇结合GB/T17573—1998,第切篇,第1节、第2节。6

4.2特殊要求

下列条款中描述的方法适用于技术试验路线:GB/T17574-1998,第V篇,第1节,第2条;-GB/T17940一2000第IV篇,第1节,第2条;-IEC60748-4:1987,第V章,第1节,第2条。4.3静态特性

KAONTKAca

GB/T20515-—2006/IEC60748-5:1997见GB/T17574-1998GB/T17940—2000和IEC607484:1987中相关要点。4.4动态特性

见GB/T17574—1998GB/T17940—-2000和IEC60748-4:1987中相关要点。5接收和可靠性

5.1电耐久性试验

5.1.1总则

见GB/T16464—1996,第谨篇,第3节,第2条和IEC60748-11。5.1.2特殊要求

见GB/T16464—1996,第篇,第3节,第3条和IEC60748-11。5.2环境试验

见相关IEC出版物。

5.3失效分析程序

见相关IEC出版物。

6设计方面

6.1总则

本条款列出实现半定制IC功能所需要的设计信息,例如,其中应提供的数据或信息安排的形式(如数据手册或设计手册),及提供方(如用户或承制方)。文件将由用户或承制方提供,根据第7章选择接口级。6.2库(由承制方批准)

应给出库的版本,所有单元和宏单元的库应按照下列几项加以描述。每个单元电路的图形符号:

\功能描述(例如逻辑图,真值表);所有相关静态和动态电特性,包括输出负载能力、输人负载因子、静态和动态功耗等;详细电路图,包括晶体管尺寸;带有全部独特结构的单元版图设计;根据几何、功能、电气和时序检查来描述单元库模拟验证。6.3计算机辅助工程(CAE)设计硬件应给出CAE硬件(例如工作站、操作系统及其版本号、存储器要求、局域网、主机等)的描述和结构列表。

6.4CAE设计软件

6.4.1CAE设计系统

给出软件包的列表,包括名称、版本、制造厂、描述语言数据格式等。CAE系统将包括下面部分或7

GB/T20515—2006/IEC60748-5:1997所有的工具,对它们所包含的内容并不加限制。a)电路图输人:使用能以特定格式产生网表的图形编辑器将半定制IC的电路图输入到CAE系统中。

b)综合:电路图能从半定制IC的功能措述或通过特定编译器编译的功能模块(例如布尔方程)中产生。编译器必须产生一种特定格式的电路图信息,且被CAE系统的其他工具所接收。综合工具也应该包括工艺拓扑结构方面的内容。模拟:半定制IC的功能可以用一个模拟程序来验证,该模拟程序接受表征设计的输入网表,还c)

接受表征应用的一系列测试向量。电路的逻辑响应和交流性能,在布局布线前用预估负载,而在布局布线后用从版图中提取的负载并进行反标注,能在不同的测试条件(最好情况、典型情况、最坏情况)下进行评价。

d)时序分析:传输延迟由一个程序来决定,该程序能将沿所有信号通道的带负载的独立元件的延迟叠加起来,且能报告用户建立的判据。e)工程规则检查:为确定半定制IC是否能够投人生产,工艺(例如某些并行或“线或”连接的输出端口,某些电源电压引出端等)采用的设计准则的兼容性,均由包含承制方要求的检查程序验证(这种工具通常由承制方提供)。可测性设计检查:通过特定的软件工具可以检测包含测试策略(如扫描通道,LSSD,边界扫描f

等)的设计结构的兼容性。

自动测试图形生成:用于产生测试程序的图形可以通过在格式上与CAE系统中其他工具兼g

容的特定丁具产生。

故障分级:故障分级是对半定制IC设计中那些被电子测试程序读取和激活的节点的统计评h)

估。在半定制IC用户和承制方之间就能接受的最小故障覆盖值达成一致。版图(布局布线):将半定制IC中的库单元布局在硅片的表面,并用专门的版图设计程序连接。这些程序将产生关于版图设计的信息,其格式与生产工具兼容。设计规则检查:可由专用程序检查受到制造约束(例如在硅片上可实现的最小几何图形及其间1

的最小间距等)的版图设计的正确性。并将可能出现的错误信息和警告文件化。6.4.2CAE软件质量和升级

每个供应商应对其设计软件工具的改版和升级所采用的方法提供说明。用户可以要求获得这些升级和改版的方法说明。供应商应该对用户正在使用的软件或商业供应的软件工具包是否进行改版升级的测试方法进行概述或描述有关的方法。该要求仅适用于承制方面向应用设计过程所使用的软件工具包。针对系统设计公司或外部设计公司使用的部分设计工具(如电原理图输入)或非承制方的软件工具,应当有相应的处理。

注:为保证CAE软件升级后的质量请参阅相关的质量评估程序。7用户/承制方接口

7.1用户/承制方设计接口的概念在半定制集成电路领域,用户和承制方在很多阶段有接口,下列表5的流程图说明了接口可能发生的典型设计点。这种设计接口不含盖任何一方的责任。8

接口级别

功能级接口

遥辑级接口

电路级接口

版图级接口

模级接口

工程样品级接口

系统设计

iiKAONYKAca-

GB/T20515--2006/IEC60748-5:1997表5用户和承制方之间的典型接口级接口级别

承制方

逻辑设计

布局布线

后模撒

掩模和工

程制作

封装和测试

(工程

样品)

7.2用户/承制方典型接口文件

下列表6所示的文件,示例格式见附录A。支持工具

设计手册

功能说明

工程工作站

CAE系统

承制方

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。