GB/T 15275-1994

基本信息

标准号: GB/T 15275-1994

中文名称:8位微型计算机STD总线

标准类别:国家标准(GB)

标准状态:已作废

发布日期:1994-01-02

实施日期:1995-08-01

作废日期:2005-10-14

出版语种:简体中文

下载格式:.rar.pdf

下载大小:1365066

标准分类号

标准ICS号:信息技术、办公机械设备>>35.160微处理机系统

中标分类号:电子元器件与信息技术>>计算机>>L65系统设备接口

出版信息

页数:平装16开, 页数:42, 字数:78千字

标准价格:19.0 元

相关单位信息

复审日期:2004-10-14

起草单位:中国计算机系统工程公司

归口单位:全国信息技术标准化技术委员会

发布部门:国家技术监督局

主管部门:国家标准化管理委员会

标准简介

本标准规定的内容:a.模板尺寸;b.总线连接器;c.总线引脚分配;d.信号定义;e.电气要求;f.读/写定时时序;g.读/写时间宽度参数;本标准没有规定的内容:a.模板功能;b.用户接口;c.互换性;d.母板设计。本标准适用于8位微处理器,16位微处理器总线的实现亦可参照本标准。 GB/T 15275-1994 8位微型计算机STD总线 GB/T15275-1994 标准下载解压密码:www.bzxz.net

标准图片预览

标准内容

中华人民共和国国家标准

8位微型计算机STD总线

Standard for an 8-bit

micrncanputer bus sysiem,STD bus1主题内客与适用范围

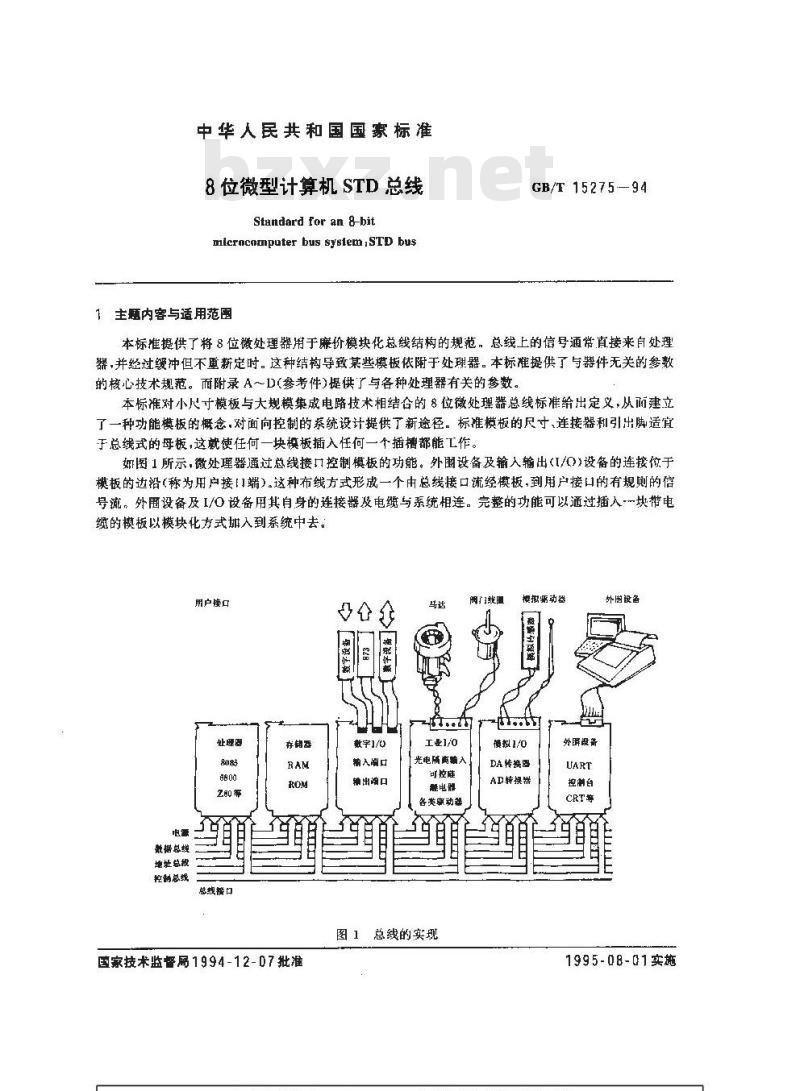

GB/T 15275—94

本标准提供了将8位微处理器用于廉价模块化总线结构的规范。总线上的信号通带直接来自处理器,并经过缓冲但不新定时。这种结构导致某些模板依附于处理器。本标准提供了与器件无关的参数的核心技术规范。而附录A~D(参考件)提供了与各种处理器有关的参数。本标准对小尺寸模板与大规模集成电路技术相结合的8位微处理器总线标准给出定义,从而建立了一种功能模板的概念,对面向控制的系统设计提供了新途径。标准模板的尺寸、连接器利引出脚适宜于总线式的母板,这就使任何一块模板插入任何一个插槽都能亡作。如图1所示,微处理器通过总线接口控制模板的功能。外围设备及输入输出(I/O)设备的连接位于模板的边沿(称为用户接门端)。这种布线方式形成一个由总线接口流经模板,到用户接口的有规则的信号流,外围设备及/O设备用其自身的连接器及电缆与系统相连。完整的功能可以通过插入一块带电缆的模板以模块化方式加人到系统中去。用户接口

处理器

Z80弄

地址总议

控制总线

总规播口

存销器

国家技术监督局1994-12-D7批准2

数字1/0

输人遍口

输出湖口

工业1/0

光电隔商物入

可控硅

醒电器

各美甄动裸

图1总线的实现

阀门线圈

提抵骊动器

报170

DA转换器

AD转摄器

外解设备

控制白

CRT等

外用段备

1995-08-01实施

主题内容

本标准规定的内容:

模板尺寸;

总线连接器:

总线引脚分配:

信号定义;

电气要求,

读/写时时序:

读/写时间宽度参数。

本标准没有规定的内容:

模板功能,

用户接口;

c.H换性;

母板设计。

1.2适用范\

GB/T 15275

5—94

本标准适用于8位微处理器,16位微处理器总线的实现亦可参照本标准。1. 3 定义

认定 assert

将信号置为逻辑“1”状态。

母板 backplane

包括连接器及互连走线的印制电路板。模板 card

国印制电路板及元器件组成的模块,此模块可以插到母板上。主板 master

控制总线信号传输的模板为主板,而正在控制总线的主板为当前主板,主管其他主板的模扳刘水久主板,除永久主板外,其他主板都是临时主板。从板slave

响应总线信号传输的模板为从板。2逻辑规范

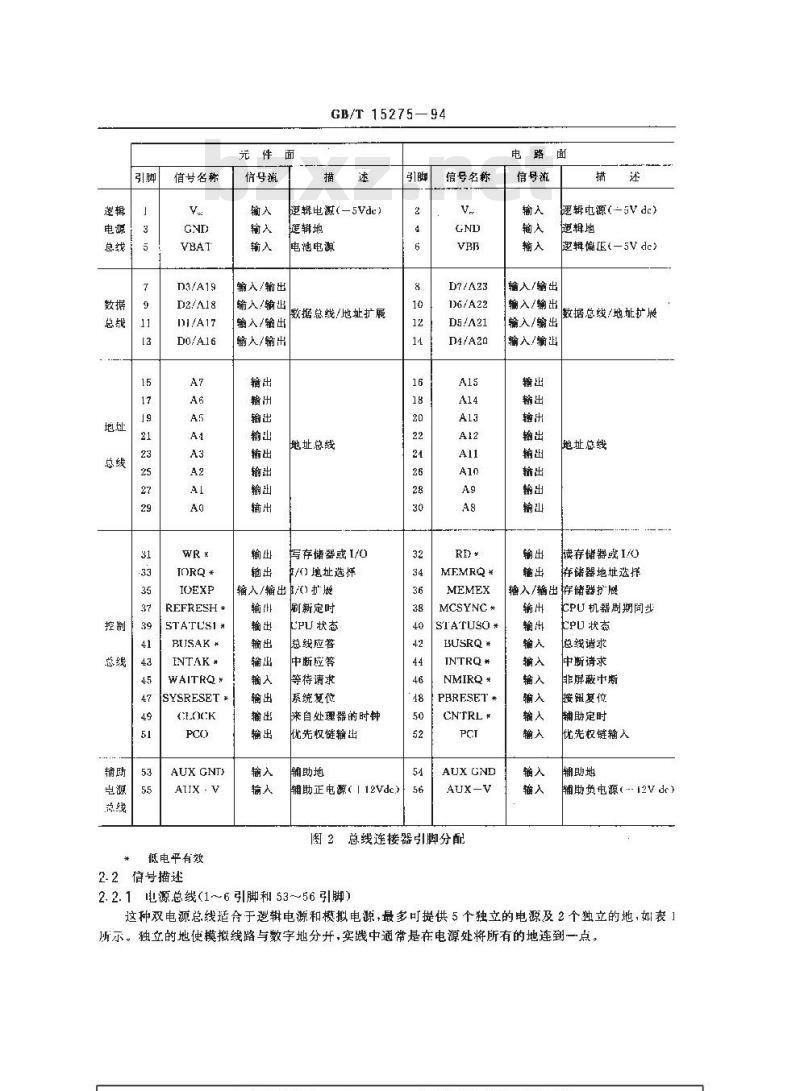

2.1总线引脚分配

总线引脚编排成如下五个功能组,如图2所示。信号流向以当前主板为参考,逻辑电源总线:

数据总线:

地址总线:

控制总线:

辅助电源总线:

采用说明:

1~6引脚

7~14引脚

15~30引脚

31~52 引脚

53~~56引脚

:] 本条内容是按照 GB 1. 1 对 IEEE Std 961 的补充。辑

控制39

信号名称

D3/A19

D2/A18

D0/A16

REFRESH *

STATLS1*

BUSAK*

INTAK *

WAITRQ*

SYSRESET*

AUX GNT)

低电平有效

2-2信号描述

元件面

信号流

GB/T15275—94

逆辑电源(-5Vde)

遥辑地

电池电源

输入/输出

输人/输出

输入/输出

输人/输出

数据总线/地址扩展

地址总线

泻存储器或1/0

/地址选择

输入/输出/0扩展

刷新定吋

EPU状态

总线应答

中断应答

等待请求

系统复位

来自处理器的时钟

优先权链输出

潮助地

辅助正电源(112Vde)

信号名称

D7/A23

1G/A22

D5/A21

D4/A2白

MEMRQ*

MCSYNC*

STATUSO*

BUSRQ*

INTRQ*

NMIRQ*

48PBRESET*

CNTRL*

AUX GND

图2总线连接器引脚分配

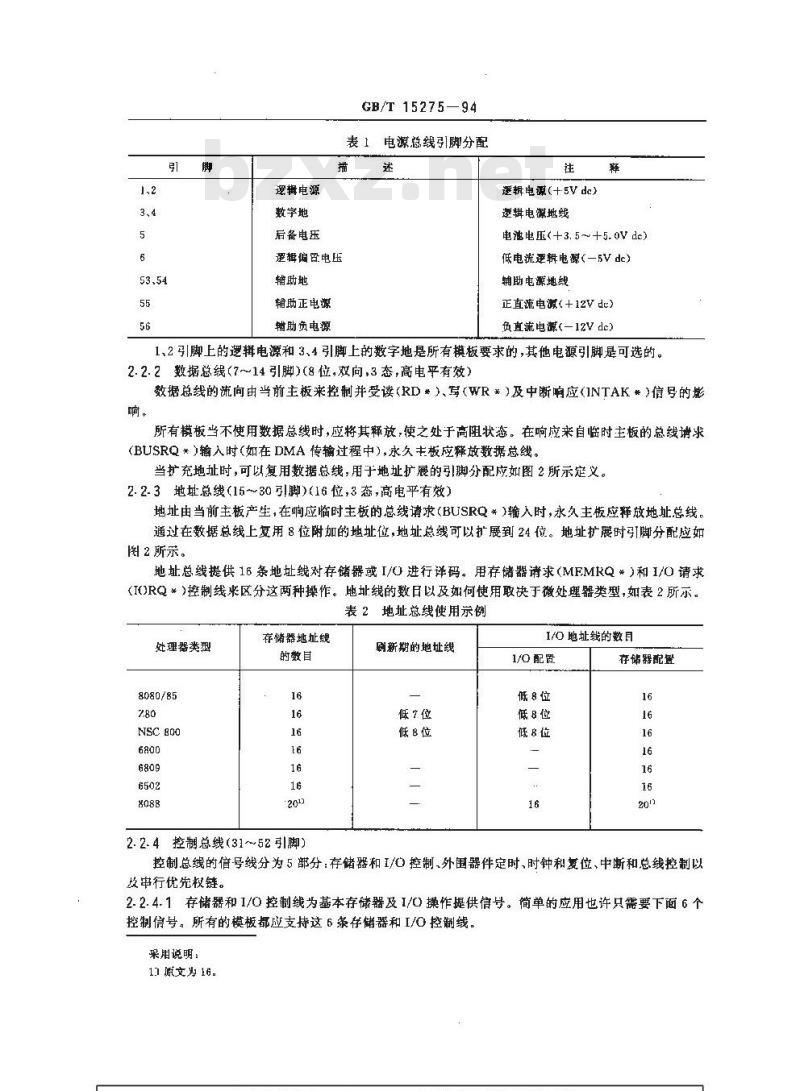

2.2.1电源总线(1~6引脚利53~56引脚)电路面

信号流

输入/输出

输入/输出

辑电源(-5Vdc)

趣辑地

趣辑偏医(—5Vde)

数据总线/地址扩展

输入/输出

输入/输出

地址总线

读存储器或1/0

存储器地址选择

辙入/輪出存储器扩展

KPU机器周期同步

PU状态

说线请求

中断请求

非屏蔽中断

接钮复位

辅助定时

优先权链输入

辅肥地

翻助负电源(--12Vdc)

这种双电源总线合于逻辑电源和模拟电源,最多可提供5个独立的电源及2个独立的地,表1所示。独立的地使模拟线路与数字地分开,实践中通常是在电源处将所有的地连到一点。1、2

逻辑电源

数字地

后备电压

GB/T15275—94

表1电源总线引脚分配

遥辑偏电压

辅助地

辅助正电源

辅助负电源

遥辑电源(+5V de)

逐辑电源地线

电池电压(+3.5~+5.0v dc)

低电流逆辑电源(-5V de)

辅助电源地线

正直流电激(+12Vde)

负直流电源(—12V de)

1、2引脚上的逻辑电源和3、4引脚上的数字地是所有模板要求的,其他电源引脚是可选的。2.2.2数据总线(7~14引脚)(8位,双向,3态,高电平有效)数据总线的流向由当前主板来控制并受读(RD*)、写(WR*)及中断响应(INTAK*)信号的影响。

所有模板当不使用数据总线时,应将其释放,使之处于高阻状态。在响应来自临时主板的总线请求(BUSRQ*)输入时(如在DMA传输过程中),永久主板应释放数据总线。当扩充地址时,可以复用数据总线,用于地址扩展的引脚分配应如图2所示定义。2.2.3地域总线(15~30引脚)(16位,3态,高电平有效)地址由当前主板产生,在响应临时主板的总线请求(BUSRQ*)输入时,永久主板应释放地址总线,通过在数据总线上复用8位附加的地址位,地址总线可以扩展到24位。地址扩展时引脚分配应如阁2所宗。

地址总线提供16条地址线对存储器或I/O进行详码。用存储器请求(MFMRQ*)和1/O请求(I)RQ*>控制线来区分这两种操作。地址线的数日以及如何使用取决于微处理器类型,如表2所示。表2地址总线使用示例

处理器类型

8080/85

NSC 800

存储器地址线

的数目

2.2.4控制总线(31~52引脚)

刷新期的地址线

低了位

低8位

1/0地址线的数目

1/0配罩

低8位

低8位

低8位

存储器配盘

控制总线的信号线分为5部分:存储器和I/O控制、外围器件定时、时钟和复位、中断和总线控制以改串行优先权链。

2. 2. 4. 1存储器和 1/0 控制线为基本存储器及 1/0 操作提供信号。简单的应用也许只需要下面 6 个控制信号。所有的模板都应支持这6条存储器和I/0控制线。采用说明:

11 娠文炎 16。

GB/T 15275—94

31引脚WR*:写到存储器或输出设备(3态,低电平有效)。WR*由当前主板产生,表示总线上的数据将被写到寻址的存储器或输出设备。所选设备应使用该信号将数据写到存赌器或输出口。32引脚RD*:从存储器或输人设备读(3态,低电平有效)。RD*出当前主板产生,表示从存储器或输入设备读数据。所选输入设备或存储器应使用该信号把数据送上数据总线。

33引脚1ORQ*:1/0地址选择(3态,低电平有效)。IORQ*由当前主板产生,表明是一个I/O 读还是写操作。IORQ*也可以用来控制处理器的从属外围器件。bzxZ.net

34引脚MEMRQ*:存储器地址选择(3态,低电平有效)。MEMRQ*由当前主板产生,表明是存储器读还是写操作。MEMRQ*也可以用来控制处理器的从属外围器件

35引脚IOEXP:I/O扩展(3态,高电平扩展,低电平启动)。I0EXP由当前主板产生,用来扩展或启动I/0端口寻址。低电平有效信号应启用基本的(8位)1/0地址空间。/O模板对OEXP译码。36引脚MEMEX:存储器扩展(3态,高电平扩展,低电平启动)。MEMEX由当前主板产生,用来扩展或启动存储器寻址。低有效信号应启用基本的(64K)存储器地址空间。存储器模板对MEMEX译码。MEMEX也可用于存储器覆盖,如引导操作。控制模板可以关闭基本存储器而使用替换存储器。2.2.4.2外围器件定时控制线提供信号准许微处理器使用总线为它们各自的外围器件服务。8位总线是为任何8位微处理器服务的然而多数外围器件只能为特定的微处理器工作。总线上有4条控制线用于外围器件定时。这些线对应不同的微处理器有不同的定义,因此它可使每种微处理器能支持它自己的外围器件(举例见表3)。需要外围器件定时控制线提供信号的模板要具体指定与它相关的微处理器,37号脚REFRESH *:(3态,低电平有效)。REFRESH*由当前主板或单独的控制模板产生,它用于刷新动态存储器,该信号的特性和定时关系可以是存储器或处理器的函数。在不用制新功能的系统中,此信号可用作任何专用存储器的控制信号。采用静态存储器的系统可以不考虑REFRESH*信号。38引脚MCSYNC*:机器周期同步(3态,低电平有效)。MCSYNC*由当前主板产生,该信号在处理器的每个机器周期出现一次。MCSYNC确定机器周期的开始。该信号确切的特性和定时关系取决于处理器。MCSYNC*保持外围器件与处理器操作同步,它也可用于控制总线分析器,该分析器可以逐个周期地分析总线操作。MCSYNC*可用于从数据总线中分离出复用的扩展寻址。39引脚STATUS1*状态控制线1(3态,低电平有效)。STATUS1*由当前主板产生,用来为外围器件提供二饮定时。在有STATUS1*时,应用作识别取指令周期的信号。

40引脚STATUS0*:状态控制线0(3态,低电平有效)2.2.4.3中断及总线控制线允许执行总线控制方案,如,直接存储器存取、多处理器处理、单步、低速存储器、掉电重新启动以及各种中断方式。对于多个中断或总线请求的优先级,可以采用串行或并行优先级裁决方案。

处理器

NSC800

GB/T15275—94

外翻器件定时控制线示例

REFRESH*

37引脚

REFRESH*

REFRESH *

低电乎有效

商电平谈,低电平写、

MCSYNG*

38引脚

(RL+WRIINTAK)*

EOUT *($2+)

H(UT+($2 +)

41引脚BUSAK总线应答(低电中有效)。STATUS1

39引脚

STATUS0*

40引脚

BUSAK*由水久主板产生,表示总线可以由临时主板使用。水久主板应通过释放总线和认定一个总线应答信号(BUSAK*)来响应总线请求(BUSRQ*)。BUSAK*在完成当前机器周期后发出。如果有多个控制器都要占用总线,该信号要与优先级信号组合使。.42引脚BUSRQ*:总线请求(低电平有效,集电极/漏极开路)。BUSRQ*由临时主板产生并通过释放所有的三态总线使水久主板托起对总线的操作,它应在当前的机器周期完成时释放总线。BUSRQ*用在需娶对直接存储器存取(I>MA)的地方。该信号可以是输人、输出或是双向的,这取决于支持的硬件环境。43引脚[NTAK¥:中断应答(低电平有效)。INTAK*由永久主板产生,向发中断的设备表示准备响应该中断。对于关量中断,在INTAK*期问,发中断的设备应将矢量地址放到数据总线上。如果有多个控制器都需要访问永久主板,该信号可以与优先级信号组合使用。

44引脚INTRQ*:中断请求(低电乎有效,集电极/漏极开路)。INTRQ*可由任何功能从板产生,用以中断永久主板上的处理器操作。该信号敢好能被处理器屏献和忽略,除非它已经被软件启动。如果处理器接受了中断,则它以一个INTAK表示认可。其他的操作则敢决于处理器的类型、中断处理软件,以及支持该中断机制的硬件。45引脚WAITRQ*:等待请求(低电平有效,集电极/极开路)。WAITRQ*可以由任何主板或从板产生,它应使当前主板的操作挂起直到该估号变高为止。当前主板应在总线F:保持-个有效地址的状态。WAITRQ*可以用来在处理器周期内插入等待状态。例如慢速存储器、1/0)操作以及单步操作等都使用该信号。46引脚NMIRQ*:非屏敲中断(低电平有效,集电极/漏极开路)。NMIRQ*可由任何主板或从板产生,该信号对永久主板为最高优先级中断输入。它应用做处理器的紧急信号处理如用于掉电指示。2.2.4.4时钟及复位线为总线提供基本时钟定时和复位能力。47引脚SYSRESET*,系统复位(低电平有效,集电极/漏极开路)SYSRESET*由任何系统复位电路产生,如加电检测电路或按钮复位电路。所有需要初始化电路的模板都应使用SYSRESET*

GB/T 15275—94

48引脚PBRESET*,按钮复位(低电平有效,巢电极/漏极开路)。PBRESET可由任何模板产生,它作为系统复位电路的一个输入。49 引脚 CLOCK *;来自水久主板的时钟信号。Cl.OCK *由永久主板产生,它是--个经缓冲的处理器时钟信号,用于系统同形,作为通用时钟源。50 引脚 CNTRL *:控制信号。

CNTRL可由任何模板产生,用作专用时钟定时。它可以是处理器时钟信号的倍值信号、实时时钟信号或处理器的外部输入信号。2.2.4.5优先权链信号线用于串行的优先中断或总线请求。规定的优先权链分配有2条总线引脚,PCI和PCO。凡参加优先权链的每块模板都有逻辑功能,不需要优先权链的模板应在模板上短接PCI和PCO。通过模板的优先权链方向是从右边的52引脚到左边的51引脚(从用户接口蹦看去)。51引脚PCO:优先权链输出(高电平有效)。PCO可由每一块模板产生,该信号作为链路上的下一个较低优先级模板的PCI输入。需要优先级的模板,应将板上的 PCO 保持低电平。52引脚PCI:优先权链输入(高电平有效)。PCI 由当前所有请求中断的模板中优先级最高的模板的 PCO 首接产生。当 PCI 为电平时,将优先权传递给检测到该 PCI 输入的模板,对所与参予优先权链排队的模板 PCI 辅入端应有一个上拉电附,将 PCI 信号上拉到十5 V,以满足优先权的需要。3定时规范

本章规定了与处理器无关的操作的定时规范,即只有存储器和I/O的读和写,而与各种处理器类型有关的操作则包括在附录 A~D(参考件)中。3.1信号时序

对于存储器和1/O的该,写操作,规定了相应的总线信号时序。在总线中定义了这些信号的时序以保证各模板的兼容性

3.1.1地址选择信号时序

扩展信号,地址总线信号和请求信号是用来在存储器和I/0该写操作中选择数据单元的,这些信号称为地址选择信号并示于图3。扩展信号(MEMEX、IOEXP)用来选择替换存储器或I/O地址空间。地址总线信号(A0~A23)用于唯--标识存储器或I/0空间内的数据单元。请求信号(MEMRQ、IO)RQ*)用以选择是存储器操作还是I/O操作。各个地址选择信号可按任何次序出现,最后出现的信号决定信号的定时。所有地址选择信号在存储器和 I/O 读,写操作前必须稳定。(MEMEX)

地体总线

地址选择

(MEMRQ+)

图3地址选择倍时序

3.1.2读信号时序

GB/T 15275-- 94

如图1所示,读时序内当前卡板控制。而数据总线信号除外.它们是从存储器或【/)模板求的响应。地域:速择

读(RD-)

数期总线

图4读信号时序

读信号在被选定的存储器或1/O单元上产生一个读操作。读信号应在地址选择信号期间改变状态,但也可能同时改变。读信号的后沿表示数据已被传送,读信号在主板接收到数据以前始终保持数据总线有效。

数据总线信号包含了传给主板的数据字节。这些信号一直保持稳定,直到读信号去掉为止:3.1. 3写信号时序

如图5所示,写时序由当前主板控制。地址选择,数据和写信号都由当前主板产生。数据总线信号包含要传送给存储器或I/0的数据字节.数据可以出现在写值号前沿的前后。数据在写信号后沿前的一-段特定时期内应保持稳定.在写倍号后沿后的:段特定时期内数据仍应保持稳定,地趾选择

微据总线

写(WR*)

图5写信号时序

3.2信号时间宽度

信号时间宽度的定义是要使用户能够确定存储器模板或I/)模板读,写操作的兼容性。3.2.1读定时

临界读定时是当前主板与存储器模板或与I/0模板共同决定的。当前主板控制读存取时间(tARD),并对读数据建立时间(tSRD)有要求。存储器或I/O 设备有--短的读存取时间(1AR)要求,并控制读数据在总线上保持多长时间(tHRD),这些定时关系见图6。模板对读操作的兼容性取决于存储器或I/O模板规定要求的读存取时间与主板可能的读存取时间的比较结果。主板的1AR应大或等于存储器或/O 模板的tAR。主板应规定:

tAR一一最大有效读存取时间。IAR值等十1ARI)的最小值减去tSRI)的最小地址选择

数据总

存储器或I/0模板应规定:

图6临界读定

要求的最人读存取时间。由于地址选择信号与读信号有可能同时出现,tAR必筑规定其最坏情形下的读存取时间。

tHRD -

最大读数据保持时间。

GB/T 15275—94

3.2.2写定时

为保证兼容性,临界写定时受存储器或1/O)模板所需的写数据建立时间(tSWD)和写数据保持时时(tHWD)的限制,如图7所示。

模板对写操作的兼容性取决于存储器或1/0模板规定要求的写数据建立时间和保持时间与主板可能的写数据建立和保持时间的比较结果。主板的tsWD应大于或等于存储器或I/O模板的tSWD。主板的tHWD应大于或等于存储器或1/O模板的LHWD。主板应规定:

tSWD---最小可能的写数据建立时间,tHwD-

最小可能的写数据保持时间。

存储器或1/0模板应规定:

tSWD-—·要求的最小写数据建立时间;tHWD

4电气规范

要求的最小写数据保持时间。

地经选样

数据总线

率?临界写定时

本章规定了 CMOS 和TTL 总线接口的电气规范。因为二者的门限特性不一样,所以二种类型的模板不能在同:-母板上使用。

4.1CMOS电气规范

4.1.1最大额定值

表4给出的最大额定值是在模板连接器引脚处测量时不应超过的值。不推荐使用这些值,因为超过这些值,就有可能损坏模板上的器件。4.1.2CMOS电源总线电压允差

总线模板的逻辑操作需要十5V电压,当然,针对不同模板的功能及设备类型的需要,在电源总线上也可能用到表5所列的其他电压。电源信号是在模板引脚处(而不是在母板连线处)测得的,并应满足表5中所列的电乐要求。

4.1.3COMS逻辑信号特性

COMS总线设计成与工业标准的高速(OMS逻辑电平容,所有的逻辑信号都应满足表6所列的电压要求。

每块模板对每个总线信号最好只存在一个负载。总线信号驱动器最好满足表6所列的宽流要求,电容输入负载最大应为20PF。

集电极开路信号应有:个1ka的上拉电阻。上拉电阻最好放在永久主板上。参

GB/T 15275 --94

表 4 CMOS 最大电压额定值

至鞋输人或被禁止的三态输出的正压加至逻辑输入或被禁止的三态输出的负压限

CMOS电源总线电压额定值

模板引脚

CMOS参数

VOH(高电平输出电压)

VOL(低电平输出电压)

VIH(高电平人电压)

VIL(低电平摘入电压)

4.2TTL电气规范

4.2.1最大额定值

信号名称

电源电压

+3.5V至V.

表 6CMOS逻辑信号电压额定值

测试条件

V.=min,1OH=-6mA

V.=min.1OL-6mA

Va-min

Vaonin

参考点

逻辑地(3.4引脚)

逻辑地(3.4引脚)

琴考点

逻辑地(3.4引脚)

遥辑地(3.1引脚)

透辑地(3.4引脚)

辅助地(53.51脚)

辅助地(53、54引脚)

表7给出的最大额定值在模板连接器引脚处测量时不应超过的值。不推荐使用这些值,闪为超过这些值,就有可能摄坏模板上的器件。4.2.2TTL电源总线电压充差

总线模板的逻辑操作需要+5V电压。当然,针对不同模板的功能及设备类型的需要,在电源总线上也可能用到表8所列的其他电压。电源信号是在模板引脚处(而不是在母板连线线处)测得的,并应满足表 8 中给出的电压要求。

4.2.3TTL逻辑信号特性

TT1. 总线设计成与工业标准的 TTL 逻辑电平兼容。所有的逻辑信号都应满足表 9 所列的电压要求,

每块模板对每个总线信号最好只存在一个负载。总线信号驱动器最好满足表9所列的电流要求。集电极开路号应有一个4702的上拉电阻。上拉电阻最好放在永久主板上。表 7TTL最大电压额值

知至逻辑输入或被禁止的三态输出的正压加至逻辑输入或被禁止的三态输出的负压极限值

V. 1 0.5v

逻辑地(3.4引脚)

辑地(3.1引脚)

模板引脚

CMOS参数

VOH(高电平输出电压)

VOL(低电平输山电乐)

VIH(高电平输入电压)

VIL(低电平辅人电压

4.3端接技术

信号名称

ALX +V

GB/T 15275—94

表8TT1.电源总线电压额定值

电源电压

+3. 5V至 V.

表9TTL逻辑信号电压额定值

测试条件

V..- min,1OH- —3mA

Vr=min,I0L.=24mA

参考点

逻辑地(3.1引脚)

逻辑地(3.1引脚)

逻辑地(3.1引脚)

辅助地(53,54引脚)

辅助地(53.54引脚)

本标准没有定母板的端接要求。母板上分布的电气特性使得它们在进行长距离快速上升及下降时间的操作中,相当于条传输线。这此特性决定于以下诸因紫:母板的长度和布置、所用连接器的类型以及插入母板的模板数量和位置。这些特性一般通过对母板上的信号进行端接而加以控制。低速运行的处理器可以有效地在短的母板上进行操作而不用端接高速运行的处理器和长母板,需要对母板进行适当的设计和端接。

5机械规范

5.1模板尺寸

电路模板应符合图9~~10 和表 10给出的尺寸。这些尺寸不包括模板投肩及1/0接口连接器如果模板不符合表10所列的最小间距要求,则应规定其实际需要间距。5.2模板侧面轮廊尺寸

板间最小间距要求考虑如下因素;器件高度、引脚焊点高度、模板之间净剩间以及印制板的厚度。按最小间距设计的模板应满足表11 的要求。5.3总线连接器

总线连接是通过印制电路板边缘的连接器实现的。与连接器匹配连接的是模板边缘的56条引脚28对。相邻两[脚中心之间的阅距为3. 18 mm(0. 125in)。5.4模板的拔肩

每一个模板都有-一个单板拔肩,装在右上角,如图9所示。5.5模板定位

模板按一定的极性方向定位,以防止上下插反。按极性定位的模板在引脚25(26)与27(28)之间应有个偏置定位槽,如图8所示。

模板的定位槽不应开在引脚27(28)与29(30)之间,以免极性定位无效。采用说明:

1)原文有误,

模板长度

模板商度

包括镀县的印制板厚度

模板间距

元件高度

元件引线焊点高度

相邻模板间净剩间隙

1.2710.13mm

05u-0.o05in)

定安糖

CB/T 15275-94

表10模板尺寸

标称值

165.10mm(6.500in)

114.30mm(4.500n)

1.58mm(0.062in)

12. 70mm(0. 500in)

±0.64mm(±0.025in)

+0. 13mm(1 0. bo5in)

0. 64mm(- 0. 025im)

+0.18mm(+0.007in)

0. 08mm( 0. 003in)

- 0. 000mm(—0. 000in)

表11最小间距下模板的例面轮廓尺寸最

细节A

(10-390in)

(0.375in)

(0.040in)

25(26)

(28)偏数算

【3h】在背面

元件面

图8模板极性定位的定位槽位置和尺寸小

(0.01Qin)

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。

8位微型计算机STD总线

Standard for an 8-bit

micrncanputer bus sysiem,STD bus1主题内客与适用范围

GB/T 15275—94

本标准提供了将8位微处理器用于廉价模块化总线结构的规范。总线上的信号通带直接来自处理器,并经过缓冲但不新定时。这种结构导致某些模板依附于处理器。本标准提供了与器件无关的参数的核心技术规范。而附录A~D(参考件)提供了与各种处理器有关的参数。本标准对小尺寸模板与大规模集成电路技术相结合的8位微处理器总线标准给出定义,从而建立了一种功能模板的概念,对面向控制的系统设计提供了新途径。标准模板的尺寸、连接器利引出脚适宜于总线式的母板,这就使任何一块模板插入任何一个插槽都能亡作。如图1所示,微处理器通过总线接口控制模板的功能。外围设备及输入输出(I/O)设备的连接位于模板的边沿(称为用户接门端)。这种布线方式形成一个由总线接口流经模板,到用户接口的有规则的信号流,外围设备及/O设备用其自身的连接器及电缆与系统相连。完整的功能可以通过插入一块带电缆的模板以模块化方式加人到系统中去。用户接口

处理器

Z80弄

地址总议

控制总线

总规播口

存销器

国家技术监督局1994-12-D7批准2

数字1/0

输人遍口

输出湖口

工业1/0

光电隔商物入

可控硅

醒电器

各美甄动裸

图1总线的实现

阀门线圈

提抵骊动器

报170

DA转换器

AD转摄器

外解设备

控制白

CRT等

外用段备

1995-08-01实施

主题内容

本标准规定的内容:

模板尺寸;

总线连接器:

总线引脚分配:

信号定义;

电气要求,

读/写时时序:

读/写时间宽度参数。

本标准没有规定的内容:

模板功能,

用户接口;

c.H换性;

母板设计。

1.2适用范\

GB/T 15275

5—94

本标准适用于8位微处理器,16位微处理器总线的实现亦可参照本标准。1. 3 定义

认定 assert

将信号置为逻辑“1”状态。

母板 backplane

包括连接器及互连走线的印制电路板。模板 card

国印制电路板及元器件组成的模块,此模块可以插到母板上。主板 master

控制总线信号传输的模板为主板,而正在控制总线的主板为当前主板,主管其他主板的模扳刘水久主板,除永久主板外,其他主板都是临时主板。从板slave

响应总线信号传输的模板为从板。2逻辑规范

2.1总线引脚分配

总线引脚编排成如下五个功能组,如图2所示。信号流向以当前主板为参考,逻辑电源总线:

数据总线:

地址总线:

控制总线:

辅助电源总线:

采用说明:

1~6引脚

7~14引脚

15~30引脚

31~52 引脚

53~~56引脚

:] 本条内容是按照 GB 1. 1 对 IEEE Std 961 的补充。辑

控制39

信号名称

D3/A19

D2/A18

D0/A16

REFRESH *

STATLS1*

BUSAK*

INTAK *

WAITRQ*

SYSRESET*

AUX GNT)

低电平有效

2-2信号描述

元件面

信号流

GB/T15275—94

逆辑电源(-5Vde)

遥辑地

电池电源

输入/输出

输人/输出

输入/输出

输人/输出

数据总线/地址扩展

地址总线

泻存储器或1/0

/地址选择

输入/输出/0扩展

刷新定吋

EPU状态

总线应答

中断应答

等待请求

系统复位

来自处理器的时钟

优先权链输出

潮助地

辅助正电源(112Vde)

信号名称

D7/A23

1G/A22

D5/A21

D4/A2白

MEMRQ*

MCSYNC*

STATUSO*

BUSRQ*

INTRQ*

NMIRQ*

48PBRESET*

CNTRL*

AUX GND

图2总线连接器引脚分配

2.2.1电源总线(1~6引脚利53~56引脚)电路面

信号流

输入/输出

输入/输出

辑电源(-5Vdc)

趣辑地

趣辑偏医(—5Vde)

数据总线/地址扩展

输入/输出

输入/输出

地址总线

读存储器或1/0

存储器地址选择

辙入/輪出存储器扩展

KPU机器周期同步

PU状态

说线请求

中断请求

非屏蔽中断

接钮复位

辅助定时

优先权链输入

辅肥地

翻助负电源(--12Vdc)

这种双电源总线合于逻辑电源和模拟电源,最多可提供5个独立的电源及2个独立的地,表1所示。独立的地使模拟线路与数字地分开,实践中通常是在电源处将所有的地连到一点。1、2

逻辑电源

数字地

后备电压

GB/T15275—94

表1电源总线引脚分配

遥辑偏电压

辅助地

辅助正电源

辅助负电源

遥辑电源(+5V de)

逐辑电源地线

电池电压(+3.5~+5.0v dc)

低电流逆辑电源(-5V de)

辅助电源地线

正直流电激(+12Vde)

负直流电源(—12V de)

1、2引脚上的逻辑电源和3、4引脚上的数字地是所有模板要求的,其他电源引脚是可选的。2.2.2数据总线(7~14引脚)(8位,双向,3态,高电平有效)数据总线的流向由当前主板来控制并受读(RD*)、写(WR*)及中断响应(INTAK*)信号的影响。

所有模板当不使用数据总线时,应将其释放,使之处于高阻状态。在响应来自临时主板的总线请求(BUSRQ*)输入时(如在DMA传输过程中),永久主板应释放数据总线。当扩充地址时,可以复用数据总线,用于地址扩展的引脚分配应如图2所示定义。2.2.3地域总线(15~30引脚)(16位,3态,高电平有效)地址由当前主板产生,在响应临时主板的总线请求(BUSRQ*)输入时,永久主板应释放地址总线,通过在数据总线上复用8位附加的地址位,地址总线可以扩展到24位。地址扩展时引脚分配应如阁2所宗。

地址总线提供16条地址线对存储器或I/O进行详码。用存储器请求(MFMRQ*)和1/O请求(I)RQ*>控制线来区分这两种操作。地址线的数日以及如何使用取决于微处理器类型,如表2所示。表2地址总线使用示例

处理器类型

8080/85

NSC 800

存储器地址线

的数目

2.2.4控制总线(31~52引脚)

刷新期的地址线

低了位

低8位

1/0地址线的数目

1/0配罩

低8位

低8位

低8位

存储器配盘

控制总线的信号线分为5部分:存储器和I/O控制、外围器件定时、时钟和复位、中断和总线控制以改串行优先权链。

2. 2. 4. 1存储器和 1/0 控制线为基本存储器及 1/0 操作提供信号。简单的应用也许只需要下面 6 个控制信号。所有的模板都应支持这6条存储器和I/0控制线。采用说明:

11 娠文炎 16。

GB/T 15275—94

31引脚WR*:写到存储器或输出设备(3态,低电平有效)。WR*由当前主板产生,表示总线上的数据将被写到寻址的存储器或输出设备。所选设备应使用该信号将数据写到存赌器或输出口。32引脚RD*:从存储器或输人设备读(3态,低电平有效)。RD*出当前主板产生,表示从存储器或输入设备读数据。所选输入设备或存储器应使用该信号把数据送上数据总线。

33引脚1ORQ*:1/0地址选择(3态,低电平有效)。IORQ*由当前主板产生,表明是一个I/O 读还是写操作。IORQ*也可以用来控制处理器的从属外围器件。bzxZ.net

34引脚MEMRQ*:存储器地址选择(3态,低电平有效)。MEMRQ*由当前主板产生,表明是存储器读还是写操作。MEMRQ*也可以用来控制处理器的从属外围器件

35引脚IOEXP:I/O扩展(3态,高电平扩展,低电平启动)。I0EXP由当前主板产生,用来扩展或启动I/0端口寻址。低电平有效信号应启用基本的(8位)1/0地址空间。/O模板对OEXP译码。36引脚MEMEX:存储器扩展(3态,高电平扩展,低电平启动)。MEMEX由当前主板产生,用来扩展或启动存储器寻址。低有效信号应启用基本的(64K)存储器地址空间。存储器模板对MEMEX译码。MEMEX也可用于存储器覆盖,如引导操作。控制模板可以关闭基本存储器而使用替换存储器。2.2.4.2外围器件定时控制线提供信号准许微处理器使用总线为它们各自的外围器件服务。8位总线是为任何8位微处理器服务的然而多数外围器件只能为特定的微处理器工作。总线上有4条控制线用于外围器件定时。这些线对应不同的微处理器有不同的定义,因此它可使每种微处理器能支持它自己的外围器件(举例见表3)。需要外围器件定时控制线提供信号的模板要具体指定与它相关的微处理器,37号脚REFRESH *:(3态,低电平有效)。REFRESH*由当前主板或单独的控制模板产生,它用于刷新动态存储器,该信号的特性和定时关系可以是存储器或处理器的函数。在不用制新功能的系统中,此信号可用作任何专用存储器的控制信号。采用静态存储器的系统可以不考虑REFRESH*信号。38引脚MCSYNC*:机器周期同步(3态,低电平有效)。MCSYNC*由当前主板产生,该信号在处理器的每个机器周期出现一次。MCSYNC确定机器周期的开始。该信号确切的特性和定时关系取决于处理器。MCSYNC*保持外围器件与处理器操作同步,它也可用于控制总线分析器,该分析器可以逐个周期地分析总线操作。MCSYNC*可用于从数据总线中分离出复用的扩展寻址。39引脚STATUS1*状态控制线1(3态,低电平有效)。STATUS1*由当前主板产生,用来为外围器件提供二饮定时。在有STATUS1*时,应用作识别取指令周期的信号。

40引脚STATUS0*:状态控制线0(3态,低电平有效)2.2.4.3中断及总线控制线允许执行总线控制方案,如,直接存储器存取、多处理器处理、单步、低速存储器、掉电重新启动以及各种中断方式。对于多个中断或总线请求的优先级,可以采用串行或并行优先级裁决方案。

处理器

NSC800

GB/T15275—94

外翻器件定时控制线示例

REFRESH*

37引脚

REFRESH*

REFRESH *

低电乎有效

商电平谈,低电平写、

MCSYNG*

38引脚

(RL+WRIINTAK)*

EOUT *($2+)

H(UT+($2 +)

41引脚BUSAK总线应答(低电中有效)。STATUS1

39引脚

STATUS0*

40引脚

BUSAK*由水久主板产生,表示总线可以由临时主板使用。水久主板应通过释放总线和认定一个总线应答信号(BUSAK*)来响应总线请求(BUSRQ*)。BUSAK*在完成当前机器周期后发出。如果有多个控制器都要占用总线,该信号要与优先级信号组合使。.42引脚BUSRQ*:总线请求(低电平有效,集电极/漏极开路)。BUSRQ*由临时主板产生并通过释放所有的三态总线使水久主板托起对总线的操作,它应在当前的机器周期完成时释放总线。BUSRQ*用在需娶对直接存储器存取(I>MA)的地方。该信号可以是输人、输出或是双向的,这取决于支持的硬件环境。43引脚[NTAK¥:中断应答(低电平有效)。INTAK*由永久主板产生,向发中断的设备表示准备响应该中断。对于关量中断,在INTAK*期问,发中断的设备应将矢量地址放到数据总线上。如果有多个控制器都需要访问永久主板,该信号可以与优先级信号组合使用。

44引脚INTRQ*:中断请求(低电乎有效,集电极/漏极开路)。INTRQ*可由任何功能从板产生,用以中断永久主板上的处理器操作。该信号敢好能被处理器屏献和忽略,除非它已经被软件启动。如果处理器接受了中断,则它以一个INTAK表示认可。其他的操作则敢决于处理器的类型、中断处理软件,以及支持该中断机制的硬件。45引脚WAITRQ*:等待请求(低电平有效,集电极/极开路)。WAITRQ*可以由任何主板或从板产生,它应使当前主板的操作挂起直到该估号变高为止。当前主板应在总线F:保持-个有效地址的状态。WAITRQ*可以用来在处理器周期内插入等待状态。例如慢速存储器、1/0)操作以及单步操作等都使用该信号。46引脚NMIRQ*:非屏敲中断(低电平有效,集电极/漏极开路)。NMIRQ*可由任何主板或从板产生,该信号对永久主板为最高优先级中断输入。它应用做处理器的紧急信号处理如用于掉电指示。2.2.4.4时钟及复位线为总线提供基本时钟定时和复位能力。47引脚SYSRESET*,系统复位(低电平有效,集电极/漏极开路)SYSRESET*由任何系统复位电路产生,如加电检测电路或按钮复位电路。所有需要初始化电路的模板都应使用SYSRESET*

GB/T 15275—94

48引脚PBRESET*,按钮复位(低电平有效,巢电极/漏极开路)。PBRESET可由任何模板产生,它作为系统复位电路的一个输入。49 引脚 CLOCK *;来自水久主板的时钟信号。Cl.OCK *由永久主板产生,它是--个经缓冲的处理器时钟信号,用于系统同形,作为通用时钟源。50 引脚 CNTRL *:控制信号。

CNTRL可由任何模板产生,用作专用时钟定时。它可以是处理器时钟信号的倍值信号、实时时钟信号或处理器的外部输入信号。2.2.4.5优先权链信号线用于串行的优先中断或总线请求。规定的优先权链分配有2条总线引脚,PCI和PCO。凡参加优先权链的每块模板都有逻辑功能,不需要优先权链的模板应在模板上短接PCI和PCO。通过模板的优先权链方向是从右边的52引脚到左边的51引脚(从用户接口蹦看去)。51引脚PCO:优先权链输出(高电平有效)。PCO可由每一块模板产生,该信号作为链路上的下一个较低优先级模板的PCI输入。需要优先级的模板,应将板上的 PCO 保持低电平。52引脚PCI:优先权链输入(高电平有效)。PCI 由当前所有请求中断的模板中优先级最高的模板的 PCO 首接产生。当 PCI 为电平时,将优先权传递给检测到该 PCI 输入的模板,对所与参予优先权链排队的模板 PCI 辅入端应有一个上拉电附,将 PCI 信号上拉到十5 V,以满足优先权的需要。3定时规范

本章规定了与处理器无关的操作的定时规范,即只有存储器和I/O的读和写,而与各种处理器类型有关的操作则包括在附录 A~D(参考件)中。3.1信号时序

对于存储器和1/O的该,写操作,规定了相应的总线信号时序。在总线中定义了这些信号的时序以保证各模板的兼容性

3.1.1地址选择信号时序

扩展信号,地址总线信号和请求信号是用来在存储器和I/0该写操作中选择数据单元的,这些信号称为地址选择信号并示于图3。扩展信号(MEMEX、IOEXP)用来选择替换存储器或I/O地址空间。地址总线信号(A0~A23)用于唯--标识存储器或I/0空间内的数据单元。请求信号(MEMRQ、IO)RQ*)用以选择是存储器操作还是I/O操作。各个地址选择信号可按任何次序出现,最后出现的信号决定信号的定时。所有地址选择信号在存储器和 I/O 读,写操作前必须稳定。(MEMEX)

地体总线

地址选择

(MEMRQ+)

图3地址选择倍时序

3.1.2读信号时序

GB/T 15275-- 94

如图1所示,读时序内当前卡板控制。而数据总线信号除外.它们是从存储器或【/)模板求的响应。地域:速择

读(RD-)

数期总线

图4读信号时序

读信号在被选定的存储器或1/O单元上产生一个读操作。读信号应在地址选择信号期间改变状态,但也可能同时改变。读信号的后沿表示数据已被传送,读信号在主板接收到数据以前始终保持数据总线有效。

数据总线信号包含了传给主板的数据字节。这些信号一直保持稳定,直到读信号去掉为止:3.1. 3写信号时序

如图5所示,写时序由当前主板控制。地址选择,数据和写信号都由当前主板产生。数据总线信号包含要传送给存储器或I/0的数据字节.数据可以出现在写值号前沿的前后。数据在写信号后沿前的一-段特定时期内应保持稳定.在写倍号后沿后的:段特定时期内数据仍应保持稳定,地趾选择

微据总线

写(WR*)

图5写信号时序

3.2信号时间宽度

信号时间宽度的定义是要使用户能够确定存储器模板或I/)模板读,写操作的兼容性。3.2.1读定时

临界读定时是当前主板与存储器模板或与I/0模板共同决定的。当前主板控制读存取时间(tARD),并对读数据建立时间(tSRD)有要求。存储器或I/O 设备有--短的读存取时间(1AR)要求,并控制读数据在总线上保持多长时间(tHRD),这些定时关系见图6。模板对读操作的兼容性取决于存储器或I/O模板规定要求的读存取时间与主板可能的读存取时间的比较结果。主板的1AR应大或等于存储器或/O 模板的tAR。主板应规定:

tAR一一最大有效读存取时间。IAR值等十1ARI)的最小值减去tSRI)的最小地址选择

数据总

存储器或I/0模板应规定:

图6临界读定

要求的最人读存取时间。由于地址选择信号与读信号有可能同时出现,tAR必筑规定其最坏情形下的读存取时间。

tHRD -

最大读数据保持时间。

GB/T 15275—94

3.2.2写定时

为保证兼容性,临界写定时受存储器或1/O)模板所需的写数据建立时间(tSWD)和写数据保持时时(tHWD)的限制,如图7所示。

模板对写操作的兼容性取决于存储器或1/0模板规定要求的写数据建立时间和保持时间与主板可能的写数据建立和保持时间的比较结果。主板的tsWD应大于或等于存储器或I/O模板的tSWD。主板的tHWD应大于或等于存储器或1/O模板的LHWD。主板应规定:

tSWD---最小可能的写数据建立时间,tHwD-

最小可能的写数据保持时间。

存储器或1/0模板应规定:

tSWD-—·要求的最小写数据建立时间;tHWD

4电气规范

要求的最小写数据保持时间。

地经选样

数据总线

率?临界写定时

本章规定了 CMOS 和TTL 总线接口的电气规范。因为二者的门限特性不一样,所以二种类型的模板不能在同:-母板上使用。

4.1CMOS电气规范

4.1.1最大额定值

表4给出的最大额定值是在模板连接器引脚处测量时不应超过的值。不推荐使用这些值,因为超过这些值,就有可能损坏模板上的器件。4.1.2CMOS电源总线电压允差

总线模板的逻辑操作需要十5V电压,当然,针对不同模板的功能及设备类型的需要,在电源总线上也可能用到表5所列的其他电压。电源信号是在模板引脚处(而不是在母板连线处)测得的,并应满足表5中所列的电乐要求。

4.1.3COMS逻辑信号特性

COMS总线设计成与工业标准的高速(OMS逻辑电平容,所有的逻辑信号都应满足表6所列的电压要求。

每块模板对每个总线信号最好只存在一个负载。总线信号驱动器最好满足表6所列的宽流要求,电容输入负载最大应为20PF。

集电极开路信号应有:个1ka的上拉电阻。上拉电阻最好放在永久主板上。参

GB/T 15275 --94

表 4 CMOS 最大电压额定值

至鞋输人或被禁止的三态输出的正压加至逻辑输入或被禁止的三态输出的负压限

CMOS电源总线电压额定值

模板引脚

CMOS参数

VOH(高电平输出电压)

VOL(低电平输出电压)

VIH(高电平人电压)

VIL(低电平摘入电压)

4.2TTL电气规范

4.2.1最大额定值

信号名称

电源电压

+3.5V至V.

表 6CMOS逻辑信号电压额定值

测试条件

V.=min,1OH=-6mA

V.=min.1OL-6mA

Va-min

Vaonin

参考点

逻辑地(3.4引脚)

逻辑地(3.4引脚)

琴考点

逻辑地(3.4引脚)

遥辑地(3.1引脚)

透辑地(3.4引脚)

辅助地(53.51脚)

辅助地(53、54引脚)

表7给出的最大额定值在模板连接器引脚处测量时不应超过的值。不推荐使用这些值,闪为超过这些值,就有可能摄坏模板上的器件。4.2.2TTL电源总线电压充差

总线模板的逻辑操作需要+5V电压。当然,针对不同模板的功能及设备类型的需要,在电源总线上也可能用到表8所列的其他电压。电源信号是在模板引脚处(而不是在母板连线线处)测得的,并应满足表 8 中给出的电压要求。

4.2.3TTL逻辑信号特性

TT1. 总线设计成与工业标准的 TTL 逻辑电平兼容。所有的逻辑信号都应满足表 9 所列的电压要求,

每块模板对每个总线信号最好只存在一个负载。总线信号驱动器最好满足表9所列的电流要求。集电极开路号应有一个4702的上拉电阻。上拉电阻最好放在永久主板上。表 7TTL最大电压额值

知至逻辑输入或被禁止的三态输出的正压加至逻辑输入或被禁止的三态输出的负压极限值

V. 1 0.5v

逻辑地(3.4引脚)

辑地(3.1引脚)

模板引脚

CMOS参数

VOH(高电平输出电压)

VOL(低电平输山电乐)

VIH(高电平输入电压)

VIL(低电平辅人电压

4.3端接技术

信号名称

ALX +V

GB/T 15275—94

表8TT1.电源总线电压额定值

电源电压

+3. 5V至 V.

表9TTL逻辑信号电压额定值

测试条件

V..- min,1OH- —3mA

Vr=min,I0L.=24mA

参考点

逻辑地(3.1引脚)

逻辑地(3.1引脚)

逻辑地(3.1引脚)

辅助地(53,54引脚)

辅助地(53.54引脚)

本标准没有定母板的端接要求。母板上分布的电气特性使得它们在进行长距离快速上升及下降时间的操作中,相当于条传输线。这此特性决定于以下诸因紫:母板的长度和布置、所用连接器的类型以及插入母板的模板数量和位置。这些特性一般通过对母板上的信号进行端接而加以控制。低速运行的处理器可以有效地在短的母板上进行操作而不用端接高速运行的处理器和长母板,需要对母板进行适当的设计和端接。

5机械规范

5.1模板尺寸

电路模板应符合图9~~10 和表 10给出的尺寸。这些尺寸不包括模板投肩及1/0接口连接器如果模板不符合表10所列的最小间距要求,则应规定其实际需要间距。5.2模板侧面轮廊尺寸

板间最小间距要求考虑如下因素;器件高度、引脚焊点高度、模板之间净剩间以及印制板的厚度。按最小间距设计的模板应满足表11 的要求。5.3总线连接器

总线连接是通过印制电路板边缘的连接器实现的。与连接器匹配连接的是模板边缘的56条引脚28对。相邻两[脚中心之间的阅距为3. 18 mm(0. 125in)。5.4模板的拔肩

每一个模板都有-一个单板拔肩,装在右上角,如图9所示。5.5模板定位

模板按一定的极性方向定位,以防止上下插反。按极性定位的模板在引脚25(26)与27(28)之间应有个偏置定位槽,如图8所示。

模板的定位槽不应开在引脚27(28)与29(30)之间,以免极性定位无效。采用说明:

1)原文有误,

模板长度

模板商度

包括镀县的印制板厚度

模板间距

元件高度

元件引线焊点高度

相邻模板间净剩间隙

1.2710.13mm

05u-0.o05in)

定安糖

CB/T 15275-94

表10模板尺寸

标称值

165.10mm(6.500in)

114.30mm(4.500n)

1.58mm(0.062in)

12. 70mm(0. 500in)

±0.64mm(±0.025in)

+0. 13mm(1 0. bo5in)

0. 64mm(- 0. 025im)

+0.18mm(+0.007in)

0. 08mm( 0. 003in)

- 0. 000mm(—0. 000in)

表11最小间距下模板的例面轮廓尺寸最

细节A

(10-390in)

(0.375in)

(0.040in)

25(26)

(28)偏数算

【3h】在背面

元件面

图8模板极性定位的定位槽位置和尺寸小

(0.01Qin)

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。