GB/T 4728.12-1996

基本信息

标准号: GB/T 4728.12-1996

中文名称:电气简图用图形符号 第12部分:二进制逻辑元件

标准类别:国家标准(GB)

英文名称: Graphical symbols for electrical schematics Part 12: Binary logic elements

标准状态:已作废

发布日期:1996-01-02

实施日期:1997-07-01

作废日期:2009-01-01

出版语种:简体中文

下载格式:.rar.pdf

下载大小:4685484

标准分类号

标准ICS号:ICS 综合、术语学、标准化、文献>>图形符号>>01.080.20专用设备用图形符号

中标分类号:电工>>电工综合>>K04基础标准与通用方法

出版信息

出版社:中国标准出版社

书号:155066.1-13929

页数:111页

标准价格:44.0 元

出版日期:2004-04-02

相关单位信息

首发日期:1985-11-01

复审日期:2004-10-14

起草人:常振启、李善贞、李占先、胡仁洋、孙人杰等

起草单位:华北计算技术研究所、电子工部标准化研究所等

提出单位:中华人民共和国电子工业部

发布部门:国家质量技术监督局

主管部门:国家标准化管理委员会

标准简介

本标准规定了用来表示逻辑功能的图形符号。 GB/T 4728.12-1996 电气简图用图形符号 第12部分:二进制逻辑元件 GB/T4728.12-1996 标准下载解压密码:www.bzxz.net

标准图片预览

标准内容

GB/T4728.12—1996

本标准是根据国际电工委员会IEC617-12:1991《电气简图用图形符号第12部分:二进制逻辑元件》对GB4728.12—85进行修订的,其技术内容和编辑格式均与IEC617-12:1991等同。本标准中出现的EC117-15《推荐性图形符号第15部分:二进制逻辑元件》是IEC617-12的前身。

本标准与GB4728.12—85比较,主要差异如下:GB4728.12—85共5章122条,包含54个图例,33个概念图解;本标准共六篇132条,包含127个图例,48个概念图解。主要增加了第六篇“复杂功能单元”及其相应的图例和概念图解。

通过本标准的修订,更好地统一了二进制逻辑元件图形符号的绘制规则,以适应国际和国内贸易、技术和经济交流的需要。

GB4728《电气图用图形符号》国家标准包括以下13个部分:5总则

GB 4728.1—85

GB4728.2—84

GB 4728.3—84

符号要素、限定符号和常用的其他符号导线和连接器件

GB4728.4—85

无源元件

GB4728.5—85

GB 4728.6—84

GB 4728.7—84

GB4728.8—84

GB 4728.9—85

半导体管和电子管

电能的发生和转换

开关、控制和保护装置

测量仪表、灯和信号器件

电信:交换和外围设备

GB4728.10—85电信:传输

GB4728.11-85电力、照明和电信布置GB/T4728.12—1996二进制逻辑元件GB/T4728.13—1996模拟元件

本标准从1997年7月1日起实施,同时代替GB4728.12—85。本标准的附录A和附录B是提示的附录。本标准由中华人民共和国电子工业部提出。本标准由全国电气图形符号标准化技术委员会归口。本标准起草单位:华北计算技术研究所、电子工业部标准化研究所、航天工业总公司二院、北京广播器材厂、北京东光电工厂。

本标准主要起草人:常振启、李善贞、李占先、胡仁洋、孙人杰、张春婷。I

GB/T4728.12—1996

IEC前言

1)正C关于技术问题的正式决定或协议,尽可能地表达了所讨论问题在国际上的一致意见。起草文件的技术委员会代表了关心这些技术问题的所有国家委员会。2)这些决定和协议以推荐标准的形式供国际上使用,并在这种意义上为各国家委员会所接受。3)为了促进国际统一,IEC希望各国家委员会,只要国家条件允许,应尽量采用IEC的推荐标准作为它们的国家标准。IEC推荐标准和相应国家标准之间的任何分歧,应尽可能地在相应国家标准中说明。

GB/T4728.12—1996

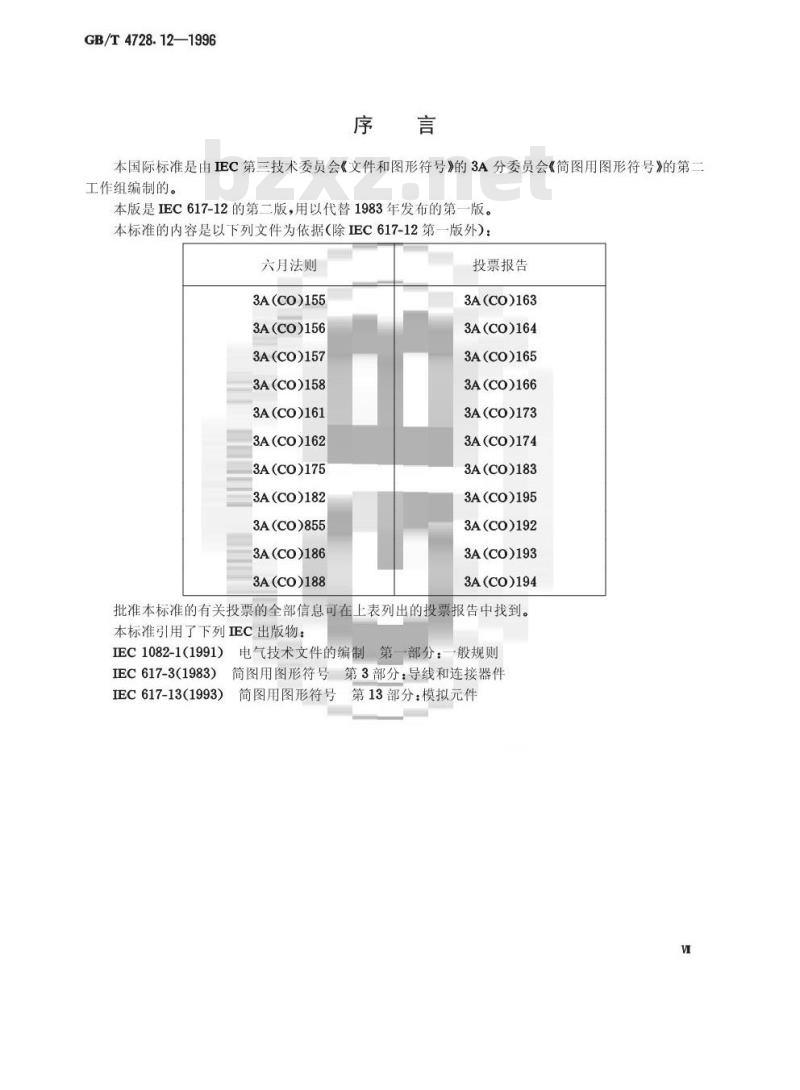

本国际标准是由IEC第三技术委员会《文件和图形符号》的3A分委员会《简图用图形符号》的第二工作组编制的。

本版是IEC617-12的第二版,用以代替1983年发布的第一版。本标准的内容是以下列文件为依据(除IEC617-12第一版外):六月法则

3A(CO)155

3A(CO)156

3A(CO)157

3A(CO)158

3A(CO)161

3A(CO)162

3A(CO)175

3A(CO)182

3A(CO)855

3A(CO)186

3A(CO)188

投票报告

3A(CO)163

3A(CO)164

3A(CO)165

3A(CO)166

3A(CO)173

3A(CO)174

3A(CO)183

3A(CO)195

3A(CO)192

3A(CO)193

3A(CO)194

批准本标准的有关投票的全部信息可在上表列出的投票报告中找到。本标准引用了下列EC出版物:

EC1082-1(1991)电气技术文件的编制第一部分:一般规则简图用图形符号第3部分:导线和连接器件IEC617-3(1983)

IEC617-13(1993)

简图用图形符号第13部分:模拟元件V

1引言

中华人民共和国国家标准

电气简图用图形符号

第12部分:二进制逻辑元件

Graphical symbolsforelectrical diagramsPart 12:Binary logic elements第一篇 总

GB/T4728.12—1996

idtIEC617-12:1991

代替GB4728.12—85

本标准规定了用来表示逻辑功能的图形符号。这些图形符号也可用来表示能执行这些逻辑功能的物理器件。符号的设计着眼于电的应用,但其大多数也可用于非电气领域,例如气动的、液压的和机械的。

2一般说明

2.1对于符号IEC117-15《推荐的图形符号第15部分:二进制逻辑元件》的符号,要求延长过渡期,但应逐步地用本标准规定的符号代替。使用一些国家标准公认的其他符号,例如形状特别的那些符号来代替12-27-01、12-27-02、12-27-09、12-27-10、12-27-11,12-27-12、12-28-01、12-28-02和12-28-04,虽然不推荐,也不应视为与本标准相抵触。但是不允许用来组合复杂符号(例如用作镶嵌符号)。2.2有关“逻辑状态”“逻辑电平”的解释,见IEC1082-2《电气技术用文件的编制功能性简图》。2.3本标准采用符号\0”和“1”来表示二进制变量的两种逻辑状态。这两种状态称之为\0”状态和“1”状态。

2.4一个二进制变量可以用任何一种有两个不同值域的物理量来表示。在本标准中,这两个值域的物理量为逻辑电平,并分别以H和L表示。H用来表示具有正得较多的代数值的逻辑电平,L用来表示具有正得较少的代数值的逻辑电平。2.5如果一个系统的逻辑状态用物理量的其他特性(例如:正脉冲和负脉冲、有脉冲和无脉冲)来表示,仍可以用H和L来表示这些特性,或者用更适当的符号代替。3术语解释

3.1内部逻辑状态internallogicstates指的是在符号框内输入端或输出端设想存在的逻辑状态。3.2外部逻辑状态externallogicstates指的是在符号框外设想存在的逻辑状态:一对输入端,是指输入线上任何外部限定符号之前的逻辑状态;一对输出端,是指输出线上任何外部限定符号之后的逻辑状态。采用说明:

1JIEC1082-2代替IEC113-7。

国家技术监督局1996-12-17批准1997-07-01实施

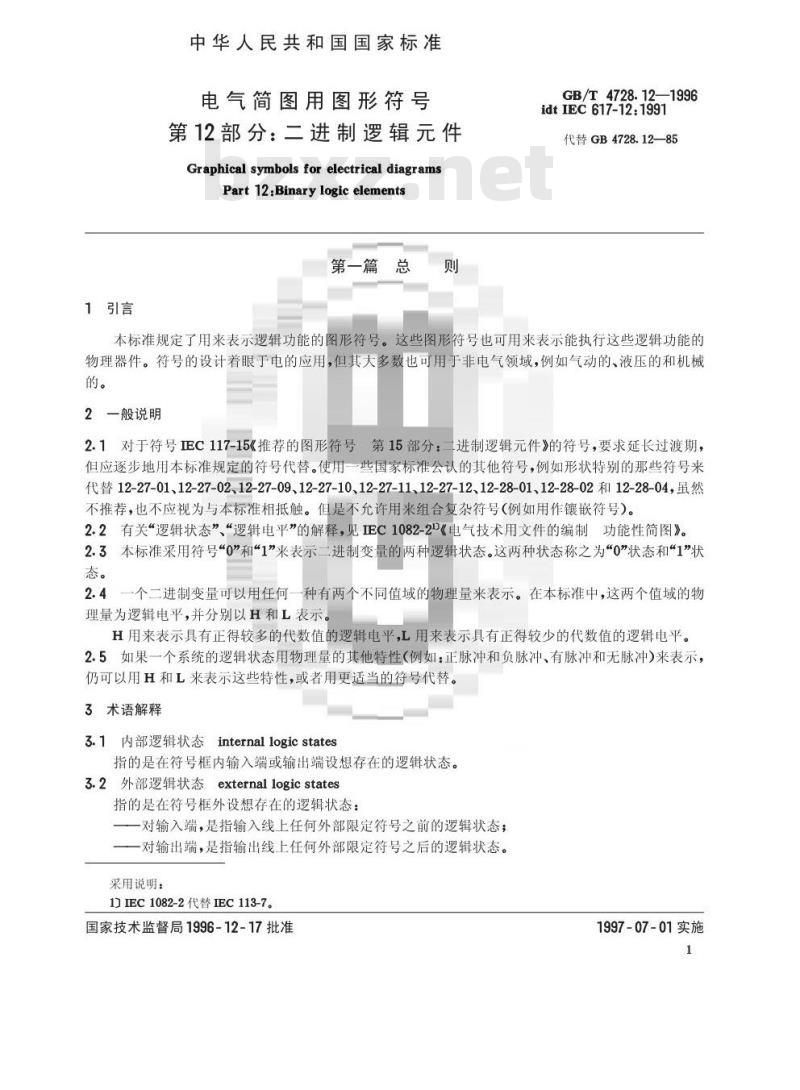

3.3逻辑电平logiclevel

GB/T4728.12—1996

指的是设想用来代表二进制变量的物理量(见2.3和2.4)。概念图解

内部退悍优芯

外部逐期达态

外卵遥辑状路

第二篇

4符号的组成

符号结构

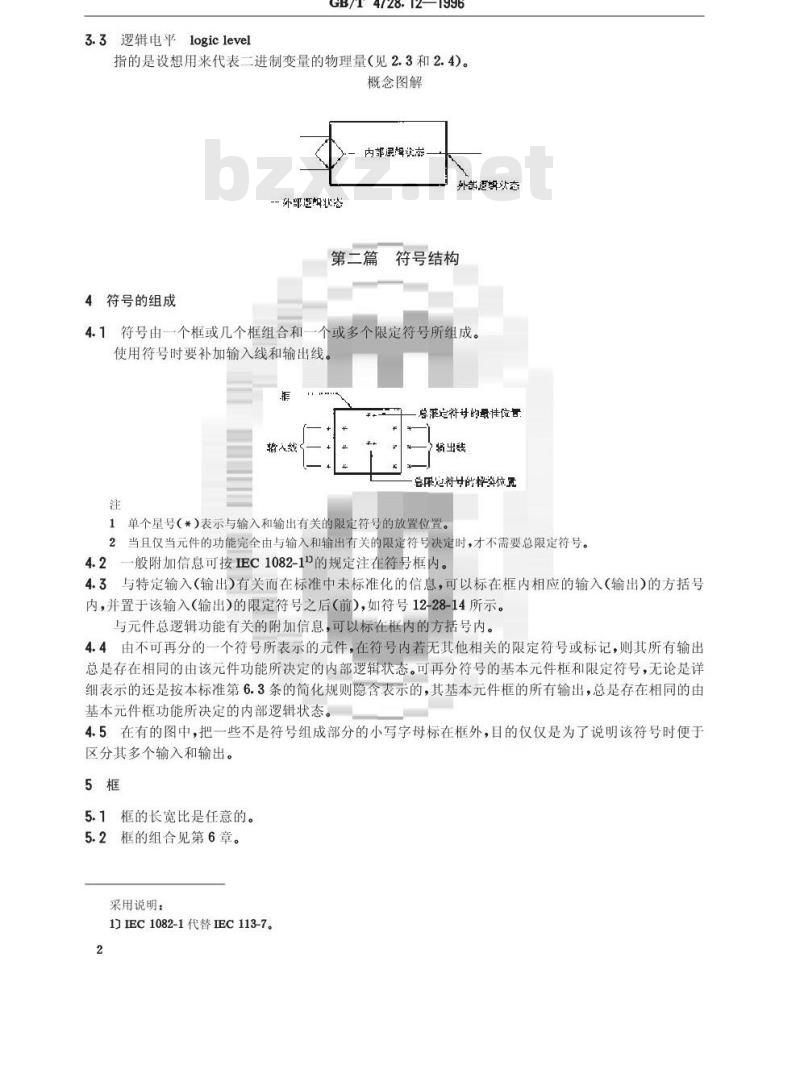

4.1符号由一个框或几个框组合和一个或多个限定符号所组成。使用符号时要补加输入线和输出线,制

总样讨的最佳位者

指人线

摘出裁

总限过待母的样类位置

1单个星号(*)表示与输入和输出有关的限定符号的放置位置。2当且仅当元件的功能完全由与输入和输出有关的限定符号决定时,才不需要总限定符号。4.2一般附加信息可按IEC1082-11的规定注在符号框内。4.3与特定输入(输出)有关而在标准中未标准化的信息,可以标在框内相应的输入(输出)的方括号内,并置于该输入(输出)的限定符号之后(前),如符号12-28-14所示。与元件总逻辑功能有关的附加信息,可以标在框内的方括号内。4.4由不可再分的一个符号所表示的元件,在符号内若无其他相关的限定符号或标记,则其所有输出总是存在相同的由该元件功能所决定的内部逻辑状态。可再分符号的基本元件框和限定符号,无论是详细表示的还是按本标准第6.3条的简化规则隐含表示的,其基本元件框的所有输出,总是存在相同的由基本元件框功能所决定的内部逻辑状态。4.5在有的图中,把一些不是符号组成部分的小写字母标在框外,目的仅仅是为了说明该符号时便于区分其多个输入和输出。

5.1框的长宽比是任意的。

5.2框的组合见第6章。

采用说明:

1JIEC1082-1代替IEC113-7。

12-05-01

12-05-02

12-05-03

6框的应用和组合

GB/T4728.12—1996

图形符号

元件框(示出正方形)

公共控制框

公共输出元件框

6.1为了缩小表示一组相邻元件所需的幅面,各元件的框可遵循下述规则邻接或镶嵌。6.1.1当各元件框公共线沿着信息流方向时,这些元件框之间无逻辑连接。概念图解

注:此规则不一定适用于有两种或两种以上信息流方向的那些阵列,例如,由公共控制框、公共输出元件框或由关联标记指明多种信息流方向的阵列。6.1.2如果两框的公共线垂直于信息流方向,则它们之间至少有一种逻辑连接。由于公共控制框不是逻辑元件框,因此,到公共控制框去的或从公共控制框来的连接线,都不存在逻辑连接,但与阵列相连并详细示出连接关系的除外。每一种逻辑连接可以由标注在公共线一侧或两侧的限定符号表示。如果这种方法会引起逻辑连接数目混乱时,则可使用内部连接符号(符号12-08-01)。如果在公共线的两侧均无限定符号,则可认为元件框间仅存在一种逻辑连接。概念图解

每一个星号表示一个限定符号的位置。6.2公共控制框可以与相关元件阵列连接。与阵列的一个以上元件有关的输入或输出,或者与阵列元件无关的输入或输出均可画在公共控制框上。这类输入和输出应加注(如果有)适当的标记。6.2.1如果示于公共控制框的输入是关联标记中的影响输入(见第11和12章),则它仅仅是阵列中标有该输入标识序号的各个元件所共有的输入。如果示于公共控制框的输入不是关联标记中的影响输入,3

GB/T4728.12—1996

则它是阵列所有元件共有的或对所有元件起作用的输入。公共控制框画在相关元件阵列的一端,除非另有说明,与公共控制框相邻接的元件是阵列中最低位的元件。

概念图解

6.2.2与阵列中全部元件有关的公共输出,可以示作公共输出元件的输出。在阵列元件有一个以上输出的情况下,只有当这些输出始终具有相同的内部逻辑状态时,才可以采用公共输出元件。采用公共输出元件意味着从阵列的每一个元件到公共输出元件有内部连接,但不必示出。此外,公共输出元件可以有其他的输入,这些输入必须详细示出。公共输出元件的功能应该标明。与阵列输出对应的公共输出元件的每一个输入具有与该输出相同的内部逻辑状态。公共输出元件框示于:

公共控制框内,或

一阵列的末端,如有公共控制框时,则在其相对的位置。对于一个阵列适于有多个公共输出元件框的场合,只需在一处画双线。概念图解

公共输出元

件框在公共

控制握内的

有两个公共

输山元件拒

的阵列

GB/T4728.12—1996

6.3对于由若干个具有相同限定符号的元件框构成的阵列,只要不会引起混乱,绘图时只在第一个框内标出限定符号即可。同样,当构成阵列的每个元件框又由几个相同的子阵列组成时,只详细画出第个子阵列,其余的用简单的框表示即可。即使在阵列的每个元件框中,关联标记的影响输入(输出)与受影响输入(输出)的标识序号不同,也可以进行简化(概念图解见第14章)。概念图解

其有相同总限定等导的元件阵

两个郭接的元件阵列wwW.bzxz.Net

两个交铝组合的元件阵列

无公共控制框的具有相同的与

输人和翰出有关的限定符号的

元件降阵

有公共控制握的具有相同的与

输人利输出有关的限定符号的

元件阵列

6.4在简化表示的由若于相同元件框组成的阵列中,若一个引出端的功能需要用两条或两条以上的引出线在框外连接在一起表示时,则需要在第个元件框详细示出,其余元件框可以简化,用单线表示。属于连接在一起的所有引出线共有的框外符号,应示于单线上,而非共有的符号可省略或示出。5

第三篇

GB/T4728.12—1996

概念图解

与输入、输出和其他连接有关的限定符号7逻辑非、逻辑极性和动态输入

本章中的每一个符号用来确定内部逻辑状态和外部逻辑状态或逻辑电平之间的关系。若在输入或输出端无本章的符号,则认为:在采用逻辑非符号的图上,内部逻辑“1”状态与外部逻辑“1”状态相对应;在采用逻辑极性符号的图上,内部逻辑“1”状态与逻辑\H”电平相对应。在采用逻辑极性符号的图上,不存在外部逻辑状态。逻辑非和逻辑极性符号不应在同一图上一起使用,但在采用逻辑极性符号的图上可能出现逻辑非作为内部连接的情况除外,见符号12-08-02和12-08-04。6

12-07-01

12-07-02

12-07-03

12-07-04

12-07-05

12-07-06

12-07-07

12-07-08

12-07-09

8内部连接

GB/T4728.12—1996

逻辑非,示于输入端

逻辑非,示于输出端

内部“1”状态与外部“0”状态对应注:连接线可延伸穿过小圆。

逻辑极性指示符,示于输入端

逻辑极性指示符,示于输出端

逻辑极性指示符,示于从右至左的信息流输入端

逻辑极性指示符,示于从右至左的信息流的输出端

内部“1”状态与连接线上的“L”电平相对应动态输入

内部“1”状态(暂态)与从外部“0”状态转换到外部“1”状态的过程相对应。其他所有时间逻辑状态为“0\

在采用逻辑极性符号的图上,内部“1”状态(暂态)与连线上从“L”电平到“H”电平的转换过程相对应。其他所有时间内部逻辑状态为“0\

有逻辑非的动态输入

内部逻辑“1”状态(暂态)与从外部“1”状态到外部\0”状态的转换过程相对应。其他所有时间内部逻辑状态为“0\

有极性指示符的动态输入

内部“1”状态(暂态)与连线上从“H”电平到“L”电平的转换过程相对应。其他所有时间内部逻辑状态为“0”

本章中的符号用来确定内部连接处与内部逻辑状态之间的关系。内部连接是指逻辑元件内部的连接。为了表示框组合在一起的元件之间的逻辑关系,用符号来表示此种连接是很有用的。在多数应用中,采用本条中的符号表示复杂元件的功能也是方便的。在此种情况下,应该使用关联标记来确定内部输入(输出)的作用。7

12-08-01

12-08-02

12-08-03

12-08-04

12-08-05

12-08-06

9框内符号

-般规则

GB/T4728.12—1996

内部连接

右边元件输入端的内部“1\状态(\0”状态)与左边元件输出端的内部“1”状态(“0”状态)相对应

注:如果不会引起混乱,此符号可以省略(见1.2)。有逻辑非的内部连接

右边元件输入端的内部“1”状态(“0”状态)与左边元件输出端的内部“0”状态(“1”状态)相对应

注:垂直线可延伸穿过小圆。

有动态特性的内部连接

右边元件输入端的内部“1”状态(暂态)与左边元件输出端从内部“0”状态到\1”状态的转换过程相对应。其他所有时间,右边元件输入端的内部状态为“0”

有逻辑非和动态特性的内部连接右边元件输入端的内部“1”状态(暂态)与左边元件输出端从内部“1”状态到“0”状态转换过程相对应其他所有时间,右边元件输入端的内部逻辑状态为“0”

内部输入(虚拟输入)

如果该输入不受占优势的或修正作用的关联关系的影响,它总是处于其内部“1”状态注

、内部输入和输出仅存在内部逻辑状态。2

除符号12-07-07外,第7章的符号不应用于内部输入和输出。

内部输出(虚拟输出)

内部输出对与之相连的内部输入的影响必须用关联标记注明

符号12-08-05的注亦适用

9.1若两个或两个以上的输入有相同的功能限定符号,则它们被认为处于“或”关系,但双向门槛输入和扩展输入(见符号12-09-02和12-09-09)除外,此时它们之间的关系应适当表明。9.2符号12-09-13至12-09-22都不是动态输入。因为由外部逻辑状态或电平决定的内部逻辑状态可能受其他输入(例如Cm输入)的影响而变更。如果由符号12-09-13至12-09-22表示的输入具有动态特性,则应附加12-07-07的符号,例如符号12-47-01。8

12-09-01

GB/T4728.12—1996

延迟输出

该输出内部逻辑状态的改变延迟到引发它改变的输入信号返回到它的起始外部逻辑状态或逻辑电平时才开始。在该引发输入处于其内部“1”状态期间,任何影响输入或受引发输入影响的任何输入的内部逻辑状态必须无变化,否则,最后该输出得到的输出状态不由此符号决定。如果引发改变的输入信号出现在内部连接处,则状态的改变延迟到前面元件的输出返回到其起始内部逻辑状态才开始

如果该符号无前缀,则应认为输出相对于每一个、、十、一、和T输入以及每一个Cm输入或Cm输出延迟(见12-18-01和12-18-02);在所有其他情况下,相对于延迟输出的所有输入或输出的标识序号(或者需要时为全标记)将作为该符号的前缀示出,见符号12-49-01。为了避免与其他符号相混,符号应为两臂等长的直角。

有关该符号的应用和补充说明见第41章。概念图解

若无其他起主要作用的输入,当输入发生下述变化时,输出就发生转换。在采用逻辑非符号的图上:

以外部\1\状态到外部\0\状态以外部“0\状态到外部“1\状态在采用极性指示符号的图上:

从“H\电平到“1,”电平

队\\电乎到\I\电平

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。

本标准是根据国际电工委员会IEC617-12:1991《电气简图用图形符号第12部分:二进制逻辑元件》对GB4728.12—85进行修订的,其技术内容和编辑格式均与IEC617-12:1991等同。本标准中出现的EC117-15《推荐性图形符号第15部分:二进制逻辑元件》是IEC617-12的前身。

本标准与GB4728.12—85比较,主要差异如下:GB4728.12—85共5章122条,包含54个图例,33个概念图解;本标准共六篇132条,包含127个图例,48个概念图解。主要增加了第六篇“复杂功能单元”及其相应的图例和概念图解。

通过本标准的修订,更好地统一了二进制逻辑元件图形符号的绘制规则,以适应国际和国内贸易、技术和经济交流的需要。

GB4728《电气图用图形符号》国家标准包括以下13个部分:5总则

GB 4728.1—85

GB4728.2—84

GB 4728.3—84

符号要素、限定符号和常用的其他符号导线和连接器件

GB4728.4—85

无源元件

GB4728.5—85

GB 4728.6—84

GB 4728.7—84

GB4728.8—84

GB 4728.9—85

半导体管和电子管

电能的发生和转换

开关、控制和保护装置

测量仪表、灯和信号器件

电信:交换和外围设备

GB4728.10—85电信:传输

GB4728.11-85电力、照明和电信布置GB/T4728.12—1996二进制逻辑元件GB/T4728.13—1996模拟元件

本标准从1997年7月1日起实施,同时代替GB4728.12—85。本标准的附录A和附录B是提示的附录。本标准由中华人民共和国电子工业部提出。本标准由全国电气图形符号标准化技术委员会归口。本标准起草单位:华北计算技术研究所、电子工业部标准化研究所、航天工业总公司二院、北京广播器材厂、北京东光电工厂。

本标准主要起草人:常振启、李善贞、李占先、胡仁洋、孙人杰、张春婷。I

GB/T4728.12—1996

IEC前言

1)正C关于技术问题的正式决定或协议,尽可能地表达了所讨论问题在国际上的一致意见。起草文件的技术委员会代表了关心这些技术问题的所有国家委员会。2)这些决定和协议以推荐标准的形式供国际上使用,并在这种意义上为各国家委员会所接受。3)为了促进国际统一,IEC希望各国家委员会,只要国家条件允许,应尽量采用IEC的推荐标准作为它们的国家标准。IEC推荐标准和相应国家标准之间的任何分歧,应尽可能地在相应国家标准中说明。

GB/T4728.12—1996

本国际标准是由IEC第三技术委员会《文件和图形符号》的3A分委员会《简图用图形符号》的第二工作组编制的。

本版是IEC617-12的第二版,用以代替1983年发布的第一版。本标准的内容是以下列文件为依据(除IEC617-12第一版外):六月法则

3A(CO)155

3A(CO)156

3A(CO)157

3A(CO)158

3A(CO)161

3A(CO)162

3A(CO)175

3A(CO)182

3A(CO)855

3A(CO)186

3A(CO)188

投票报告

3A(CO)163

3A(CO)164

3A(CO)165

3A(CO)166

3A(CO)173

3A(CO)174

3A(CO)183

3A(CO)195

3A(CO)192

3A(CO)193

3A(CO)194

批准本标准的有关投票的全部信息可在上表列出的投票报告中找到。本标准引用了下列EC出版物:

EC1082-1(1991)电气技术文件的编制第一部分:一般规则简图用图形符号第3部分:导线和连接器件IEC617-3(1983)

IEC617-13(1993)

简图用图形符号第13部分:模拟元件V

1引言

中华人民共和国国家标准

电气简图用图形符号

第12部分:二进制逻辑元件

Graphical symbolsforelectrical diagramsPart 12:Binary logic elements第一篇 总

GB/T4728.12—1996

idtIEC617-12:1991

代替GB4728.12—85

本标准规定了用来表示逻辑功能的图形符号。这些图形符号也可用来表示能执行这些逻辑功能的物理器件。符号的设计着眼于电的应用,但其大多数也可用于非电气领域,例如气动的、液压的和机械的。

2一般说明

2.1对于符号IEC117-15《推荐的图形符号第15部分:二进制逻辑元件》的符号,要求延长过渡期,但应逐步地用本标准规定的符号代替。使用一些国家标准公认的其他符号,例如形状特别的那些符号来代替12-27-01、12-27-02、12-27-09、12-27-10、12-27-11,12-27-12、12-28-01、12-28-02和12-28-04,虽然不推荐,也不应视为与本标准相抵触。但是不允许用来组合复杂符号(例如用作镶嵌符号)。2.2有关“逻辑状态”“逻辑电平”的解释,见IEC1082-2《电气技术用文件的编制功能性简图》。2.3本标准采用符号\0”和“1”来表示二进制变量的两种逻辑状态。这两种状态称之为\0”状态和“1”状态。

2.4一个二进制变量可以用任何一种有两个不同值域的物理量来表示。在本标准中,这两个值域的物理量为逻辑电平,并分别以H和L表示。H用来表示具有正得较多的代数值的逻辑电平,L用来表示具有正得较少的代数值的逻辑电平。2.5如果一个系统的逻辑状态用物理量的其他特性(例如:正脉冲和负脉冲、有脉冲和无脉冲)来表示,仍可以用H和L来表示这些特性,或者用更适当的符号代替。3术语解释

3.1内部逻辑状态internallogicstates指的是在符号框内输入端或输出端设想存在的逻辑状态。3.2外部逻辑状态externallogicstates指的是在符号框外设想存在的逻辑状态:一对输入端,是指输入线上任何外部限定符号之前的逻辑状态;一对输出端,是指输出线上任何外部限定符号之后的逻辑状态。采用说明:

1JIEC1082-2代替IEC113-7。

国家技术监督局1996-12-17批准1997-07-01实施

3.3逻辑电平logiclevel

GB/T4728.12—1996

指的是设想用来代表二进制变量的物理量(见2.3和2.4)。概念图解

内部退悍优芯

外部逐期达态

外卵遥辑状路

第二篇

4符号的组成

符号结构

4.1符号由一个框或几个框组合和一个或多个限定符号所组成。使用符号时要补加输入线和输出线,制

总样讨的最佳位者

指人线

摘出裁

总限过待母的样类位置

1单个星号(*)表示与输入和输出有关的限定符号的放置位置。2当且仅当元件的功能完全由与输入和输出有关的限定符号决定时,才不需要总限定符号。4.2一般附加信息可按IEC1082-11的规定注在符号框内。4.3与特定输入(输出)有关而在标准中未标准化的信息,可以标在框内相应的输入(输出)的方括号内,并置于该输入(输出)的限定符号之后(前),如符号12-28-14所示。与元件总逻辑功能有关的附加信息,可以标在框内的方括号内。4.4由不可再分的一个符号所表示的元件,在符号内若无其他相关的限定符号或标记,则其所有输出总是存在相同的由该元件功能所决定的内部逻辑状态。可再分符号的基本元件框和限定符号,无论是详细表示的还是按本标准第6.3条的简化规则隐含表示的,其基本元件框的所有输出,总是存在相同的由基本元件框功能所决定的内部逻辑状态。4.5在有的图中,把一些不是符号组成部分的小写字母标在框外,目的仅仅是为了说明该符号时便于区分其多个输入和输出。

5.1框的长宽比是任意的。

5.2框的组合见第6章。

采用说明:

1JIEC1082-1代替IEC113-7。

12-05-01

12-05-02

12-05-03

6框的应用和组合

GB/T4728.12—1996

图形符号

元件框(示出正方形)

公共控制框

公共输出元件框

6.1为了缩小表示一组相邻元件所需的幅面,各元件的框可遵循下述规则邻接或镶嵌。6.1.1当各元件框公共线沿着信息流方向时,这些元件框之间无逻辑连接。概念图解

注:此规则不一定适用于有两种或两种以上信息流方向的那些阵列,例如,由公共控制框、公共输出元件框或由关联标记指明多种信息流方向的阵列。6.1.2如果两框的公共线垂直于信息流方向,则它们之间至少有一种逻辑连接。由于公共控制框不是逻辑元件框,因此,到公共控制框去的或从公共控制框来的连接线,都不存在逻辑连接,但与阵列相连并详细示出连接关系的除外。每一种逻辑连接可以由标注在公共线一侧或两侧的限定符号表示。如果这种方法会引起逻辑连接数目混乱时,则可使用内部连接符号(符号12-08-01)。如果在公共线的两侧均无限定符号,则可认为元件框间仅存在一种逻辑连接。概念图解

每一个星号表示一个限定符号的位置。6.2公共控制框可以与相关元件阵列连接。与阵列的一个以上元件有关的输入或输出,或者与阵列元件无关的输入或输出均可画在公共控制框上。这类输入和输出应加注(如果有)适当的标记。6.2.1如果示于公共控制框的输入是关联标记中的影响输入(见第11和12章),则它仅仅是阵列中标有该输入标识序号的各个元件所共有的输入。如果示于公共控制框的输入不是关联标记中的影响输入,3

GB/T4728.12—1996

则它是阵列所有元件共有的或对所有元件起作用的输入。公共控制框画在相关元件阵列的一端,除非另有说明,与公共控制框相邻接的元件是阵列中最低位的元件。

概念图解

6.2.2与阵列中全部元件有关的公共输出,可以示作公共输出元件的输出。在阵列元件有一个以上输出的情况下,只有当这些输出始终具有相同的内部逻辑状态时,才可以采用公共输出元件。采用公共输出元件意味着从阵列的每一个元件到公共输出元件有内部连接,但不必示出。此外,公共输出元件可以有其他的输入,这些输入必须详细示出。公共输出元件的功能应该标明。与阵列输出对应的公共输出元件的每一个输入具有与该输出相同的内部逻辑状态。公共输出元件框示于:

公共控制框内,或

一阵列的末端,如有公共控制框时,则在其相对的位置。对于一个阵列适于有多个公共输出元件框的场合,只需在一处画双线。概念图解

公共输出元

件框在公共

控制握内的

有两个公共

输山元件拒

的阵列

GB/T4728.12—1996

6.3对于由若干个具有相同限定符号的元件框构成的阵列,只要不会引起混乱,绘图时只在第一个框内标出限定符号即可。同样,当构成阵列的每个元件框又由几个相同的子阵列组成时,只详细画出第个子阵列,其余的用简单的框表示即可。即使在阵列的每个元件框中,关联标记的影响输入(输出)与受影响输入(输出)的标识序号不同,也可以进行简化(概念图解见第14章)。概念图解

其有相同总限定等导的元件阵

两个郭接的元件阵列wwW.bzxz.Net

两个交铝组合的元件阵列

无公共控制框的具有相同的与

输人和翰出有关的限定符号的

元件降阵

有公共控制握的具有相同的与

输人利输出有关的限定符号的

元件阵列

6.4在简化表示的由若于相同元件框组成的阵列中,若一个引出端的功能需要用两条或两条以上的引出线在框外连接在一起表示时,则需要在第个元件框详细示出,其余元件框可以简化,用单线表示。属于连接在一起的所有引出线共有的框外符号,应示于单线上,而非共有的符号可省略或示出。5

第三篇

GB/T4728.12—1996

概念图解

与输入、输出和其他连接有关的限定符号7逻辑非、逻辑极性和动态输入

本章中的每一个符号用来确定内部逻辑状态和外部逻辑状态或逻辑电平之间的关系。若在输入或输出端无本章的符号,则认为:在采用逻辑非符号的图上,内部逻辑“1”状态与外部逻辑“1”状态相对应;在采用逻辑极性符号的图上,内部逻辑“1”状态与逻辑\H”电平相对应。在采用逻辑极性符号的图上,不存在外部逻辑状态。逻辑非和逻辑极性符号不应在同一图上一起使用,但在采用逻辑极性符号的图上可能出现逻辑非作为内部连接的情况除外,见符号12-08-02和12-08-04。6

12-07-01

12-07-02

12-07-03

12-07-04

12-07-05

12-07-06

12-07-07

12-07-08

12-07-09

8内部连接

GB/T4728.12—1996

逻辑非,示于输入端

逻辑非,示于输出端

内部“1”状态与外部“0”状态对应注:连接线可延伸穿过小圆。

逻辑极性指示符,示于输入端

逻辑极性指示符,示于输出端

逻辑极性指示符,示于从右至左的信息流输入端

逻辑极性指示符,示于从右至左的信息流的输出端

内部“1”状态与连接线上的“L”电平相对应动态输入

内部“1”状态(暂态)与从外部“0”状态转换到外部“1”状态的过程相对应。其他所有时间逻辑状态为“0\

在采用逻辑极性符号的图上,内部“1”状态(暂态)与连线上从“L”电平到“H”电平的转换过程相对应。其他所有时间内部逻辑状态为“0\

有逻辑非的动态输入

内部逻辑“1”状态(暂态)与从外部“1”状态到外部\0”状态的转换过程相对应。其他所有时间内部逻辑状态为“0\

有极性指示符的动态输入

内部“1”状态(暂态)与连线上从“H”电平到“L”电平的转换过程相对应。其他所有时间内部逻辑状态为“0”

本章中的符号用来确定内部连接处与内部逻辑状态之间的关系。内部连接是指逻辑元件内部的连接。为了表示框组合在一起的元件之间的逻辑关系,用符号来表示此种连接是很有用的。在多数应用中,采用本条中的符号表示复杂元件的功能也是方便的。在此种情况下,应该使用关联标记来确定内部输入(输出)的作用。7

12-08-01

12-08-02

12-08-03

12-08-04

12-08-05

12-08-06

9框内符号

-般规则

GB/T4728.12—1996

内部连接

右边元件输入端的内部“1\状态(\0”状态)与左边元件输出端的内部“1”状态(“0”状态)相对应

注:如果不会引起混乱,此符号可以省略(见1.2)。有逻辑非的内部连接

右边元件输入端的内部“1”状态(“0”状态)与左边元件输出端的内部“0”状态(“1”状态)相对应

注:垂直线可延伸穿过小圆。

有动态特性的内部连接

右边元件输入端的内部“1”状态(暂态)与左边元件输出端从内部“0”状态到\1”状态的转换过程相对应。其他所有时间,右边元件输入端的内部状态为“0”

有逻辑非和动态特性的内部连接右边元件输入端的内部“1”状态(暂态)与左边元件输出端从内部“1”状态到“0”状态转换过程相对应其他所有时间,右边元件输入端的内部逻辑状态为“0”

内部输入(虚拟输入)

如果该输入不受占优势的或修正作用的关联关系的影响,它总是处于其内部“1”状态注

、内部输入和输出仅存在内部逻辑状态。2

除符号12-07-07外,第7章的符号不应用于内部输入和输出。

内部输出(虚拟输出)

内部输出对与之相连的内部输入的影响必须用关联标记注明

符号12-08-05的注亦适用

9.1若两个或两个以上的输入有相同的功能限定符号,则它们被认为处于“或”关系,但双向门槛输入和扩展输入(见符号12-09-02和12-09-09)除外,此时它们之间的关系应适当表明。9.2符号12-09-13至12-09-22都不是动态输入。因为由外部逻辑状态或电平决定的内部逻辑状态可能受其他输入(例如Cm输入)的影响而变更。如果由符号12-09-13至12-09-22表示的输入具有动态特性,则应附加12-07-07的符号,例如符号12-47-01。8

12-09-01

GB/T4728.12—1996

延迟输出

该输出内部逻辑状态的改变延迟到引发它改变的输入信号返回到它的起始外部逻辑状态或逻辑电平时才开始。在该引发输入处于其内部“1”状态期间,任何影响输入或受引发输入影响的任何输入的内部逻辑状态必须无变化,否则,最后该输出得到的输出状态不由此符号决定。如果引发改变的输入信号出现在内部连接处,则状态的改变延迟到前面元件的输出返回到其起始内部逻辑状态才开始

如果该符号无前缀,则应认为输出相对于每一个、、十、一、和T输入以及每一个Cm输入或Cm输出延迟(见12-18-01和12-18-02);在所有其他情况下,相对于延迟输出的所有输入或输出的标识序号(或者需要时为全标记)将作为该符号的前缀示出,见符号12-49-01。为了避免与其他符号相混,符号应为两臂等长的直角。

有关该符号的应用和补充说明见第41章。概念图解

若无其他起主要作用的输入,当输入发生下述变化时,输出就发生转换。在采用逻辑非符号的图上:

以外部\1\状态到外部\0\状态以外部“0\状态到外部“1\状态在采用极性指示符号的图上:

从“H\电平到“1,”电平

队\\电乎到\I\电平

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。